блоки управления, четвертый блок памяти, четвертый блок сравнения, блок регистров и второй блок усилителей, первьм и второй входы которого соединены соответственно с первым и вторым выходами второго блока управления, третий выход которого соединен с первьм входом третьего блока управления, выход которого соединен с первым входом блока регистров, первьш.и второй выходы которого соединены соответственно с третьим и четвертым входами второго блока усилителей, первый выход которого соединен с первым входом второго блока управления, второй вход которого соединен с первым выходом четвертого блока памяти, второй выход которого соединен с первым входом четвертого блока сравнения, второй вход которого соединен с первым входом четвертого блока управления, с вторым входом блока регистров и с вторым выходом второго блока усилителей третий выход которого соединен с вторым входом четвертого блока управления, третий вход и выход которого соединены соответственно с третьим выходом и входом четвертого блока памяти, четвертый выход которогосоединен с третьим входом блока регистров, четвертый вход которого соединен с четвертым выходом второго блока усилителей, пятый вход и пятый выход которого соединен соответственно с пятым выходом и третьим входом первого блока усилителей, четвертый выход второго блока управления соединен с четвертым входом четвертого блока управления, пятьй вход которого соединен с выходом четвертого блока сравнения, пятый выход четвертого блока памяти соединен с вторым входом третьего блока упраеления, шестой вход и шестой .выход второго блока усилителей являются соответственно входом и выходом устройства.

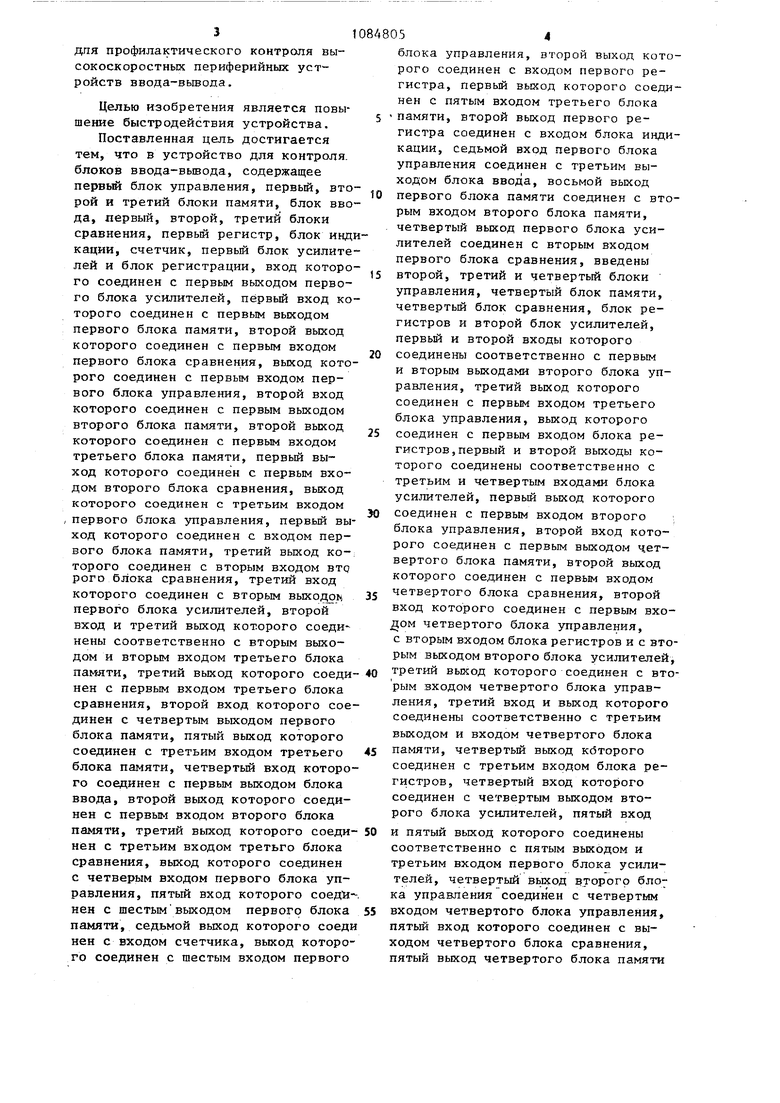

2. Устройство по 1, отличающееся тем, что второй блок

управления содержит элемент ИЛИ-НЕ, первьй и второй триггеры и формирователи импульсов, выходы которых сое

динены с входами элемента ИЛИ-НЕ, входы формирователей импульсов являются первым входом блока, входы первого и второго триггеров являются вторым входом блока, выходы перВС)ГО Т второго триггеров ЯВЛЯК11СЯ

первь(м и вторым выходами блока, выход одного из формирователей импульсов является третьим выходом блока, выход элемента ИЛИ-НЕ является четвертым выходом блока.

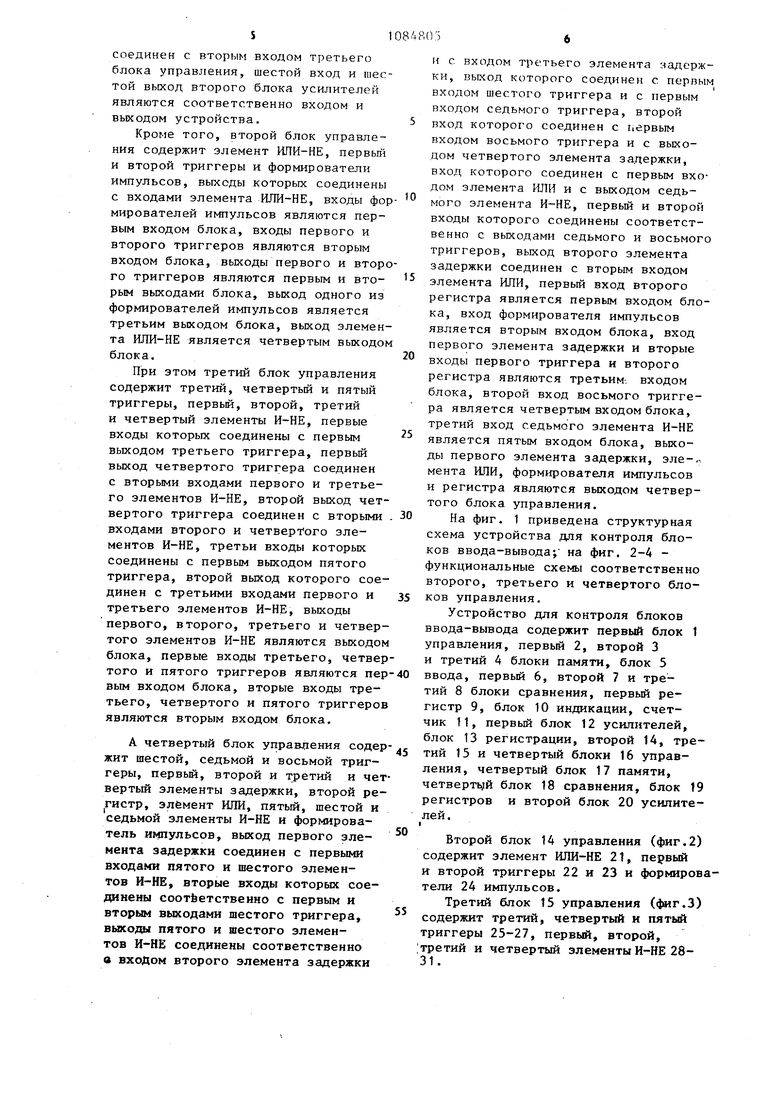

3. Устройство по п, 1, о т л ичающе ее я тем, что третий блок управления содержит третий, четвертый и пятый триггеры, первый, второй, третий и четвертый элементы И-НЕ, первые входы которых соединены с первьм выходом третьего триггера, первый выход четвертого триггера соединен с вторыми входами первого и третьего элементов И-НЕ, второй выход четвертого триггера соединен с вторыми входами второго и четвертого элементов И-НЕ, третьи входы которых соединены с первым выходом пятого триггера, второй выход которого соединен с третьими входами первого и третьего элементов И-НЕ выходы первого, второго, третьего и четвертого элементов И-НЕ являются выходом блока, первые входы третьего четвертого и пятого триггеров являются первым входом блока, вторые входы третьего, четвертого и пятого триггеров являются вторым входом блока.

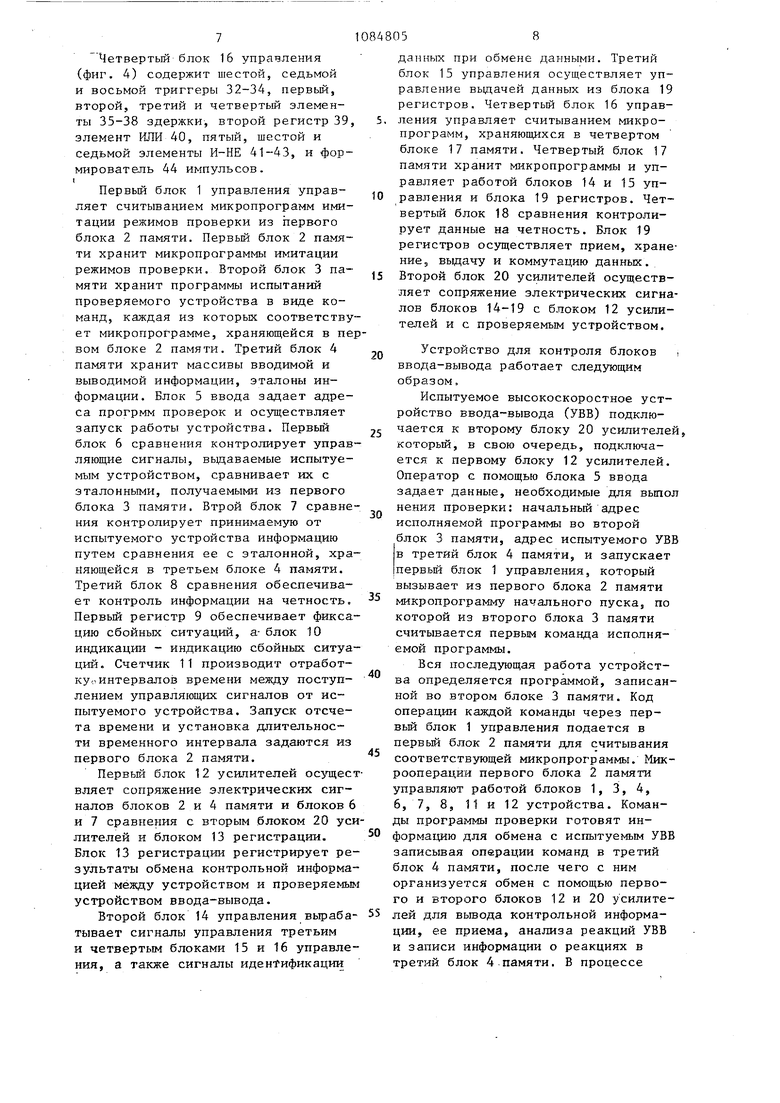

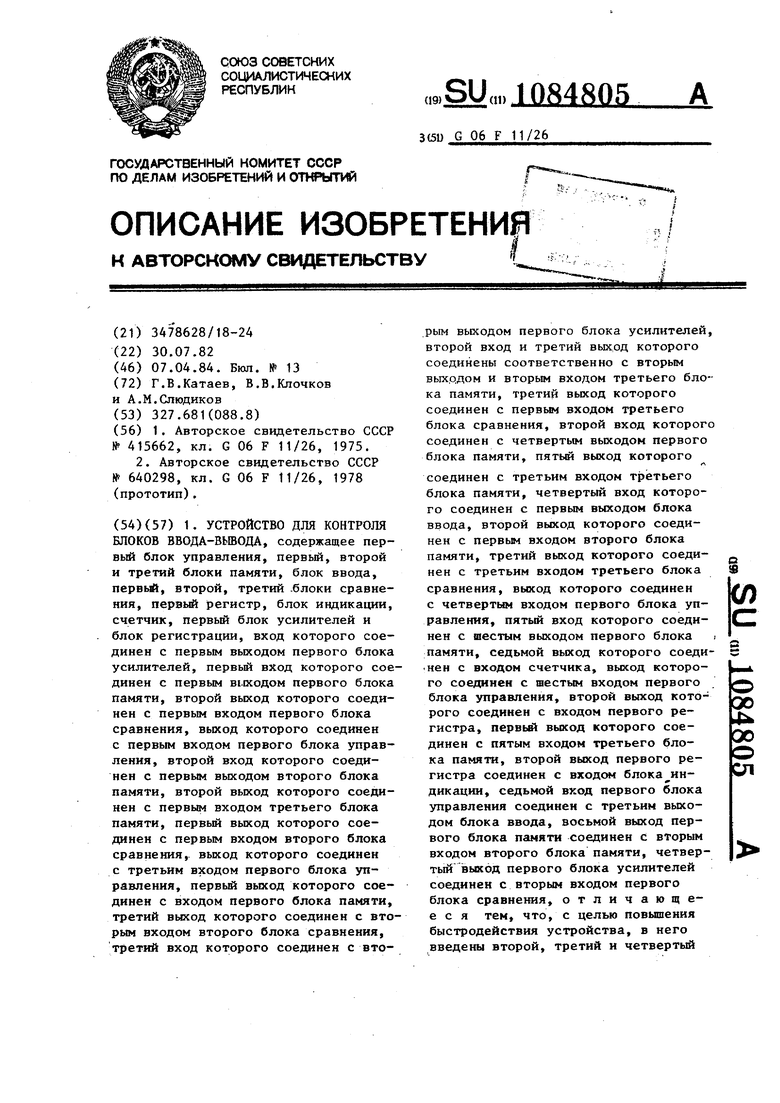

4. Устройство -ПО п. 1, о т л ичающееся тем, что четвертый блок управления содержит шестой, седьмой и восьмой триггеры, первый, второй, третий и четвертый элементы задержки, второй регистр, элемент ИЛИ, пятый, шестой и седьмой элементы И-НЕ и формирователь импульсов, выход первого элемента задержки соединен с первыми входами пятого и шестого элементов И-НЕ, вторые входы которых соединены соответственно с первым и вторым выходами шестого триггера, выходы пятого и шестого элементов И-НЕ соединены соответственно с входом второго элемента задержки и с входом третьего элемента задержки, выход которого соединен с п ервым входом шестого триггера и с первым входом седьмого триггера, второй вход которого соединен с первым входом восьмого триггера и с выходом четвертого элемента задержки, вход которого соединен с первым входом элемента ИЛИ и с выходом седьмого элемента И-НЕ, первый второй входы которого соединень

соответственно с выходами седьмого и восьмого триггеров, выход второго элемента задержки соединен с вторым входом элемента ИЛИ, первый вход второго регистра является первым входом блока, вход формирователя импульсов является вторым входом блока, вход первого элемента задержки и вторые входы первого триггера

и второго регистра являются третьим входом блока, второй вход восьмого триггера является четвертым входом блока, третий вход седьмого элемента И-НЕ является пятым входом блока, выходы первого элемента задержки, элемента ИЛИ, формирователя импульсов и регистра являются выходом четвертого блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1982 |

|

SU1020825A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Устройство для контроля | 1981 |

|

SU1072052A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1166110A1 |

| Устройство для определения составляющих вектора скорости движения изображения | 1983 |

|

SU1233190A1 |

| Пульт преподавателя для обучающих устройств | 1984 |

|

SU1166163A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

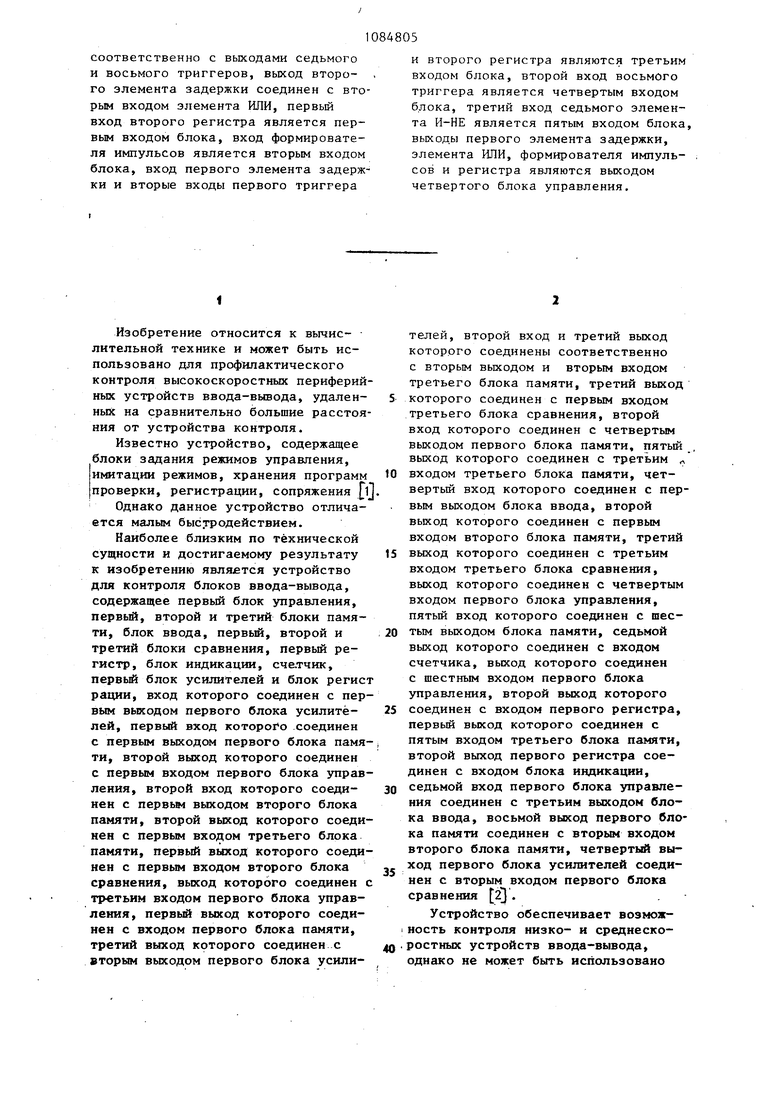

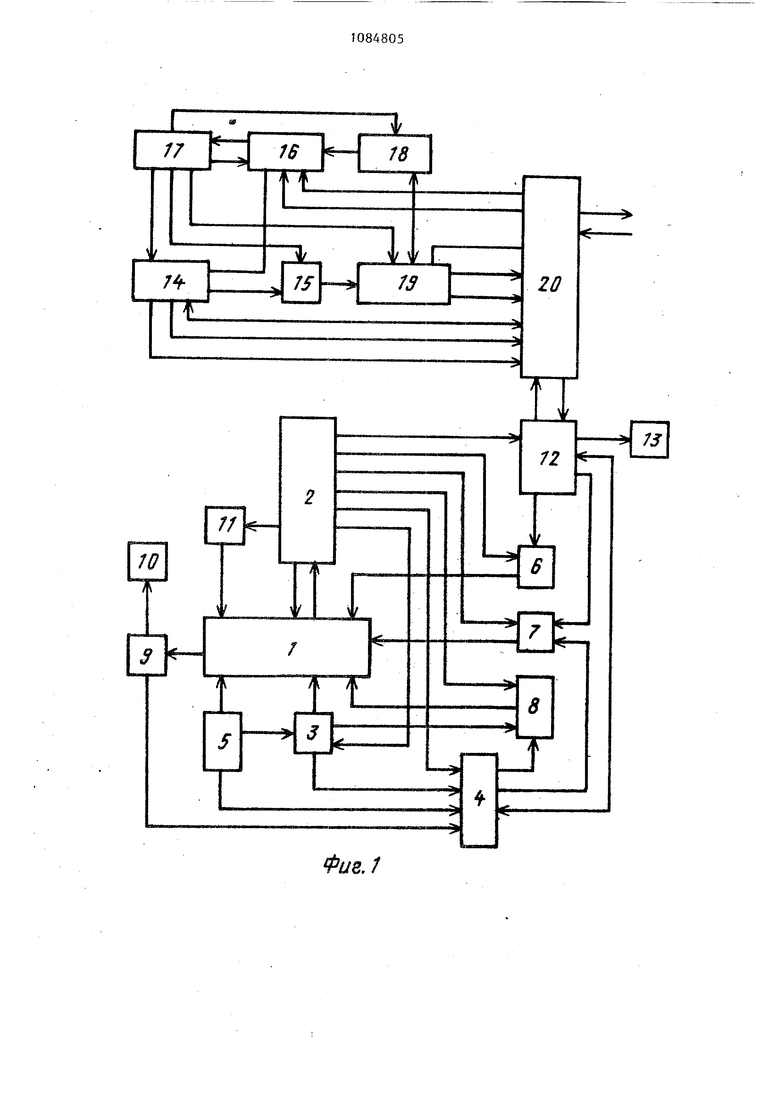

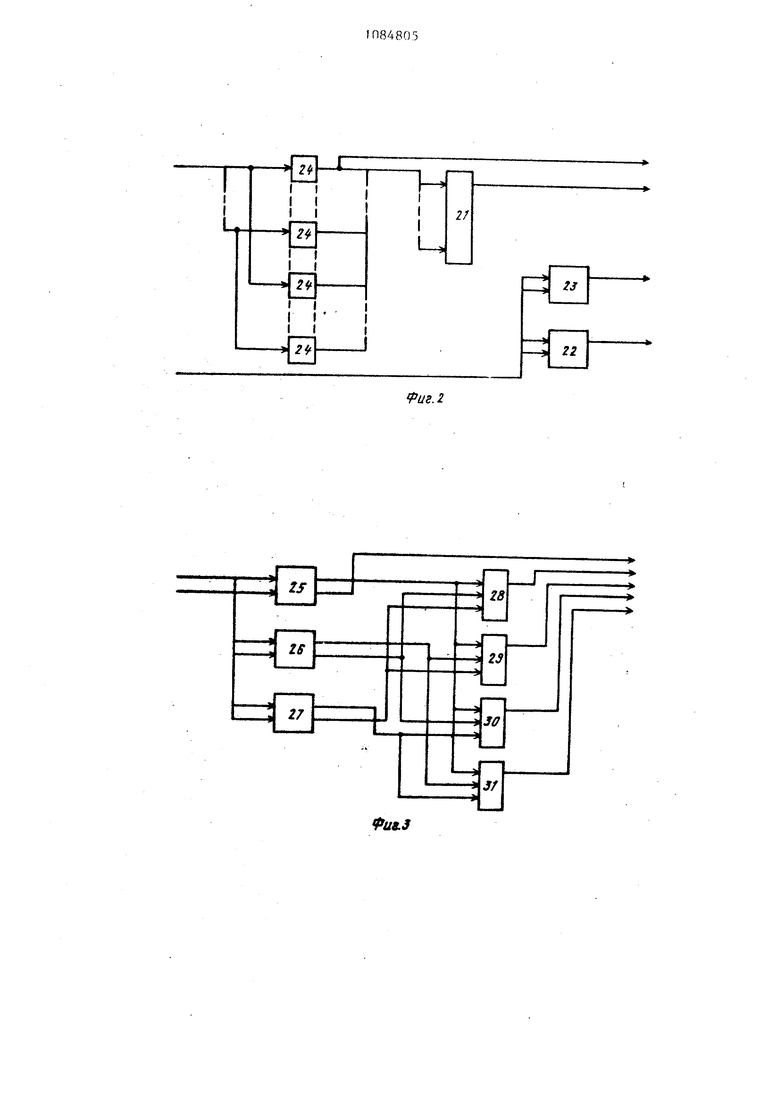

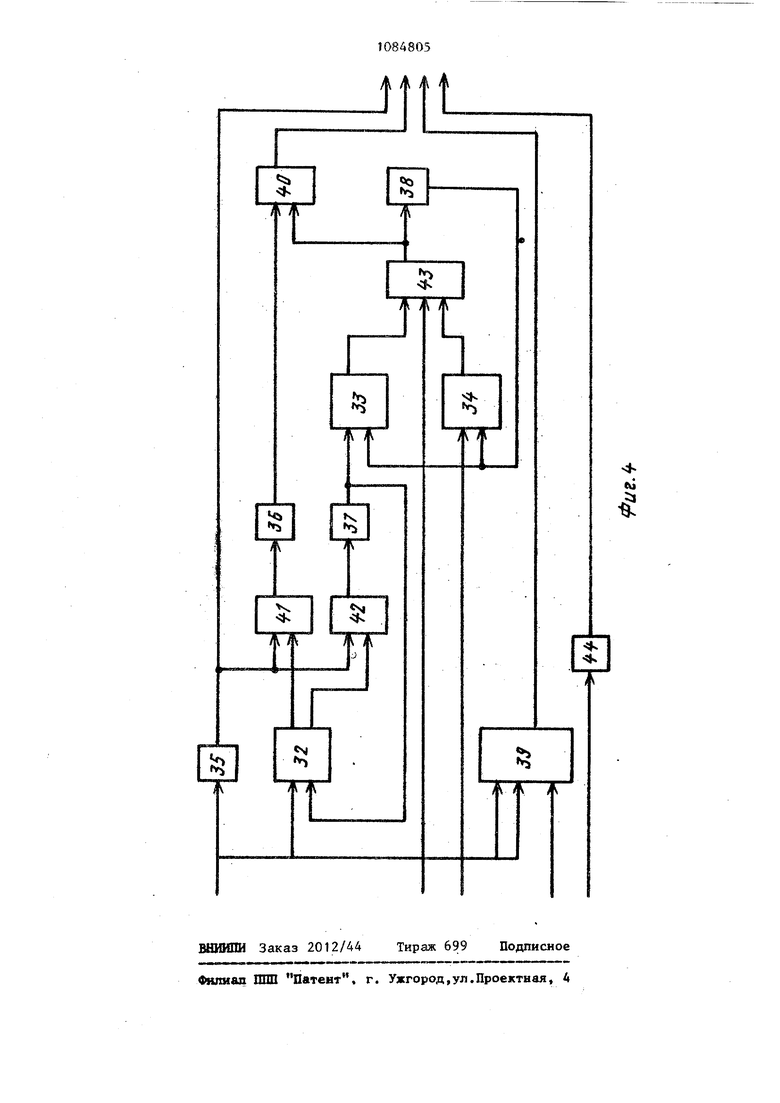

Изобретение относится к вычислительной технике и может быть использовано для профилактического контроля высокоскоростных периферий ных устройств ввода-вывода, удаленных на сравнительно большие расстоя ния от устройства контроля. Известно устройство, содержащее блоки задания режимов управления, имитации режимов, хранения программ проверки, регистрации, сопряжения Однако данное устройство отличается малым быстродействием. Наиболее близким по технической сущности и достигаемому результату к изобретению являатся устройство для контроля блоков ввода-вывода, содержащее первый блок управления, первый, второй и третий блоки памяти, блок ввода, первый, второй и третий блоки сравнения, первый регистр, блок индикации, сче.тчик, первый блок усилителей и блок регис рации, вход которого соединен с пер вым выходом первого блока усилителей, первый вход которого .соединен с первым выходом первого блока памя ти, второй выход которого соединен с первым входом первого блока управ ления, второй вход которого соединен с первьн выходом второго блока памяти, второй выход которого соеди нен с первым входом третьего блока памяти, первый выход которого соеди нен с первым входом второго блока сравнения, выход которого соединен третьим входом первого блока управления, первый выход которого соединен с входом первого блока памяти, третий выход которого соединен с вторым выходом первого блока усилителей, второй вход и третий выход которого соединены соответственно с вторым выходом и вторым входом третьего блока памяти, третий выход которого соединен с перВЕлм входом третьего блока сравнения, второй вход которого соединен с четвертым выходом первого блока памяти, пятый выход которого соединен с третьим ,, входом третьего блока памяти, четвертый вход которого соединен с первым выходом блока ввода, второй выход которого соединен с первым входом второго блока памяти, третий выход которого соединен с третьим входом третьего блока сравнения, выход которого соединен с четвертым входом первого блока управления, пятьш вход которого соединен с шестым выходом блока памяти, седьмой выход которого соединен с входом счетчика, выход которого соединен с шестным входом первого блока управления, второй выход которого соединен с входом первого регистра, первый выход которого соединен с пятым входом третьего блока памяти, второй выход первого регистра соединен с входом блока индикации, седьмой вход первого блока управления соединен с третьим выходом блока ввода, восьмой вькод первого блока памяти соединен с вторым входом второго блока памяти, четвертый выход первого блока усилителей соединен с вторым входом первого блока сравнения 2} .. Устройство обеспечивает возможность контроля низко- и среднескоростных устройств ввода-вывода, однако не может быть использовано для профилактического контроля высокоскоростньк периферийных устройств ввода-вьшода, Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для контроля, блоков ввода-вьшода, содержащее первый блок управления, первый, вто рой и третий блоки памяти, блок вво да, первый, второй, третий блоки сравнения, первьм регистр, блок инд кации, счетчик, первьш блок усилите лей и блок регистрации, вход которо го соединен с первым выходом первого блока усилителей, пёрвьй вход ко торого соединен с первым выходом первого блока памяти, второй выход которого соединен с первым входом первого блока сравнения, выход кото рого соединен с первым входом первого блока управления, второй вход которого соединен с первым выходом второго блока памяти, второй выход которого соединен с первым входом третьего блока памяти, первый выход которого соединен с первым входом второго блока сравнения, выход которого соединен с третьим входом первого блока управления, первый вы ход которого соединен с входом первого блока памяти, третий выход которого соединен с вторым входом BTQ рого блока сравнения, третий вход которого соединен с вторым выход г первого блока усилителей, второй вход и третий выход которого соеди нены соответственно с вторым выходом и вторым входом третьего блока памяти, третий выход которого соеди нен с первым входом третьего блока сравнения, второй вход которого сое динен с четвертым выходом первого блока памяти, пятый выход которого соединен с третьим входом третьего блока памяти, четвертый вход которо го соединен с первым выходом блока ввода, второй выход которого соединен с первым входом второго блока памяти, третий выход которого соеди ней с третьим входом третьго блока сравнения, выход которого соединен с четверым входом первого блока управления, пятый вход которого соедй нен с шестымвыходам первого блока памяти, седьмой выход которого соед нен с входом счетчика, выход которо го соединен с шестым входом первого 54 блока управления, второй выход которого соединен с входом первого регистра, первый выход которого соединен с пятым входом третьего блока памяти, второй выход первого регистра соединен с входом блока индикации, седьмой вход первого блока управления соединен с третьим выходом блока ввода, восьмой выход первого блока памяти соединен с вторым входом второго блока памяти, четвертый выход первого блока усилителей соединен с вторым входом первого блока сравнения, введены второй, третий и четвертый блоки управления, четвертый блок памяти, четвертый блок сравнения, блок регистров и второй блок усилителей, первый и второй входы которого соединены соответственно с первым и вторым выходаш второго блока управления, третий выход которого соединен с первым входом третьего блока управления, выход которого соединен с первым входом блока регистров, первый и второй выходы которого соединены соответственно с третьим и четвертым входами блока усилителей, первьш выход которого соединен с первым входом второго блока управления, второй вход которого соединен с первым выходом четвертого блока памяти, второй выход которого соединен с первым входом четвертого блока сравнения, второй вход которого соединен с первым вхоом четвертого блока управления, с вторым входом блока регистров и с вторым выходом второго блока усилителей, третий выход которого соединен с вторым входом четвертого блока управления, третий вход и выход которого соединены соответственно с третьим выходом и входом четвертого блока памяти, четвертьй выход которого соединен с третьим входом блока регистров, четвертый вход которого соединен с четвертым выходом второго блока усилителей, пятый вход и пятый выход которого соединены соответственно с пятым выходом и третьим входом первого блока усилителей, четвертый выход второго блока управления соединен с четвертым входом четвертого блока управления, пятый вход которого соединен с выходом четвертого блока сравнения, пятый выход четвертого блока памяти соединен с вторым входом третьего блока управления, шестой вход и шес той вьсход второго блока усилителей являются соответственно входом и выходом устройства. Кроме того, второй блок управления содержит элемент ИПИ-НЕ, первый и второй триггеры и формирователи импульсов, выходы которых соединены с входами элемента ИЛИ-НЕ, входы фо мирователей импульсов являются первым входом блока, входы первого и второго триггеров являются вторым входом блока, выходы первого и втор го триггеров являются первым и вторым выходами блока, выход одного из формирователей импульсов является третьим выходом блока, выход элемен та ИЛИ-НЕ является четвертым выходо блока. При этом третий блок управления содержит третий, четвертый и пятый триггеры, первьй, второй, третий и четвертый элементы И-НЕ, первые входы которых соединены с первым выходом третьего триггера, первьй выход четвертого триггера соединен с вторыми входами первого и третьего элементов И-НЕ, второй выход чет вертого триггера соединен с вторыми входами второго и четвертого элементов И-НЕ, третьи входы которых соединены с первым выходом пятого триггера, второй выход которого сое динен с третьими входами первого и третьего элементов И-НЕ, выходы первого, второго, третьего и четвер того элементов И-НЕ являются выходо блока, первые входы третьего, четве того и пятого триггеров являются пе вым входом блока, вторые входы третьего, четвертого и пятого триггеро являются вторым входом блока. А четвертый блок управления соде жит шестой, седьмой и восьмой триггеры, первьй, второй и третий и че вертый элементы задержки, второй ре гистр, элемент ИЛИ, пятый, шестой и седьмой элементы И-НЕ и формирователь импульсов, выход первого элемента задержки соединен с первыми BXOAaNm пятого и шестого элементов И-НЕ, вторые входы которых соединены соотйетствеино с первым и вторым выходами шестого триггера, выхода пятого и шестого элементов И-НЕ соединены соответственно в входом второго элемента эадержки н с входом третьего элемента задержки, выход которого соединен с первым входом шестого триггера и с первым входом седьмого триггера, второй вход которого соединен с Ггврвым входом восьмого триггера и с выходом четвертого элемента задержки, вход которого соединен с первым входом элемента ИЛИ и с выходом седьмого элемента И-НЕ, первый и второй входы которого соединены соответственно с выходами седьмого и восьмого триггеров, выход второго элемента задержки соединен с вторым входом элемента ИЛИ, первый вход второго регистра является первым входом блока, вход формирователя импульсов является вторым входом блока, вход первого элемента задержки и вторые входы первого триггера и второго регистра являются третьим-, входом блока, второй вход восьмого триггера является четвертым входом блока, третий вход седьмого элемента И-НЕ является пятым входом блока, выходы первого элемента задержки, эле---, мента ИЛИ, формирователя импульсов и регистра являются выходом четвертого блока управления. На фиг. 1 приведена структурная схема устройства для контроля блоков ввода-вывода; на фиг, 2-4 функциональные схемы соответственно второго, третьего и четвертого блоков управления. Устройство для контроля блоков ввода-вывода содержит первый блок 1 управления, первьй 2, второй 3 и третий 4 блоки памяти, блок 5 ввода, первьй 6, второй 7 и третий 8 блоки сравнения, первый регистр 9, блок 10 индикации, счетчик 11, первьй блок 12 усилителей, блок 13 регистрации, второй 14, третий 15 и четвертый блоки 16 управления, четвертый блок 17 памяти, четверть й блок 18 сравнения, блок 19 регистров и второй блок 20 усилителей. Второй блок 14 управления (фиг.2) содержит элемент ИЛИ-НЕ 21, первый и второй триггеры 22 и 23 к формирователи 24 импульсов. Третий блок 15 управления ((.3) содержит третий, четвертый н пятый триггеры 25-27, первый, второй, третий и четвертый элементы И-НЕ 2831. Четвертый блок 16 упрачления (фиг. 4) содержит шестой, седьмой и восьмой триггеры 32-34, первьм, второй, третий и четвертый элементы 35-38 здержки, второй регистр 39, элемент ИЛИ 40, пятый, шестой и седьмой элементы И-НЕ 41-43, и формирователь 44 импульсов. I Первый блок 1 управления управляет считыванием микропрограмм имитации режимов проверки из первого блока 2 памяти. Первьм блок 2 памяти хранит микропрограммы имитации режимов проверки. Второй блок 3 памяти хранит программы испытаний проверяемого устройства в виде команд, каждая из которых соответству ет микропрограмме, храняющейся в пе вом блоке 2 памяти. Третий блок 4 памяти хранит массивы вводимой и выводимой информации, эталоны информации. Блок 5 ввода задает адреса прогрмм проверок и осуществляет запуск работы устройства. Первый блок 6 сравнения контролирует управ ляющие сигналы, вьщаваемые испытуемым устройством, сравнивает их с эталонными, получаемыми из первого блока 3 памяти. Втрой блок 7 сравне ния контролирует принимаемую от испытуемого устройства информацию путем сравнения ее с эталонной, хра няющейся в третьем блоке 4 памяти. Третий блок 8 сравнения обеспечивает контроль информации на четность. Первый регистр 9 обеспечивает фикса цию сбойных ситуаций, а- блок 10 индикации - индикацию сбойных ситуа ций. Счетчик 11 производит отработку интервалов времени между поступлением управляющих сигналов от испытуемого устройства. Запуск отсчета времени и установка длительности временного интервала задаются из первого блока 2 памяти. Первый блок 12 усилителей осущес вляет сопряжение электрических сигналов блоков 2 и 4 памяти и блоков 6 и 7 сравнения с вторым блоком 20 ус лителей и блоком 13 регистрации. Блок 13 регистрации регистрирует ре зультаты обмена контрольной информа цией между устройством и проверяемы устройством ввода-вывода. Второй блок 14 управления выраба тывает сигналы управления третьим и четвертым блоками 15 и 16 управле ния, а также сигналы идентификации данных при обмене данными. Третий блок 15 управления осуществляет управление выдачей данных из блока 19 регистров. Четвертый блок 16 управления управляет считыванием микропрограмм, храняющихся в четвертом блоке 17 памяти. Четвертый блок 17 памяти хранит микропрограммы и управляет работой блоков 14 и 15 управления и блока 19 регистров. Четвертый блок 18 сравнения контролирует данные на четность. Блок 19 регистров осуществляет прием, хранение, вьщачу и коммутацию данных. Второй блок 20 усилителей осуществляет сопряжение электрических сигналов блоков 14-19 с блоком 12 усилителей и с проверяемым устройством. Устройство для контроля блоков , ввода-вывода работает следующим обрс13ОМ, Испытуемое высокоскоростное устройство ввода-вывода (УВВ) подключается к второму блоку 20 усилителей, который, в свою очередь, подключается к первому блоку 12 усилителей. Оператор с помощью блока 5 ввода задает данные, необходимые для выпол нения проверки; начальньй адрес исполняемой программы во второй блок 3 памяти, адрес испытуемого УВВ в третий блок 4 памяти, и запускает первьй блок 1 управления, который вызывает из первого блока 2 памяти микропрограмму начального пуска, по которой из второго блока 3 памяти считывается первым команда исполняемой программы. Вся последующая работа устройства определяется программой, записанной во втором блоке 3 памяти. Код операции каждой команды через первьй блок 1 управления подается в первьй блок 2 памяти для считывания соответствующей микропрограммы. Микрооперации первого блока 2 памяти управляют работой блоков 1, 3, 4, 6, 7, 8, 11 и 12 устройства. Команды программы проверки готовят информацию для обмена с испытуемым УВВ записывая операции команд в третий блок 4 памяти, после чего с ним организуется обмен с помощью первого и второго блоков 12 и 20 усилителей для вьшода контрольной информации, ее приема, анализа реакций УВВ и записи информации о реакциях в третий блок 4 памяти. В процессе приема и записи информации осуществ ляется сравнение принимаемой и эталонной информации во втором блоке 7 сравнения, а также проверяется правильность выработки УВВ управляющих сигналов с помощью первого блока 6 сравнения, который сравнивает реаль но поступающие сигналы от УВВ и эта лонные (ожидаемые) сигналы из перво го блока 2 памяти. Для определения ошибок, прерывающих испытания, используется счетчик 11, фиксируюЕций случаи отсутствия управляющих сигна лов от УВВ в течение определённых промежутков времени. Все пересыпки информации контролируются на четность в третьем блоке 8 сравнения. Обнаруженные при проверке неисправности первым, вторым и третьим блоками 6-8 сравнения и счетчиком 11 через первьш блок 1 управления фиксируются в первом регистре 9 и индйцирзтотся на блоке 10 индикации. По каждой из зафиксированных неисправностей осуществляется останов .работы устройства, t После запуска програм№1 устройства устанавливается связь с УВВ через второй блок 20 усилителей. При этом управляющие сигналы, вырабатываеьяяе первым блоком 2 памяти, через первьй и второй блоки 12 и 20 усилителей поступают на УВВ и на второй блок 14 управления, а управляющие сигналы от УВВ через второй блок 20 усилителей поступают также на второй блок 14 управления, а через первый блок 12 усилителей - на первый блок 6 сравнения. Служебные данные из третьего блока 4 памяти через первый ,и второй блоки 12 и 20 усилителей, блок 19 регистров и блок 20 усилителей поступают на УВВ а от УВВ служебные данные через второй блок 20 усилителей, блок 19 регистров, блок 20 усилителей и первый блок 12 усилителей поступают на третий блок 4 памяти и второй блок 7 сравнения, В процессе установления связи между устройством и УВВ соответству ющим сигналом управления от УВВ через второй блок 20 усилителей, через формирователь 44 импульсов четвертого блока 16 управления запускается четвертый блок 17 памяти с начального адреса, где вырабатывает ся соответствзгощий адресу набор мик роопераций (МО), определяющий работу устройства в данный отрезок вреПоследующие обращения к четвертому блоку 17 памяти осуществляются четвертым блоком 16 управления, который работает следующим образом. В любом наборе МО по любому адресу в четвертом блоке 17 памяти вырабатывается МО, поступающая на первый элемент 35 задержки блока 16 управления, а с его выхода снова на четвертый блок 17 памяти для подготовки следующего адреса и через пятый элемент И-НЕ 41, второй элемент 36 задержки, элемент ИЛИ 40 так же на четвертый блок 17 памяти для считьшания следующего набора МО. Если микропрограммой определен переход :на ожидание ответа от УВВ или управ|ляющего сигнала от первого блока 12 усилителей, то соответствующей МО взводится шестой триггер 32 и сигнал с первого элемента 35 задержки Через пятый И-НЕ 41 не пройдет, а через шестой элемент И-НЕ 42, и третий элемент 37 задержки взведет седьмой триггер 33 и сбросит шестой триггер 32 в начальное состояние. При поступлении или снятии управляющего сигнала от УВВ или от первого блока 12 усилителей на второй блок 14 управления, на одном из соответствующей пары формирователей 24 импульсов, входы которых объединены и один из которых является формирователем переднего фронта, другой - заднего, вырабатывается сигнал, который через элемент ИЛИНЕ 21 поступает на второй.вход восьмого триггера 34 четвертого блока 16 управления и взводит его. При этом, так как триггер 33 взведен, на выходе седьмого элемента И-НЕ 43 вырабатывается сигнал, поступаюпщй через элемент ИЛИ 40 на четвертый блок 17 памяти для считывания еледующего набора МО, а через четвертый элемент 38 задержки на входы седьмого и восьмого триггеров 33 и 34 для установки их в начальное состояние. Второй регистр 39 предназначен для приема, временного хранения и передачи в четвертый блок 17 памяти адреса микропрограм1« 1, по которой будет осуществляться обмен контрольной информацией между устройством и УВВ. Адрес микропрограммы поступает на первый вход второго регистра 39 из третьего блока 4 памяти через первый и второй блоки 12 и 20 усилителей, а на вторы входы регистра поступают МО из четвертого блока 17 памяти для установки регистра в начальное состояние и управления занесением в него адреса микропрограммы.

Таким образом, четвертый блок 17 памяти отслеживает обмен управляющими сигналами между устройством и УВВ. Когда блок 17 памяти определи что на УВВ передается код команды, которую УВВ должно вьшолнять, то этот код заносится в рег.истр 39 блока 16 управления. В момент перехода к обмену контрольными данными между устройством и УВВ код команды переносится из регистра 39 блока 16 управления в блок 17 памяти и этот код является начальным адресом соответствующей микропрограммы обмена данными. В этот же момент соответствующей МО из блока 17 памяти, поступающей на второй вход третьего блока 15 управления, взводится третий триггер 25. При этом запрещающий сигнал с второго выхода триггера 25 поступает на первый вход блока 19 регистров, запрещая прохождение данных между устройством и УВВ через соответствующие коммутаторы данных блока, а разрешающий сигнал с первого выхода триггера 25 поступает на первые входы первого, второго, третьего и четвертого элементов И-НЕ 28-31, на Bbcibде одного из которых в соответствии с состоянием четвертого и пято- го триггеров 26 и 27 вырабатывается сигнал, обеспечивающий соответствующую коммутацию данных в блоке 19 регистров. Управление состоянием триггеров 26 и 27 производится соответствукщими МО из блока 17 памяти.

f

При передаче контрольных данных от устройства в УВВ очередное слово данных из блока 4 памяти записывается в один из двух регистров блока 19 регистров соответствующим сигналом, поступающим из блока 17 паяти, а с другого регистра осуществляется выдача в УВВ записанного ранее предыдущего слова данных. За время передачи очередного слова данных из блока 4 памяти в блок 19 регистров, каждое предьщущее слово из блока 19

регистров передается в УВВ N раз, так, что общее число переданных слов данных в УВВ

Р M-N, где М - количество слов, переданных

из блока 4 памяти; N - отношение быстродействия УВВ к быстродействию блоков 1-13.

Это отношение N может быть задано программно в блоке 17 памяти в зависимости от быстродействия УВВ.

При считывании из УВВ переданных ранее контрольных данных из каждых N слов в соответствующий регистр блока 19 регистров записывается одно которое затем передается в блок 4 памяти. Таким образом, за один сеанс связи с УВВ в блок 4 памяти поступит М слов данных. Все слова Р передаются за сеансы связи с УВВ, причем в каждом сеансе в блок 19 регистров заносится соответственно каждое первое, второе,.... N-e слово из группы в N слов, что задается программой устройства.

В процессе обмена контрольными данными сигнал идентификации данных от ЗГВВ через первый блок 20 усилителей, соответствукщий формирователь 2 и элемент ИЛИ-НЕ 21 блока 14 управления запускает блок 17 памяти, как было показано соответствующими МО I которого производится управление первым и вторьм триггерами 22 и 23 блока- 14 управления. При этом ответный сигнал идентификации данных с триггера 23 через второй блок 20 сопряжения поступает на УВВ, а с триггера 22 через блоки 20 и 12 усилителей - на первьй блок 6 сравнения .

В процессе передачи данных в УВВ в четвертом блоке 18 сравнения производится контроль данных на четность. В случае ошибки на выходе блока 18 сравнения вырабатьшается запрещающий сигнал, поступающий на третий вход седьмого элемента И-. НЕ 43 четвертого блока 16 управления запрещая выработку сигнала запуска четвертого блока 17 памяти (происхо дит останов работы устройства).

После оконча1}ия передачи данных соответствующий управляющий сигнал от УВВ через один из формирователей 24 импульсов второго блока 14 управления поступает на первый вход третьего триггера 25 третьего блока 15 управления и устанавливае его в начальное состояние. При это как бьшо указано, служебные данные между устройством и УВВ передаются .через блок 19 регистров (через ком мутаторы), минуя регистры. При передаче данных между устройством и быстродействующим УВВ существенное значение приобретает время распространения сигналов по кабелю меяду ними, которое ограничивает взаимную длину линии связи. Максимально допустимое время передачи единицы информации выража ется формулой лаадоо Mart где f Mpikjg максимальная скорость работы УВВ. Распределение этого времени вьфажается формулой мЯКАвП ) где tuo. t,. - время обработки сиг 1 налов идентификации данных в УВВ и устро стве соответственно; t Qg - время распространени сигналов в кабеле. Обычно 1л|дрПриблизительно равно Учитыt gg всегда меньше t.gg что этот и сделав допущение, t tM.MOKHo записать .. МОмАОП ЗЬ«™и -kois 3 Так как t 2L , Ц(др- длина кабеля; 0 - погонная задержка в кабел 2 - коэффициент, учитьгоающий, что за время обмена едини цей информации сигнал идеи-. чем в стыке 514 тификации данных распределиется от устройства в УВВ и обратно, и учитывая (1) и (3), получаем W° ,, Если, например, максимальная скорость работы УБВ равна 800 кбайт/с, а погонная задержка в кабеле 5 нс/м, то из (4) получаем --Г-- х ггто 65 -lO- -SOO-lO (м) Следовательно, при таком быстродействии УВВ расстояние между ним и устройством (даже при сделанном допущении, что Цд5 ) не должно превьппать 40 м, а реально еще меньше. Невомзожность проводить контроль быстродействующих УВВ на сравнительно больших расстояниях ограничивает возможность использования контрольной аппаратуры на объектах. Устройство позволяет значительно увеличить расстояние между ним и испытуемым высокоскоростным УВВ. Это достигается тем, что блоки 14-20 вьтолнены конструктивно отдельно от блоков 1-13 так, что легко могут при помснци блока 20 подсоединяться к испытуемому УВВ в непосредственной близости от него, а подсоединение к блоку 12 может осуществляться на значительных расстояниях, так как обмен в стыке между блоком 20 и блоком 12, как быпо указано, при описании работы устройства производится iC быстродействием известного устройства, т.е. значительно медленнее. между блоком 20 и УВВ.

Фив.1

(о

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 1972 |

|

SU415662A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для проверки устройств ввода-вывода информации | 1977 |

|

SU640298A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-04-07—Публикация

1982-07-30—Подача