нительньи управлякидим выходом ячейки памяти, а входы сброса соединены с выходами вспомогательных элементов И-НЕ ячейки памяти, причем дополнительный управляющий выход каждой ячейки памяти, кроме последней, соединен с дополнительным управляющим

входом последующей ячейки памяти, дополнительный управляющий вход пер.вой ячейки памяти является дополни.тельным управляющим входом регистра, а дополнительный управляющий выход последней ячейки памяти - дополнительным управляющим выходом регистра,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для матричных операций | 1989 |

|

SU1777154A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1501168A1 |

| Устройство для LU-разложения матриц | 1987 |

|

SU1509933A1 |

| Асинхронный регистр сдвига (его варианты) | 1982 |

|

SU1140173A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1462422A1 |

| Асинхронный регистр сдвига | 1985 |

|

SU1251182A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2011 |

|

RU2450447C1 |

| Регистр | 1980 |

|

SU928418A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1789975A1 |

РЕГИСТР СДВИГА, содержащий ячейки памяти, каждая из которых состоит из RS-триггера на двух элементах И-НЕ, первые входы которых являются управляющим входом данного триггера, и два вспомогательных элемента И-НЕ, выходы которых соединены соответственно с входами установки и сбро са RS-триггера ячейки памяти, первые входы вспомогательных элементов И-НЕ являются информационными входами ячейки памяти, а вторые и третьи входы соединены соответственно с выходами элементов И-НЕ RS-триггера, которые являются информационными выходами ячейки памяти, информационные входы каждой ячейки памяти, кроме первой, соединены с информационньми выходами предьщущей ячейки памяти, первый и второй управляющие входы которой соединены с соответствующими управляющими выходами данной ячейки памяти, информационные входы первой ячейки являются информационными входами регистра, а ее управлякщие выходы - управляющими выходами регистра, информационные выходы последней ячейки памяти являются кнформационньми выходами регистра, а ее управлякяцие входы - управляющимг входами регистра s отличающ и и с я тем, что, с целью повышения быстродействия регистра, каждая ячейка памяти содержит дополнительньй RS-триггер на двух элементах И-НЕ к четыре дополнительных элемента , выход первого из которых соединен с управляющим входом RS-триггера ячейки памяти и первым входом второго дополнительного элемента И-НЕ, второй и третий входы которого являются соответственно первым и вторым управляющими входами ячейки памяти, а четвертый вход и первый вход первого дополнительного элемента И-НЕ являются дополнительным управляющим входом ячейки памяти, второй вход первого дополнительного элемента И-НЕ соединен с выходом третьего дополнительного элеме {та И-НЕ, который является первым управляющим выходом ячейки памяти ; первый и второй входы третьего дополнительного элемента И-НЕ соединены с выходами вспомогательных элементов И-НЕ ячейки памяти, а его Tpeti- K вход соединен с выходом четвертого дополнительного элемента И-НЕ, который является вторым управляющим выходом ячейки памяти, выход второго дополнительного ,элемента И-НЕ ячейки памяти соединен с первым входом ее четвертого дополнительного элемента И-НЕ и входом установки дополнительного RS-триггера5 единичный выход которого соединен с вторым входом четвертого дополнительного элемента И-НЕ, нулевой выход является допол

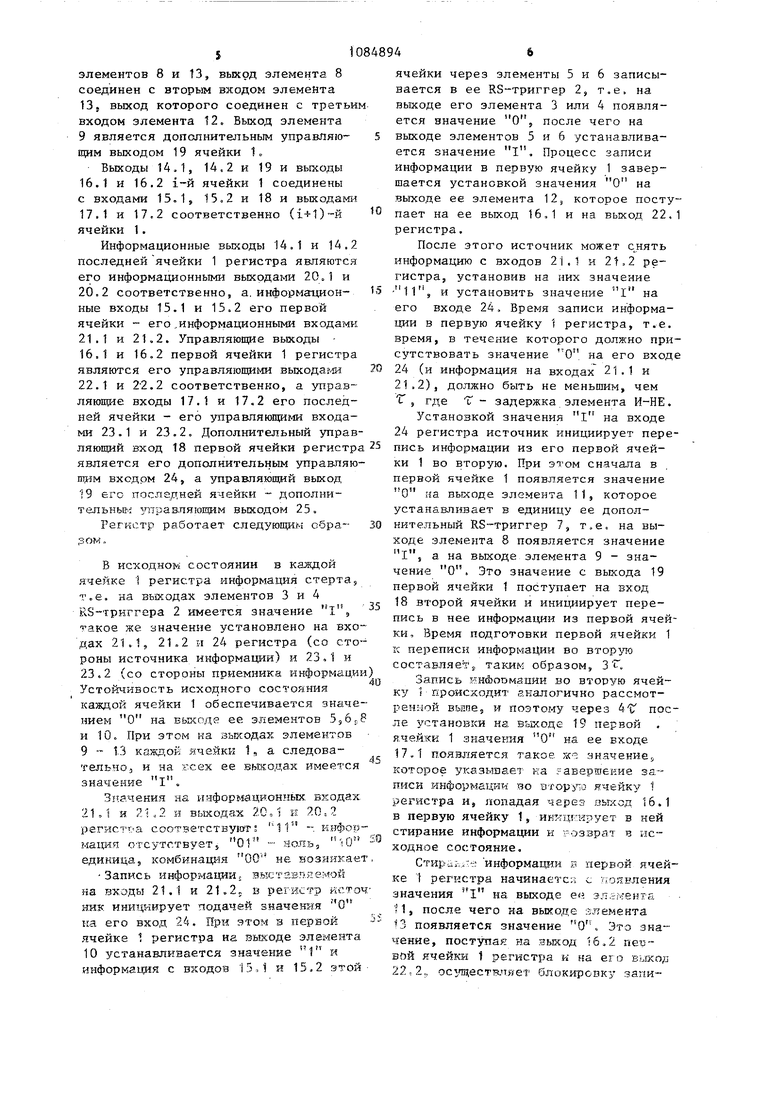

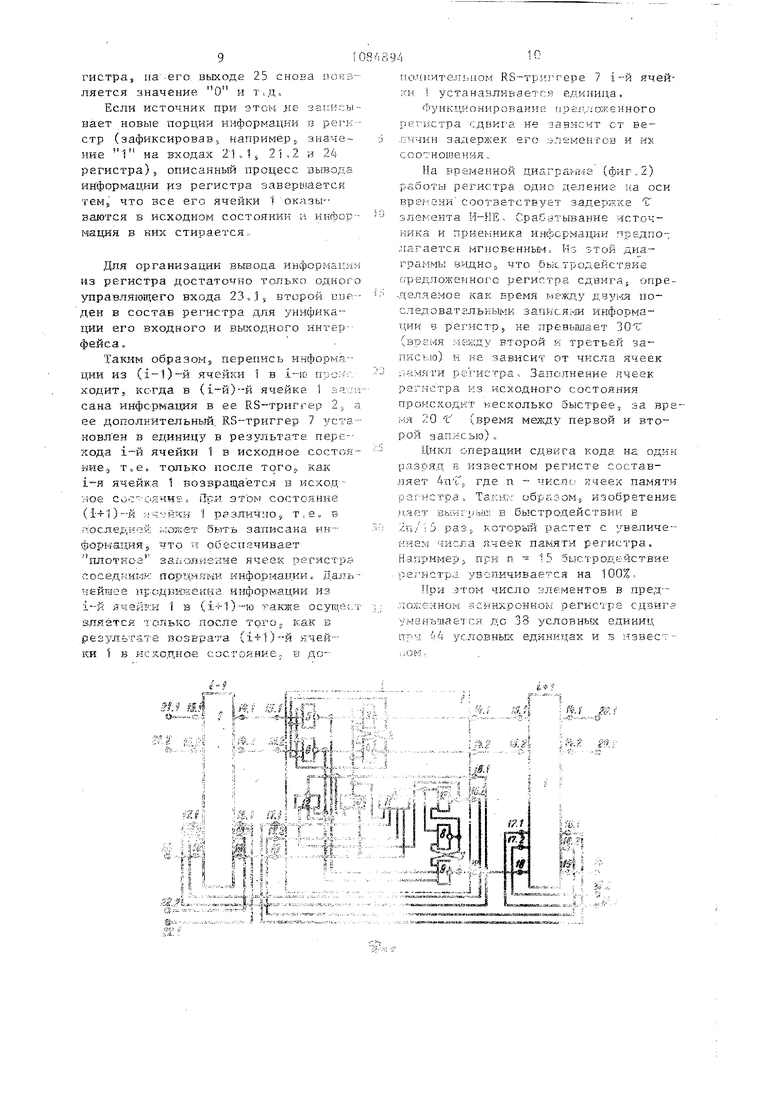

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении цифровых вычислительных машин. Известен асинхронный регистр сдвига на элементах И-НЕ, содержащий ячейки памяти, каждая из которьк состоит из трехстабильного триггера на трех элементах и вспомогательного элемента, причем первые входы первых двух элементов трехстабильного триггера являются информационными входами ячейки, а первые входы его третье го элемента и вспомогательного элемента ячейки объединены и являются управляющим входом ячейки, выходы первых двух элементов трехстабильного триггера являются информационными выходами ячейки, а выход его третьего элемента соединен с вторым входом вспомогательного элемента, вы ход которого является управляющим выходом ячейки, информационные и управляющие входы i-й ячейки соединены соответственно с инфомационными и управляющими выходами (1-1)-й .ячейки, два входа первых двух элементов трехстабильного триггера i-й ячейки и третий вход ее вспомогатель ного элемента соединены соответственно с информационными и управляющим выводами ()-й ячейки, а четвертьй и пятый входы вспомогательного элемента i-й ячейки соединены с информационными выходами ()-A /ячейки til. Недостатком этого регистра сдвиг является избыточкое количество обор дования. Для хранения га разрядов код регистр должен содержать ячеек памяти г поскольку в нем мевду двумя ячейками, хранящими соседние разряд сдвигаемого кода, находится как минимум одна ячейка, в которой информация стерта. Наиболее близким по технической сущности к изобретению является регистр сдвига на элементах И-НЕ, содержащий ячейки памяти, каждая из которьж имеет основной и вспомогательный RS-триггеры на двух элементах каждьй, две пары входов обоих плеч основного RS-триггера объединены между собой и являются парой управляклдих входов ячейки, выход каждого элемента основного RS-триггера соединен с входами обоих элементов вспомогательного RS-триггера и является информационньгм выходом ячейки s выход каждого элемента вспомогательного RS-триггера соединен с входом соответствующего элемента основного RS-триггера и Является управлякщим выходом ячейки, а вход каждого его элемента является информационным входом ячейки, причем информационные выходы каждой ячейки регистра соединены с информационными входами последующей ячейки, управляю;зше )l которой соединены с управляющими входами данной ячейки, при этом информационные входы первой ячейки регистра являются его информационными входами, а ее управляющие выходы - управляющими выходами регистра, информационные вьгходы последней ячейки регистра являются его информационными выходагет, а ее управляющие входы -- управляющими вхоцамк регистра. Регистр экономичен по затратам оборудования: для хранения т-разрядного кода в нем достаточно иметь ячеек, причем каждая ячейка требует для реализации только четьфе четырхвходовьЕ элемента И-НЕ 2. Недостатком известного регистра является его низкое быстродействие (операция сдвига кода на один разряд в нем выполняется за время, равное 4 п f, где п - число ячеек регистра,, а t - задержка элемента И-НЕ) Цель изобретения - повышение быст родействия регистра сдвига. Поставленная цель достигается тем что в регистре сдвига, содержащем ячейки памяти, каждая из которых состоит из RS-триггера на двух элементах И-НЕ, первые входы которых объединены и являются управляющим входом данного триггера, и два вспомогательных элемента И-НЕ, выходы ко торых соединены соответственно с вхо дами установки и сброса RS-триггера ячейки памяти, первые входы вспомогательных элементов И-НЕ являются информационными входами ячейки памяти, а вторые и третьи входы соединены соответственно с выходами злементов И-НЕ RS-триггера, которые являют ся информационными выходами ячейки памяти, информационные входы каждой ячейки памяти, кроме первой, соединены с информационными вьгходами предьщущей ячейки памяти, первьй и второй управляющие входы которой соединены с соответствующими управляющи ми выходами данной ячейки памяти, информационные входы первой ячейки памяти являются информационными входами регистра, а ее управлякяцие выходы - управляющими выходами регистра, информационные выходы последней ячейки памяти являются информационными выxoдa « регистра, а ее управляющие входы - управлякяцими входами регистра, каждая ячейка памяти содержит дополнительный RS-триггер на двух элементах И-НЕ и четьфе дополнительных элемента И-НЕ, выход первого из которых соединен с управляющим входом RS-триггера ячейки памяти и первым входом второго дополнительного элемента И-НЕ, второй и третий входы которого являются соответственно первым и вторым управ ляющими входами ячейки памяти, а четвертьй вход и первый вход первого дополнительного элемента И-НЕ являются дополнительным управляющим входом ячейки памяти, второй вход первого дополнительного элемента И-Н соединен с выходом третьего дополнительного элемента И-НЕ,который является первым управляющим выходом ячейки памяти, первый и второй входы третьего дополнительного элемента И-НЕ соединены с выходами вспомогательных элементов И-НЕ ячейки памяти, а его третий вход соединен с выходом четвертого дополнительного элемента И-НЕ, который является вторым управляющим выходом ячейки памяти, выход второго дополнительного элемента И-НЕ ячейки памяти соединен с первым входом ее четвертого дополнительного элемента И-НЕ и входом установки дополнительного RS-триггера, единичный выход которого соединен с BTOpbiM входом четвертого дополнительного элемента И-НЕ, нулевой выход является дополнительным управляющим выходом ячейки памяти, а входы сброса соединены с вьгходами вспомогательных элементов И-НЕ ячейки памяти, причем дополнительньй управлякнций выход каждой ячейки памяти, кроме последней, соединен с дополнительным управляющим входом последующей ячейки памяти, дополнительный управлякнций вход первой ячейки памяти является дополнительным управляющим входом регистра, а дополнительный управлякяций вьрсод последней ячейки памяти - дополнительным управляющим выходом регистра. На фиг. 1 приведена схема регистра; на фиг. 2 - временная диаграмма его работы. Регистр содержит ячейки 1 памяти, каждая из которых содержит RS-триггер 2 на элементах И-НЕ 3 и 4, вспомогательные элементы И-НЕ 5 и 6, дополнительный RS-триггер 7 на элементах И-НЕ 8 и 9 и дополнительные элементы И-НЕ 10 - 13. Вьход элемента 3(4) является информационным выходом 14.1(14.2) ячейки 1 и соединен с входами элементов 5 и 6, остальные входы которых являются информационными входами 15.1 и 15,2 ячейки 1, а выход элемента 5(6) соединен с входами элементов 3(4), 9 и 12. Остальные входы элементов 3 и 4 объединены и соединены с выходом элемента 10, который соединен также с, первым fexoдом элемента 11. Выходы элементов 12 и 13 являются управляющими выходами 16.1 и 16,2 ячейки 1, а второй и третий входы элемента 11 - ее управляюпщми входами 17.1 и 17.2. Выход элемента 12 соединен с первым входом элемента 10, второй вход которого сое динен с четвертым входом элемента 11 и является дополнительным управляющим входом 18 ячейки 1. Выход элемента 11 соединен с первым входом

элементов 8 и 13, выход элемента 8 соединен с вторым взсодом элемента 13. выход которого соединен с третьи входом элемента 12. Выход элемента 9 является дополнительным управляющим выходом 19 ячейки К

Выходы 14,1, 14.2 и 19 и выходы 16.1 и 16.2 i-й ячейки 1 соединены с входами 15.1s 15.2 и 18 и выходами

Информационные выходы 14.1 и 14.2 последней ячейки 1 регистра являются его информационными выходами 20.1 и

ячейки через элементы 5 и 6 записывается в ее RS-триггер 2, т.е. на выходе его элемента 3 или 4 появляется значение О, после чего на

вькоде элементов 5 и 6 устанавливается значение I. Процесс записи информации в первую ячейку 1 завершается установкой значения О на выходе ее элемента 12j которое поступает на ее выход и на выход 22.1 регистра.

После этого источник может информацию с входов 21.1 и 21,2 регистра, установив на них значение

и установить значение l на его входе 24, Время записи информации в первую ячейку 1 регистра, т.е. время, в течение которого должно присутствовать значение О, на его входе

24 (и информация на входах 21.1 и 21.2), должно быть не меньшим, чем Т, где f - задержка элемента И-НЕ. Установкой значения I на входе 24 регистра источник инициирует перепись информации из его первой ячейки 1 во вторую. При этом сначала в первой ячейке 1 появляется значение О на вьЕкоде элемента 1 1, которое устанавливает в единицу ее дополнительный RS-триггер 7, т.е. на выходе элемента 8 появляется значение а на вькоде элемента 9 - значение О. Это значение с выхода 19 первой ячейки 1 поступает на вход 18 второй ячейки и инициирует перепись в нее информации из первой ячейки. Время подготовки первой ячейки 1 к переписи информации во вторую состаеляет таким образом, 3. Запись ин(Ьоомаиии во вторую ячейку 1 гфоискодит гкалогично рассмотренной вьше, и поэтому через 4J после установки на вьжоде 19 первой . ячейки 1 значения О на ее входе 17,1 появляется такое же значение, которое указывает ка 5авершекие записи информации зо вторите ячейку 1 1эегнстра и попадая через вькод 16.1 в первую ячейку 1, иккцтирует в ней стирание информации и возврат в исходное состояние. Стираг..:,-;: информации в первой ячейке 1 регистра начинаете;-; с появления значения I на выходе е« элемента 11, после чего на выходе элемента 3 появляется значение 0 Это значение, поступая на 16,2 ne j-вой ячейки 1 регистра к на его выход 22,2,, ос.ществ.пяет блокировку записи источником информации в регистр до тех пор, пока в первой ячейке 1 регистра не завершается возврат в исходное состояние. Далее на выходе элемента 12 первой ячейки 1 появляет ся значение 1 (хотя при этом снимается значение О с выхода 16.1 первой ячейки 1 регистра и его выхода 22.1, блокирующее запись источником информации в регистр, источ ник остается заблокированным значением О на выходе 22.2 регистра). Затем появляется значение О на выходе элемента. 10 первой ячейки 1 регистра. Это значение стирает ниформац 1ю в RS-триггере 2 первой ячей ки 1, и на выходах ее элементов 3 и 4 появляется значение 1, а на выходе элемента 5 или 6 - значение О. Это значение сбрасывает в ноль дополнительный RS-триггер 7 первой ячейки 1, т.е. на вьсходе ее элемента 9 (и ее выходе 19) появляется значение 1, а на выходе элемента 8 значение 0 .Процесс возврата первой ячейки 1 в исходное состояние завершается появлением значения 1 на выходе ее элемента 13 и ее выходе 16.2, т.е. на выходе 22.2 регистра. После этого источник может записьшат следзтощую порцию информации в регист Время возврата первой ячейки 1 в исходное состояние, т.е. времмя между подачей значения О на ее выход 16.1 и установкой значения 1 на ее входах 17.1 и 17.2 составляет 9t. ,11ри этом уже через 7f после начала этого процесса разрешается (установко значёйия 1 на выходе 19 первой ячейки 1) перепись информации из вто рой ячейки 1 регистра в его третью ячейку. Перепись информации из второй ячейки 1 регистра в третью и возврат .второй ячейки 1 в исходное состояние происходит аналогично.Предположим, что приемник-не может принять информацию с выходов 20. и 20,2 регистра, и на его входах 23 и 23.2 зафиксировано исходное значение 1 независимо от значения на его выходе 25, тогда последняя ячейка 1 регистра после того, как в нее будет переписана информация из предпоследней его ячейки, не сможет стереть эту информацию к возвратиться в исходное состояние, так как инициация стирания информации и возврата ячейки 1 в исходное состояние осуществляется подачей значения О на вход 17.1 или 17.2 этой ячейки, а у последней ячейки 1 на этих входах зафиксировано значение 1. После того, как информация записана в последнюю ячейку 1 регистра, и на ее выходе 16.1 появляется значение О, предпоследняя ячейка 1 возвращается в исходное состояние. Далее в предпоследнюю ячейку 1 может быть записана следующая порция инфор 1ахии, однако эта ячейка не может провести подготовку к переписи след тощей порции информации в последнюю ячейку 1. В результате при подаче значения 1 на вход 18 предпоследней ячейки 1 на выходе ее элемента t1 сохраняется значение 1 и дополнительный RS-триггер 7 этой ячейки остается в нулевом состоянии, т.е. на выходе 19 предпоследней ячейки 1 сохраняется значение 1, и запись следующей порции информации в последнюю ячейку 1 не происходит. Таким образом, следующие друг за другом порции информации оказываются записанными в соседние ячейки 1 регистра (в данном случае в последнюю и предпоследнюю). Аналогично каждая следующая порция информации проходит по регистру до тех пор, пока встречает ячейки 1, находящиеся в исходном состоянии, и останавливается в последней такой ячейке. Прохождению этой порции дальше по регистру препятствует наличие блокирующего значения О с выхода 16.1 или 16.2 ячейки, которая не вернулась в исходное состояние, Выход информации из регистра в приемник заключается в подаче значения О на вход 23.1 или 23.2 регистра после того, как на его выходе 25 появляется значение О, свидетельствующее о наличии очередной порции информации на выходах 20,1 и 20.2 регистра. При этом последняя ячейка 1 регистра переходит в исходное состояние и через время, равное 7 5 на выходе 25 регистра появляется значение 1, а через 9L в эту ячейку можат быть переписана следующая порция информации. После того, как на выходе 23 регистра появляется значение 1 приемник должен установить на его входах 23.1 и 23.2 зна- . ение 1, после чего, в случае завершения переписи следующей порции нформации в последнюю ячейку 1 регистрЯз па -его выходе 25 снова появляется значение О и т,д.

Если источник при этой ле

зацнсы вает новые порции информации стр (зафиксировав,, например,, значение 1 на входах21„Ь 21,2 и 24 регистра). описанный процесс вьшодг информации из регистра заверилаетск TeMj что все его ячейки 1 окязы-ВаЮТСЯ в исходном СОСТОЯНРП к ИНФСЯ

нация в них стирается..

Для организации вьшода информации из регистра достаточно только одного управляющего входа 23,), второй вые ден в состав регистра для унификации его входного и вьосодного интер фейса.

Таким образом, перепись информа/ции из (1-1)-и ячейки I в i-to npo;f; ХОДИТ; ксГда в (1-й)--й ячейке 1 ;;л,.чг сана информация в ее RS-триггер 2, а ее дополнительный, RS-триггер 7 установлен в единицу в результате пере;-хода i-й ячейки 1 в исходное состояние т.е. только после того с. как i-я ячей :а 1 возвращается в исходное сос СЯчиЕ При этом состояние (i-f-l)--K 1 различно, . в последней; ;.;ожет записана инфорнация5 что iT обеспечивает плотноэ захаолйение ячеек регистра соседкиг-з -;: порцмями инфо,рма.ции, Дальнейшее п.{;:с дви ;1енка информации из i-й 1 в (i-J-1) Ю также осуш;е;./г зляётся чолько после того как в ре23льта7е возврата (1-5-1} й ячейки 1 в исходное состояннв; в до tF I „. ,3 V rr-1p I 1Щ I

- is ir-Г

Й, ffin r г . J|

-v-- .- ..----- . J

-. 1 , I- I

iiiT- ir

:: - ь

1лодп:ите, К8 тригтере 7 i-й ячейки устаназливается единица.

f нкц1-5онировакие прея, ложе иного регистра сдвига не зависит от величин задержек его алиментов и их cooiHoineHHH..

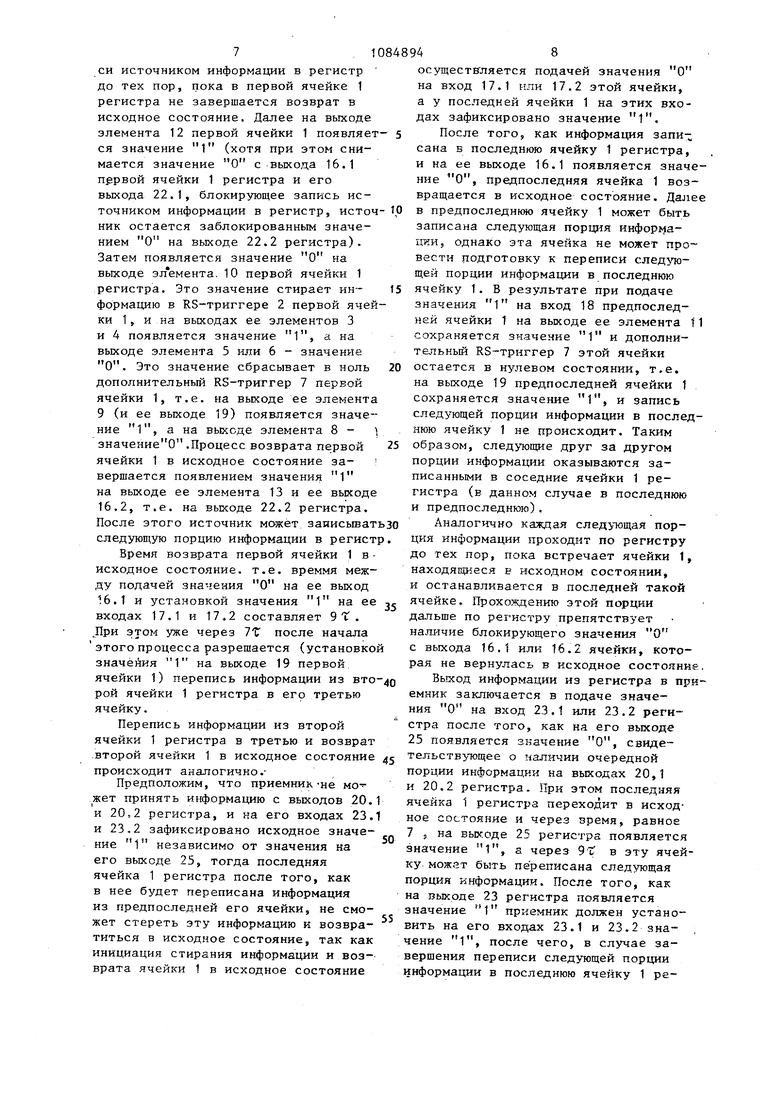

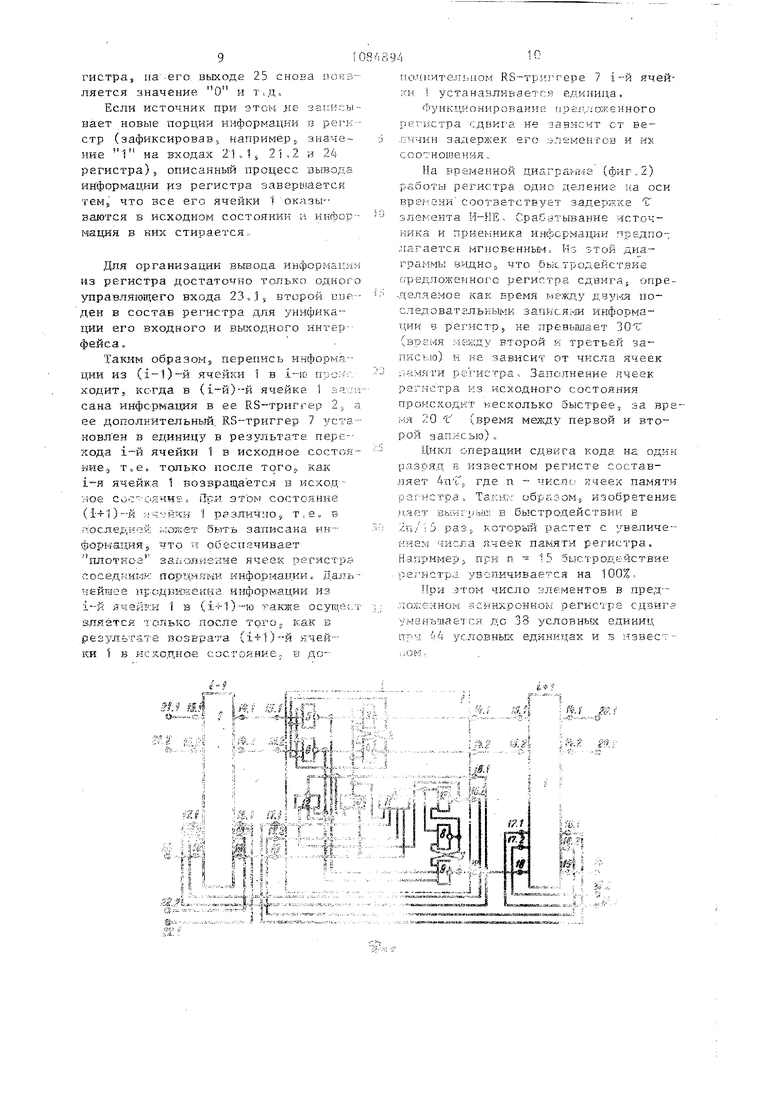

На временной диаграы-га (фиг. 2) paocrffcj регистра одно деление на оси врен;ени соответствует задержке Т элемента И-НЕ, Срабатывание источника и приекр-1ика информации предполагается мгновенньвч. Из зтой диаграммы виднод что быстродействие аредложенногО регистра сдБИга опре.дел,1емое как время ме-жду дзу-ля п,оследоватЕЛЬггынк записями информации в perHCTps не превьшает ЗОТ (BpSfSH ;.1ел;ду второй и третьей записью) к не зависит от числа ячеек ijaMJiTH регистра. Заполнение ячеек рагистра из исходного состояния происходит несколько быстрее, за время 2Q t (время мехзду первой и второй записью),

Цикл операции сдвига кода на одни р-азряд Б известном регисте составляет iit- где п число ячеек памяти рзгнстра. образом, изобретение дает BbiHrijaiui в быстродействии в 2r;/i5 paSj которой растет с увапичениe i числа ячеек памяти регистра, Р1апример при п - 15 быстродействие регистра увеличивается на 100%,

При этом число зле;ментов в пред-лох;с;нном асинхронном регкстре сдвига уменьиает ся до 38 условньнх единиц п;пч ч4 условных единицах и в известilOM,

vj

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Регистр сдвига | 1974 |

|

SU548892A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-04-07—Публикация

1982-09-22—Подача