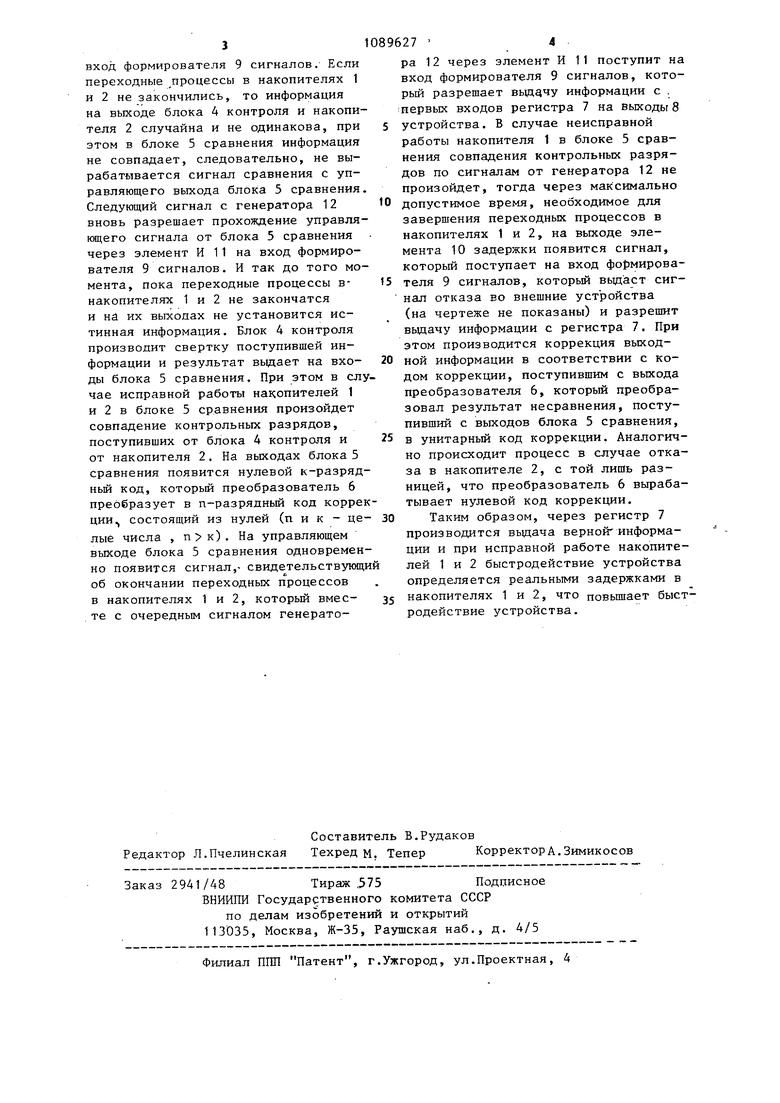

Изобретение относится к вычислительной технике и предназначено для использования в устройствах повышенной надежности, в частности в специализированных вычислительных ма шинах. Известно запоминающее устройство с самоконтролем, которое содержит блоки памяти, коммутаторы, блоки свертки по модулю два, блок поразрядного сравнения, блок управления, блок задержки, в котором за счет поразрядного сравнения информации из идентичных блоков памяти определяется наличие отказов, а с помощью блоков свертки по модулю два и блока управления производится выбор исправ ного блока Л . Недостаток данного запоминающего устройства - невысокое быстродействи Наиболее близким к предлагаемому является запоминанядее устройство с исправлением ошибок, содержащее формирователь адресных сигналов, выход которого соединен с входами основного и дополнительного накопителей, вы ходы которых подключены соответстве но к первым входам регистра числа и дешифратора, выход которого соединен с вторым входом регистра числа, блок анализа ошибок, блок классификации ошибок и блок контроля, причем входы блока анализа ошибок подключены соответственно к первому выходу бло ка контроля и выходу дополнительног накопителя, а выходы соединены соот ветственно с вторым входом дешифратора и одним из входов блока класси фикации ошибок, другой вход которого подключен к второму :выходу блока контроля, вход которого соединен с выходом основного накопителя, первый выход блока классификации ошибок яв ляется одним из выходов устройства, а второй и третий выходы соединены соответственно с третьим и четвертью входами дешифратора, при этом блок анализа ошибок выполнен состоящим из сумматора по модулю два, элементов ИЛИ и схемы сравнения р . Недостатком известного устройст ва является невысокое быстродействи вызванное тем, что блоки контроля и анализа ошибок в каждом цикле работы устройства начинают работу с некоторой задержкой, обусловленной временем считывания информации из накопителей и выбираемой обычно с большим запасом. Цель изобретения - повьшгение быстродействия устройства. Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее первый и второй накопители информации, блок контроля, блок сравнения, преобразователь кодов и регистр числа, одни из входов которого подключены к выходам первого накопителя информации, а другие - к выходам преобразователя кодов, входы которого соединены с одними из выходов блока сравнения, одни из входов которого подключены к выходам второго накопителя инфорнации5 а другие - к выходам блока контроля, входы которого соединены с выходами первого накопителя информации, введены генератор тактовых импульсов, элемент задержки, элемент И и формирователь сигналов, выход которого подключен к управляющему входу регистра числа, а входы подключены к выходу элемента задержки и выходу элемента И, первьм вход которого соединен с выходом генератора тактовых им:пульсов, а второй вход - с другим выходом блока сравнения, причем входы элемента задержки и генератора тактовых импульсов объединены и являются одним из управляющих входов устройства. На чертеже изображена структурная схема запоминаюа1его устройства с самоконтролем. Устройство содержит первый 1 и второй 2 накопители информации, имеющие адресные входы 3, блок 4 контроля, блок 5 сравнения, преобразователь 6 кодов, регистр 7 числа, имеющий выходы 8, формирователь 9 сигналов, элемент 10 задержки, элемент И 11 и генератор 12 тактовыхимпульсов, вход 13 которого является одним из управляющих входов устройства. Предлагаемое устройство работает следующим образом. При поступлении адресных сигналов на входы 3 в накопителях 1 и 2 начинается процесс выборки информации, при этом на их выходах появляется случайная информация, соответствующая переходному процессу. Одновременно сигнал, поступивший на вход 13, запускает генератор 12, сигналы с выхода которого разрешают прохождение управлянщего сигнала с выхода блока 5 сравнения через элемент И 11 на

вход формирователя 9 сигналов. Если переходные процессы в накопителях 1 и 2 не закончились, то информация на выходе блока 4 контроля и накопителя 2 случайна и не одинакова, при этом в блоке 5 сравнения информация не совпадает, следовательно, не вырабатывается сигнал сравнения с управляющего выхода блока 5 сравнения Следующий сигнал с генератора 12 вновь разрешает прохождение управляющего сигнала от блока 5 сравнения через элемент И 11 на вход формирователя 9 сигналов. И так до того момента, пока переходные процессы внакопителях 1 и 2 не закончатся и на их выходах не установится истинная информация. Блок 4 контроля производит свертку поступившей информации и результат выдает на входы блока 5 сравнения. При этом в случае исправной работы накопителей 1 и 2 в блоке 5 сравнения произойдет совпадение контрольных разрядов, поступивших от блока 4 контроля и от накопителя 2. На выходах блока 5 сравнения появится нулевой к-разрядный код, который преобразователь 6 преобразует в п-разрядный код коррекции состоящий из нулей (пик- целые числа , п к). На управляющем выходе блока 5 сравнения одновременно появится сигнал,- свидетельствующи об окончании переходных процессов в накопителях 1 и 2, который вместе с очередным сигналом генератора 12 через элемент И 11 поступит на вход формирователя 9 сигналов, который разрешает выдачу информации с . первых входов регистра 7 на выходы 8 устройства. В случае неисправной работы накопителя 1 в блоке 5 сравнения совпадения контрольных разрядов по сигналам от генератора 12 не произойдет, тогда через максимально допустимое время, необходимое для завершения переходных процессов в накопителях 1 и 2, на выходе элемента 10 задержки появится сигнал, который поступает на вход фо{1мирова5 теля 9 сигналов, который вьщаст сиг нал отказа во внешние устройства (на чертеже не показаны) и разрешит вьщачу информации с регистра 7, При этом производится коррекция выходной информации в соответствии с кодом коррекции, поступившим с выхода преобразователя 6, который преобразовал результат несравнения, поступивший с выходов блока 5 сравнения, в унитарный код коррекции. Аналогично происходит процесс в случае отказа в накопителе 2, с той лишь разницей, что преобразователь 6 вырабатывает нулевой код коррекции.

Таким образом, через регистр 7 производится вьщача вернойинформации и при исправной работе накопителей 1 и 2 быстродействие устройства определяется реальными задержками в

накопителях 1 и 2, что повьш1ает быстродействие устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь с самоконтролем | 1986 |

|

SU1367155A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство для контроля каналов записи аппарата магнитной записи | 1986 |

|

SU1411818A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU951406A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU1001174A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1164790A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее первый и второй накопители информации, блок контроля, блок сравнения, преобразователь кодов и регистр числа, одни из входов которого подключены к выходам первого накопителя информации, а другие - к выходам преобразователя кодов, входы которого соединены с одними из выходов блока сравнения, одни из входов которого подключены к выходам второго накопителя информации, а другие - к выходам блока контроля, входы которого соединены с выходами первого накопителя информации, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены генератор тактовых импульсов, элемент задержки, элемент И и формирователь сигналов, выход которого подключен к управляющему входу регистра числа, а входы подключены к выходу элемента задержки и выходу элемента И, первый вход которого соединен с выходом генератора тактос S вых импульсов, а второй вход - с другим выходом блока сравнения, причем входы элемента задержки и генератора тактовых импульсов объединены и являются одним из управляющих входов устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Резервированное оперативное запоминащее устройство | 1975 |

|

SU589623A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| 1980 |

|

SU928421A1 | |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-04-30—Публикация

1982-06-10—Подача