гие выходы блока сравнения являются другими выходами устройства, третьи выходы блоков сравнения группы подключены к входам формирователя сигналов отказа..

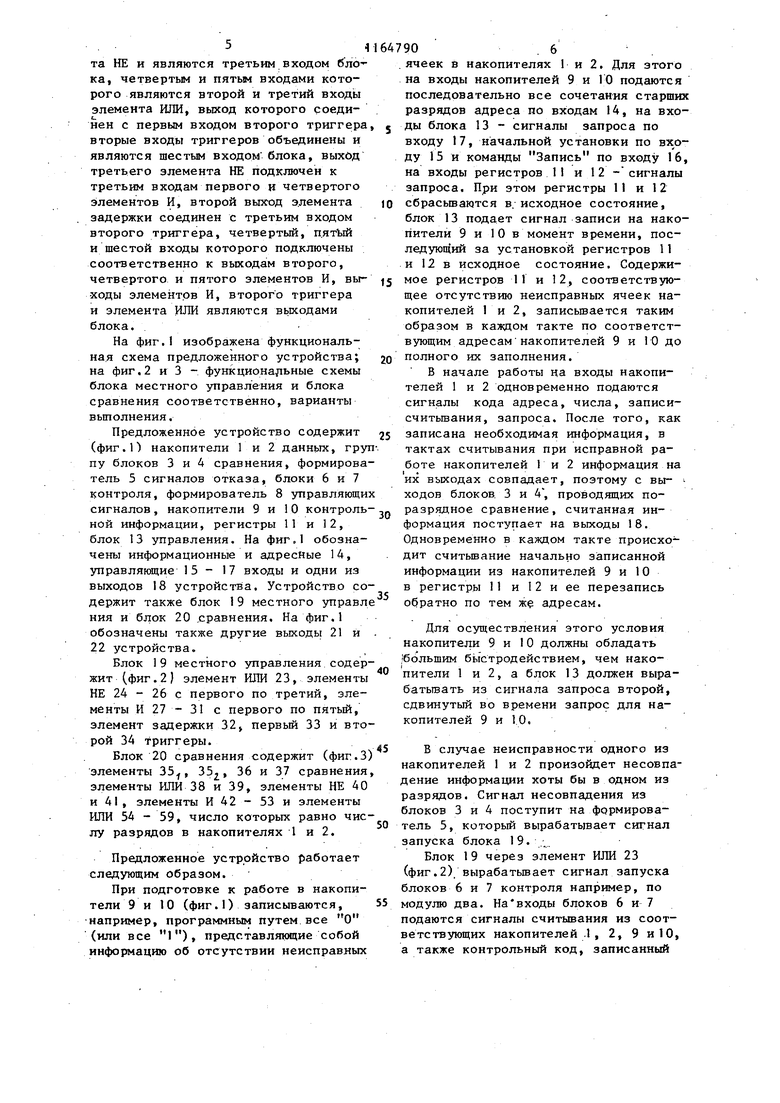

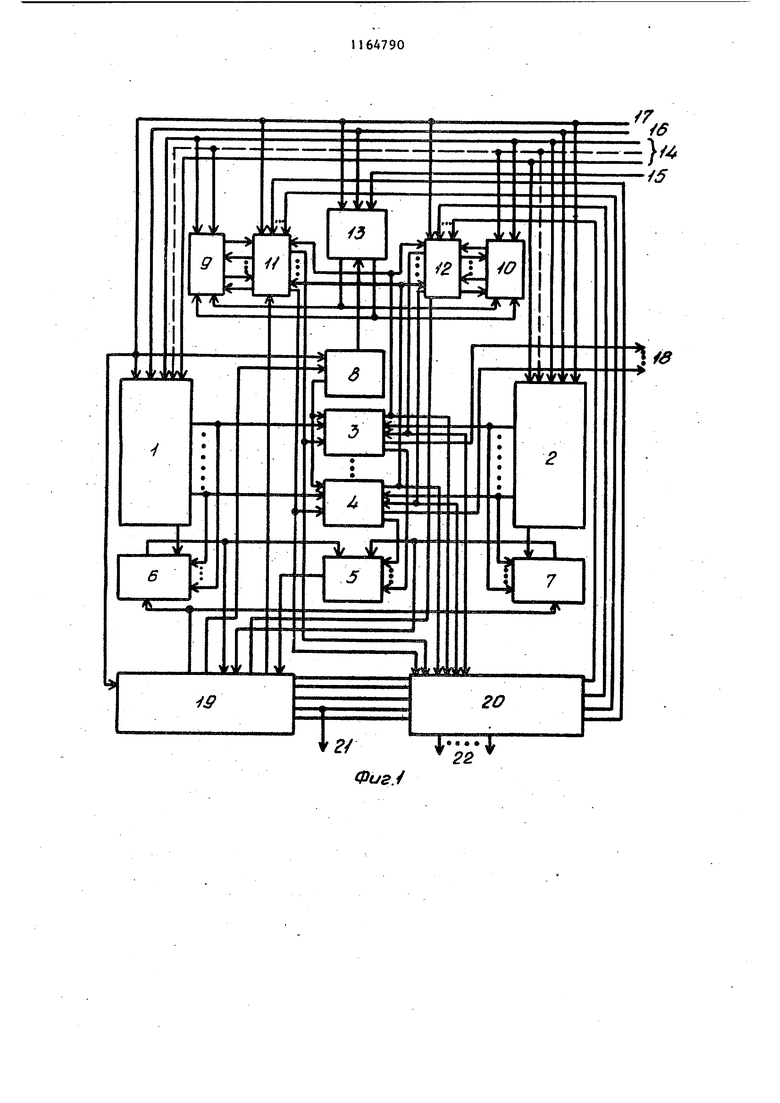

2. Устройство по П.1, о т ли чающееся тем, что блок местного управления содержит элемент ИЛИ, триггеры, элементы НЕ, элемент задержки и элементы И с первого по пятый, причем первый вход первого триггера и первьй вход элемента ИЛИ являются первым входом блока, вход первого элемента НЕ и первые входы элементов И с второго по четвертый являются вторым входом блока, выход первого триггера подключен к входу элемента задержки, вьрсод которого соединен с первыми входами первого и пятого элементов И, вторыми входами третьего и четвертого элементов И и входом второго элемента НЕ, выход которого подключен к второму входу второго

элемента И, выход первого элемента НЕ соединен с вторыми входами первого и пятого элементов И, третьи входы второго, третьего и пятого элементов И соединены с входом третьего элементаНЕ и являются третьим входом блока, четвертым и пятьм входами которого являются второй и третий входы элемента ИЛИ, выход которого соединен с первым входом второго триггера, вторые входы триггеров объединены и являются шестым входом блока, выход третьего элемента НЕ подключен к третьим входам первого и четвертого элементов И, второй выход элемента задержки соединен с третьим входом второго триггера, четвертый, пятый и шестой входы которого подключены соответственно к выходам второго, четвертого и пятого элементов И, выходы элементов И, второго триггера и элемента. ИЛИ являются выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

| Запоминающее устройство с обнаружением отказов | 1981 |

|

SU1005192A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU879655A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Оперативное запоминающее устройство с самоконтролем | 1978 |

|

SU771731A1 |

| Резервированное запоминающее устройство | 1985 |

|

SU1278984A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2024969C1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1188784A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| Устройство для контроля информационного тракта "запоминающее устройство команд-процессор | 1980 |

|

SU1005060A2 |

1. ЗАПШЙНАЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее группу блоков сравнения, накопители данных, одни выходы которых подключены к одним из входов блоков сравнения группы и к входам соответствующих блоков контроля, другие выходы - к первым управляющим входам соответствующих блоков крнтроля, выходы которых соединены с управляющими входами формирователя сигналов отказа, формирователь управляющих сигналов, первый выход которого подключен к управляющим входам блоков сравнения группы, регистры, входы первой группы которых соединены с первыми выходами блоков сравнения группы, другие входы которых подключены к одним из выходов регистров, накопители контрольной инфо рмации, одни входы и выходы которых соединены с другими выходами и со входами второй группы соответствующего регистра, и блок управления, первый вход которого подключен к второму выходу формирователя управляющих сигналов, выходы подключены к управляющим входам накопителей контрольной информации, а второй, третий и четвертый входы являются управляющими входами устройства, одними выходами которого являю7 ся вторые выходы блоков сравнения группы, причем третий и четвертый входы блока управления соединены с первыми и вторьми .управляющими входами накопителей данных, первые управляющие входы регистров и первый вход формирователя управляющих сигналов подключены к четвертому входу блока управления, входы накопителей данных являются .информационными и адресными входами устройства, о т личающе.еся тем, что, с целью повьшения надежности устройства, в него введены блок сравнения и блок местного управления, первый вход которого соединен с выходом СП формирователя сигналов отказа, второй и третий входы подключены к выходам блоков контроля, а четвертый и пятый входы - к первому и второму управляющим выходам блока сравнения, одни выходы КОТОРОГО соединены со входами третьей группы регистров, . Од вторые управляющие входы которых под4 ключены к первому и второму выходам блока местного управления, третий vl выход которого соединен с вторым со входом формирователя управляющих сигналов , четвертый выход - с вторьми управляющш и входами блоков контроля, а выходы с пятого по седьмой подключе.ны к управляющим входам блока сравнения, одни входы которого соединены с одними из выходов регистров, а другие входы - с первьми выходами блоков сравнения группы, причем шестой вход блока местного управления соединен с вторыми управляющими входами накопителей данных, шестой выход блока местного управления и дру

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам.

Известно запоминающее устройство с самоконтролем, в котором применяется контроль сравнением в каждом такте считьшаемой из двух идентичных накопителей информации, образованием сверток для каждого накопителя в случае несравнения хотя бы по одному из разрядов и отключением накопителя, в котором свертка не совпала с информацией в контрольном разряде ll.

Недостатком этого устройства явлйется низкая надежность.

Наиболее близким техническим решением к изобретению является запоминающее устройство с самоконтролем содержащее накопители, схемы сравнения, формирователь сигналов отказа, блоки контроля, блок задержки, дополнительные накопители, регистры, блок управления, числовые и адресны шины, шину начальной установки, шину Запись - считьшание, шину Запрос, выходные шины устройства, причем информационные выходы каждо2

го из накопителей подключены к соответствующим входам схем сравнения и к входам соответствующего блока контроля, выход дополнительного информационного разряда каждого из накопителей подключен к первому управлякяцему входу соответствующего блока контроля, выход которого подключен к соответствующему управляющему

входу формирователя сигналов отказа, первый выход формирователя сигналов отказа подключен к в.торым управляющим входам блоков контроляj а второй выход формирователя сигналов отказа

подключен к первому входу блока задержки, первый управляющий выход которого подключен к первым управляющим входам схем сравнения, первые входы каждого из регистров подключены к соответствующим выходам схем сравнения, первые вькоды - к соответствующим вторым управлякицим входам схем сравнения, а управляющий вход каждого из регистров подключен

к выходу соответствующего блока

контроля, вторые выходы регистров , подк.гаочены к входам соответствующего дополнительного накопителя, а выходы дополнительных накопителей - к вторым .входам сортветствующего регистра второй управляющий выход блока задержки подключен к входу блока управления, управл5пощие выходы которого подключены к соответствующим управляющим входам дополнительных накопителей 2 7. Недостатком известного устройства является низкая надежность вследствие того, что в нем не обеспечивается коррекция ошибок в случае возникновения неисправностей в одноименных эонах адресов обоих накопителей в различных разрядах и в одноименных разрядах, а также не обеспечивается коррекция четных ошибок в любом из накопителей. Цель изобретения - повышение надежности запоминающего устройства с самоконтролем. Поставленная цель достигается тем что в запоминающее устройство с самоконтролем, содержащее группу блоков сравнения, накопители данных, одни выходы которых подключены к одним из входов блоков сравнения группы и к .,входам соответствующих блоков КОНТРОля, другие выходы - к первым управляющим входам соответствующих блоков контроля, выходы которых соедшсены с управляющими входами формирователя сигналов отказа, формирователь управляющих сигналов, первый выход которого подключен к управляющим входам блоков сравнения группы, регистры, входы первой группы которых соединены с первыми выходами блоков сравнения группы, другие входы которых подключеиы к одним из выходов регистров, накопители контрольной информации, одни входы и выходы которых соединены с другими выходами и с входами второй группы соответствующего регистра, и блок управления, первый вход которо- 45 по

го подключен к второму выходу формирователя управляющих сигналов, выходы подключены к зшравлякицим входам накопителей контрольной информации, а второй, третий и четвертый входы 50 являются управляющими входами устройства, одними выходами которого являются вторые выходы блоков срав1 енйя группы, причем третий и четвертый входы блока управления соединены с 55 первыми и вторыми управляющими входами накопителей данных, первые управляющие входы регистров и первый вход

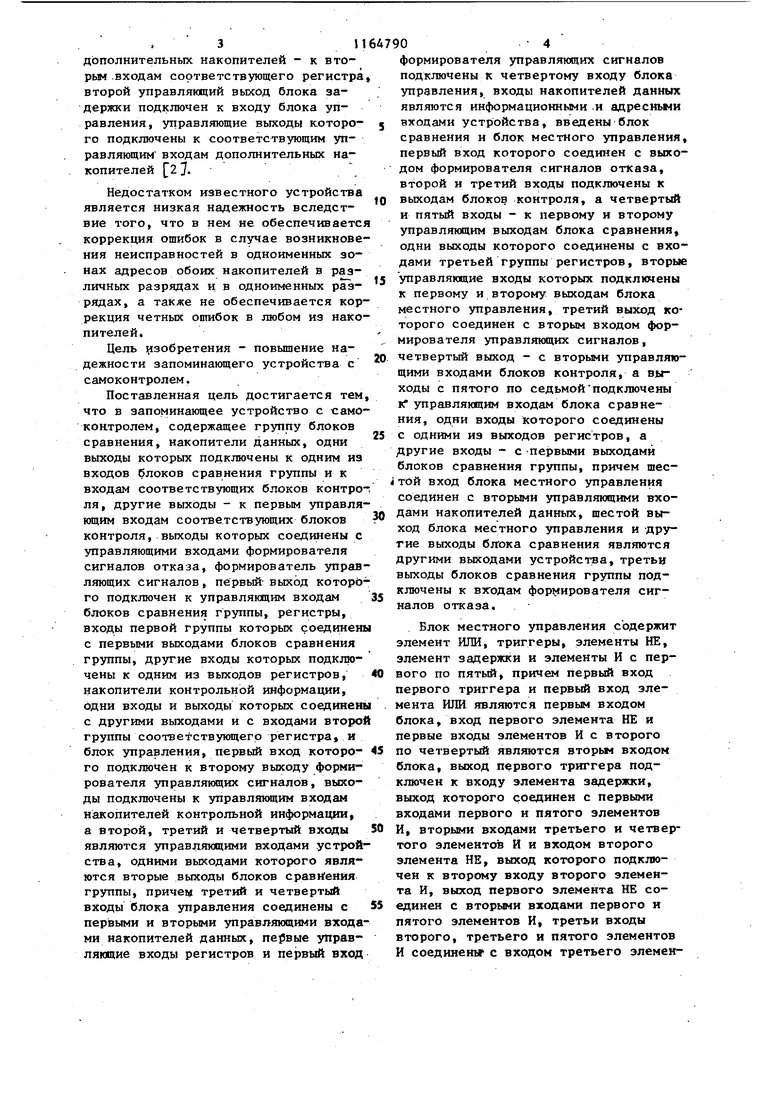

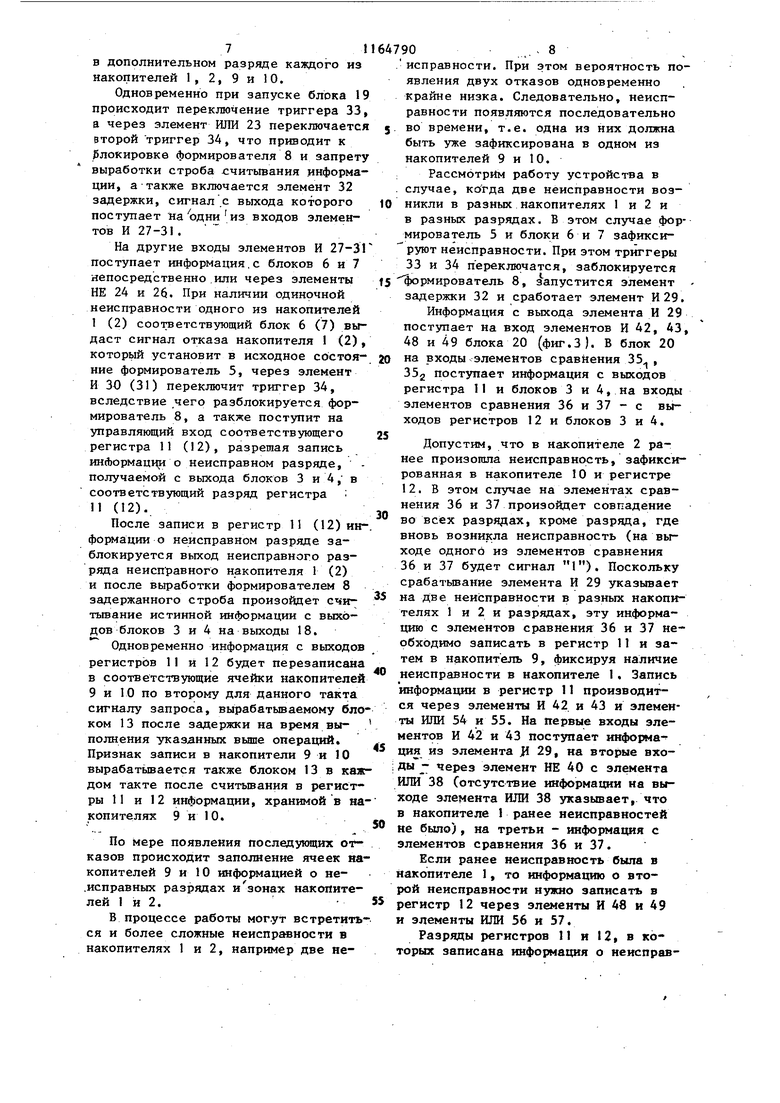

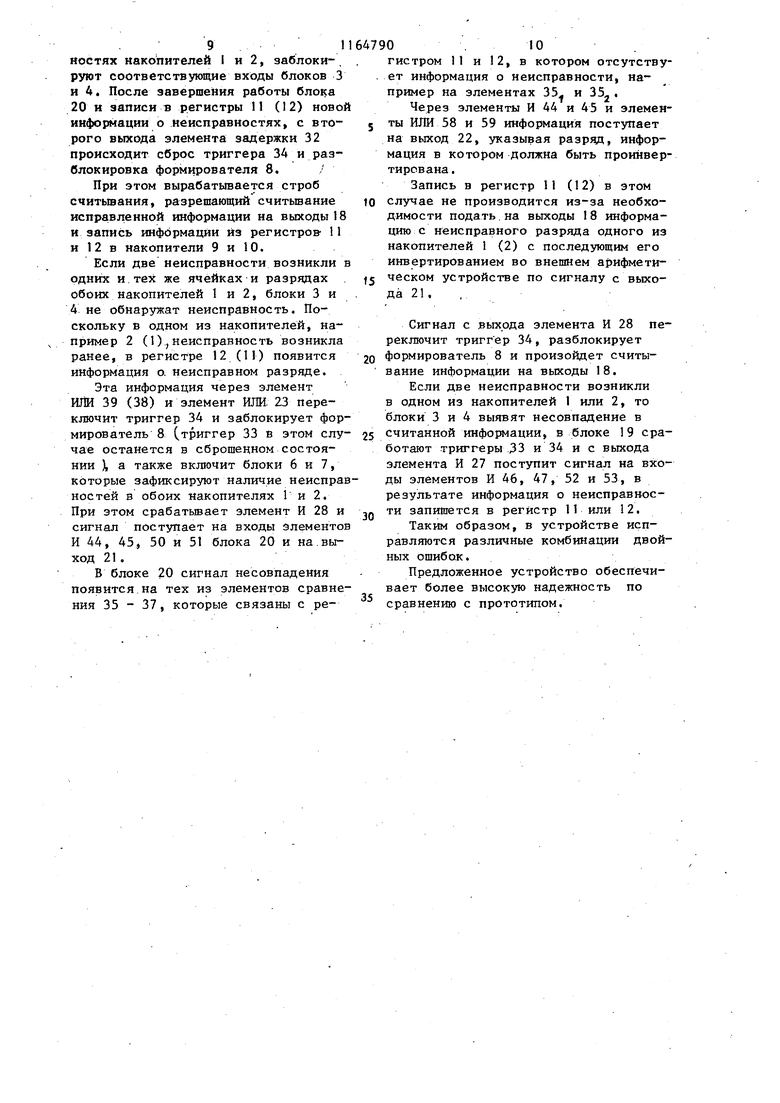

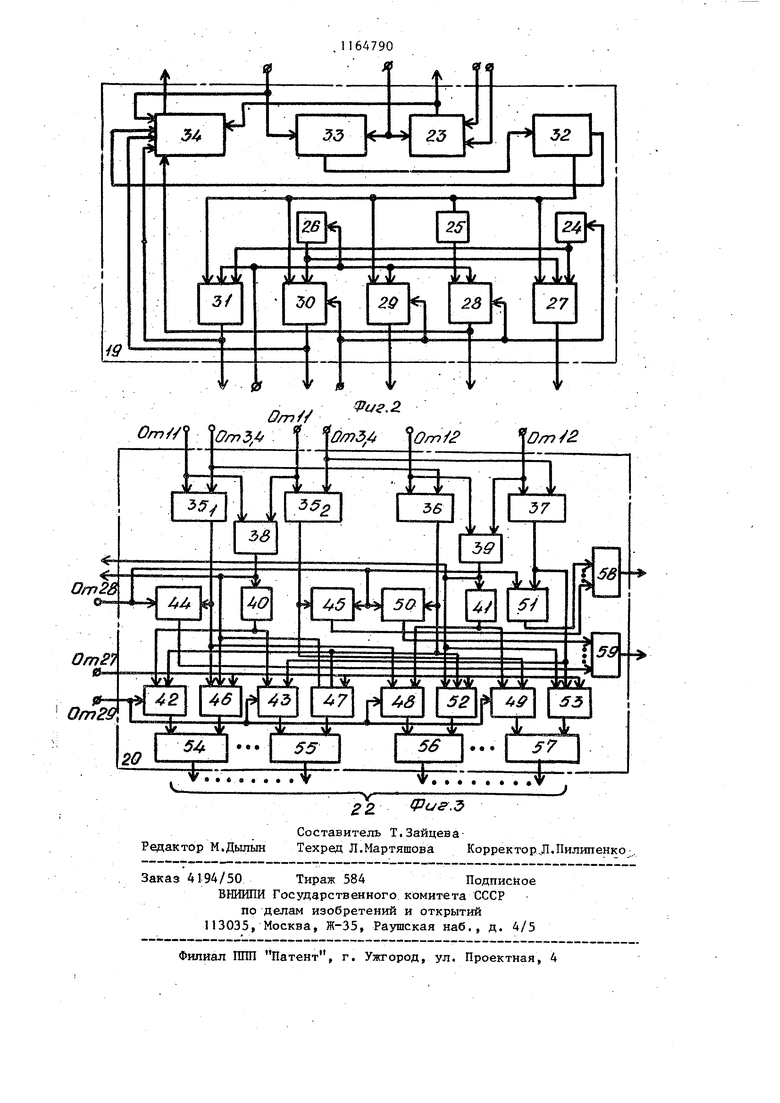

блока, выход первого триггера подключен к входу элемента задержки, выход которого соединен с первыми входами первого и пятого элементов И, вторыми входами третьего и четвертого элементов И и входом второго элемента НЕ, выход которого подключен к второму входу второго элемента И, выход первого элемента НЕ соединен с ВТОР1Л4И входами первого и пятого элементов И, третьи входы второго, третьего и пятого элементов И соединен с входом третьего элеменформирователя управляющих сигналов подключены к четвертому входу блока управления, входы накопителей данных являются информационными .и адресньми входами устройства, введены блок сравнения и блок местного управления, первый вход которого соединен с выходом формирователя сигналов отказа, второй и третий входы подключены к выходам блоков контроля, а четвертый и пятый входы - к первому и второму управляющим выходам блока сравнения, одни выходы которого соединены с входами третьей группы регистров, вторые управляющие входы которых подключены к первому и второму выходам блока местного управления, третий выход которого соединен с вторым входом формирователя управляющих сигналов, четвертый выход - с вторыми управляющими входами блоков контроля, а выходы с пятого по седьмойподключены If управляющим входам блока сравнения, одни входы которого соединены с одними из выходов регистров, а другие входы - с первыми выходами блоков сравнения группы, причем шестой вход блока местного управления и v.i « У соединен с вторыми управляющими вхонш у у дшищюти дами накопителей данных, шестой выход блока местного управления и другие выходы блока сравнения являются другими выходами устройства, третьи выходы блоков сравнения группы подключены к входам формирователя сигналов отказа. Блок местного управления содержит элемент ИЛИ, триггеры, элементы НЕ, элемент задержки и элементы И с первого по пятый, причем первый вход первого триггера и первый вход элемента ИЛИ являются первым входом блока, вход первого элемента НЕ и первые входы элементов И с второго четвертый являются вторьм входом та НЕ и являются третьим входом бло ка, четвертым и пятьм входами которого являются второй и третий входы элемеита ИЛИ, выход которого соединен с первым входом второго триггера вторые входы триггеров объединены и являются шестым входомблока, выход третьего элемента НЕ подключен к третьим входам первого и четвертого элементов И, второй выход элемента задержки соединен с третьим входом второго триггера, четвертый, пятЪгй и шестой входы которого подключены соответственно к выходам второго, четвертого и пятого элементов И, выходы элементов И, второго триггера и элемента ИЛИ являются вькодами блока. На фиг,1 изображена функциональная схема предложенного устройства; на фиг.2 и 3 - функциона;1ьные схемы блока местного управления и блока сравнения соответственно, варианты вьтолнения. Предложенное устройство содержит (фиг.1) накопители 1 и 2 данньгх, гру пу блоков 3 и 4 сравнения, формирова тель 5 сигналов отказа, блоки 6 и 7 контроля, формирователь 8 управляющи сигналов, накопители 9 и 10 контроль ной информации, регистры П и 12, блок 13 управления. На фиг.1 обозначены информационные и адресные 14, управляющие 15 - 17 входы и одни из выходов 18 устройства. Устройство со держит также блок 19 местного управл ния и блок 20 „сравнения. На фиг.1 обозначены также другие выходы 21 и 22 устройства. Блок 19 местного управления содер жит (фиг. 2) элемент ИЛИ 23, элементы НЕ 24 - 26 с первого по третий, элементы И 27 - 31 с первого по пятый, элемент задержки 32, первьй 33 и вто рой 34 триггеры. Блок 20 сравнения содержит (фиг.З элементы 35, 35, 36 и 37 сравнения элементы РШИ 38 и 39, элементы НЕ 40 и 41, элементы И 42 - 53 и элементы ИЛИ 54 - 59, число которых равно чис лу разрядов в накопителях 1 и 2. Предложенное устройство работает следующим образом. При подготовке к работе в накопители 9 и 10 (фиг.1) записываются, например, программным путем все О (или все 1), представляющие собой информацию об отсутствии неисправных ячеек в накопителях 1 и 2. Для этого на входы накопителей 9 и 10 подаются последовательно все сочетания старших разрядов адреса по входам 14, на входы блока 13 - сигналы запроса по входу 17, начальной установки по входу 15 и команды Запись по входу 16, на входы регистров II и 12 - сигналы запроса. Прн этом регистры 11 и 12 сбрасьшаются в/исходное состояние, блок 13 подает сигнал записи на накопители 9 и 10 в момент времени, последующий за установкой регистров 11 и 12 в исходное состояние. Содержимое регистров 11 и 12, соответствующее отсутствию неисправных ячеек накопителей 1 и 2, записьшается таким образом в каждом такте по соответствующим адресам накопителей 9 и 10 до полного их заполнения. В начале работы на входы накопителей 1 и 2 одновременно подаются сигналы кода адреса, числа, записисчитьтания, запроса. После того, как записана необходимая информация, в тактах считывания при исправной работе накопителей 1 и 2 информация на их выходах совпадает, поэтому с вьг ходов блоков. 3 и 4, проводящих поразрядное сравнение, считанная информация поступает на выходы 18. Одновременно в каждом такте происходит считьшание начально записанной информации из накопителей 9 и 10 в регистры 11 и 12 и ее перезапись обратно по тем же адресам. Для осуществления этого условия накопители 9 и 10 должны обладать /большим быстродействием, чем накопители 1 и 2, а блок 13 должен вырабатьшать из сигнала запроса второй, сдвинутый во времени запрос для накопителей 9 и 10. В случае неисправности одного из накопителей 1 и 2 произойдет несовпаение информации хоты бы в одном из разрядов. Сигнал несовпадения из блоков 3 и 4 поступит на формирователь 5, который вырабатывает сигнал запуска блока 19. ... Блок 19 через элемент ИЛИ 23 (фиг. 2)/ вырабатьшает сигнал запуска блоков 6 и 7 контроля например, по модулю два. Навходы блоков 6 и 7 подаются сигналы считывания из соответствующих накопителей Л, 2, 9 н10, а также контрольный код, записанный в дополнительном разряде каждого из накопителей 1, 2, 9 и 10. Одновременно при запуске блока 19 происходит переключение триггера 33, а через элемент ИЖ 23 переключается второй триггер 34, что приводит к блокировке формирователя 8 и запрету выработки строба считьгоания информации, а также включается злемент 32 задержки, сигнал .с выхода которого поступает наоднииз входов элементов И 27-31. На другие входы элементов И 27-ЗР поступает информация,с блоков 6 и 7 непосредственно.или через элементы НЕ 24 и 26. При наличии одиночной неисправности одного из накопителей I(2) соответствующий блок 6 (7) выдаст сигнал отказа накопителя 1 (2), который установит в исходное состояние формирователь 5, через элемент И 30 (31) переключит триггер 34, вследствие чего разблокируется формирователь 8, а также поступит на управляющий вход соответствующего регистра 11 (12), разрешая запись инАормац о неисправном разряде, получаемой с выхода блоков 3 и 4, в соответствующий разряд регистра II(12). После записи в регистр 11 (12) информации о неисправном разряде заблокируется выход неисправного разряда неисправного накопителя 1 (2) и после выработки формирователем 8 задержанного строба произойдет считьшание истинной информации с выходов блоков 3 и 4 на выходы 18. Одновременно информация с выходов регистров II и 12 будет перезаписана в соответствующие ячейки накопителей 9 и 10 по второму для данного такта сигналу запроса, вырабатываемому бло ком 13 после задержки на время выполнения указднных выше операций. Признак записи в накопители 9 и 10 вырабатывается также блоком 13 в каж дом такте после считьшания в регистры 1 1 и 12 информации, хранимой в на копителях 9 и 10. По мере появления последующих отказов происходит заполнение ячеек на копителей 9 и 10 информацией о не,исправных разрядах изонах накопителей 1 и 2.В процессе работы могут встретить ся и более сложные неисправности в накопителях 1 и 2, например две неисправности. При этом вероятность появления двух отказов одновременно крайне низка. Следовательно, неисправности появляются последовательно во времени, т.е. одна из них должна быть уже зафиксирована в одном из накопителей 9 и 10. Рассмотрим работу устройства в случае, когда две неисправности возникли в разных накопителях 1 и 2 и в разных разрядах. В этом случае формирователь 5 и блоки 6 и 7 зафиксируют неисправности. При этом триггеры 33 и 34 переключатся, заблокируется рмирователь 8, запустится элемент задержки 32 и сработает элемент И 29. Информация с выхода элемента И 29 поступает на вход элементов И 42, A3, 48 и 49 блока 20 (фиг.З). В блок 20 на входы элементов сравнения 35, ЗЗд поступает информация с выходов регистра 11 и блоков 3 и 4, на входы элементов сравнения 36 и 37 - с выходов регистров 12 и блоков 3 и 4. Допустим, что в накопителе 2 ранее произошла неисправность, зафиксированная в накопителе 10 и регистре 12. В этом случае на элементах сравнения 36 и 37 произойдет совпадение во всех разрядах, кроме разряда, где вновь возникла неисправность (на выходе одного из элементов сравнения 36 и 37 будет сигнал 1). Поскольку срабатьшание элемента И 29 указывает на Две неисправности в разных накопителях 1 и 2 и разрядах, эту информацию с элементов сравнения 36 и 37 необходимо записать в регистр 11 и затем в накопитель 9, фиксируя наличие неисправности в накопителе 1. Запись информации в регистр 11 производится через элементы И 42 и 43 и элементы ИЛИ 54 и 55. На первые входы элементов И 42 и 43 поступает информадня из элемента |1 29, на вторые входы - через элемент НЕ 40 с элемента ИЛИ 38 Сотсутствие информации на выходе элемента ИЛИ 38 указывает, что в накопителе 1 ранее неисправностей не было), на третьи - информация с элементов сравнения 36 и 37. Если ранее неисправность была в накопителе 1, то информацию о второй неисправности нужно записать в регистр 12 через элементы И 48 и 49 и элементы ИЛИ 56 и 57. Разряды регистров П и 12, в которых записана информация о неисправ9П

ностях накопителей I и 2, заблокируют соответствующие входы блоков 3 и 4. После завершения работы блока 20 и записи в регистры 11 (12) новой информации о неисправностях, с второго выхода элемента задержки 32 происходит сброс триггера ЗА и разблокировка формирователя 8.

При этом вырабатывается строб считьгаания, разрешающий считывание исправленной информации на выходы 18 и запись информации из регистров- 11 и 12 в накопители 9 и 10.

Если две неисправности возникли в одних и тех же ячейках и разрядах обоих накопителей 1 и 2, блоки 3 и 4 не обнаружат неисправность. Поскольку в одном из накопителей, например 2 (1)., неисправность возникла ранее, в регистре 12 (1) появится информация о. неисправном разряде.

Эта информация через элемент ИЛИ 39 (38) и злемент ИЛИ 23 переключит триггер 34 и заблокирует формирователь 8 (триггер 33 в этом случае останется в сброшенном состоянии а также включит блоки 6 и 7, которые зафиксируют наличие неисправностей в обоих Накопителях Г и 2. При этом срабатьюает элемент И 28 и сигнал поступает на входы элементов И 44, 45, 50 и 51 блока 20 и на.выход 21 ,

В блоке 20 сигнал несовпадения появится на тех из элементов сравнения 35-37, которые связаны с ре4790 . 10

гистром 11 и 12, в котором отсутству. ет информация о неисправности, например на элементах 35 и 35.

Через элементы И 44 и 45 и элеменJ ты ИЛИ 58 и 59 информация поступает на вьпсод 22, указывая разряд, информация в котором должна быть проинвертирована.

Запись в регистр П (12) в этом fO случае не производится из-за необходимости подать на выходы I8 информацию с неисправного разряда одного из накопителей 1 (2) с последующим его инвертированием во внешнем арифмети1«1 ческом устройстве по сигналу с выхода 21. ,,

Сигнал с выхода элемента И 28 переключит триггер 34, разблокирует 20 формирователь 8 и произойдет считывание информации на выходы 18.

Если две неисправности возникли в одном из накопителей I или 2, то блоки 3 и 4 выявят несовпадение в 5 считанной информации, в блоке 19 сработают триггеры .33 и 34 и с выхода элемента И 27 поступит сигнал на входы элементов И 46, 47, 52 и 53, в результате информация о неисправности запишется в регистр 11 или 12.

Таким образом, в устройстве исправляются различные комбинации двойных ошибок.

Предложенное устройство обеспечивает более высокую надежность по

сравнению с прототипом.

2Г

j. 22

Фиг.

1164790

I

t

| I | |||

| Запоминающее устройство с самоконтролем | 1977 |

|

SU696545A1 |

| Солесос | 1922 |

|

SU29A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU879655A1 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1985-06-30—Публикация

1984-01-13—Подача