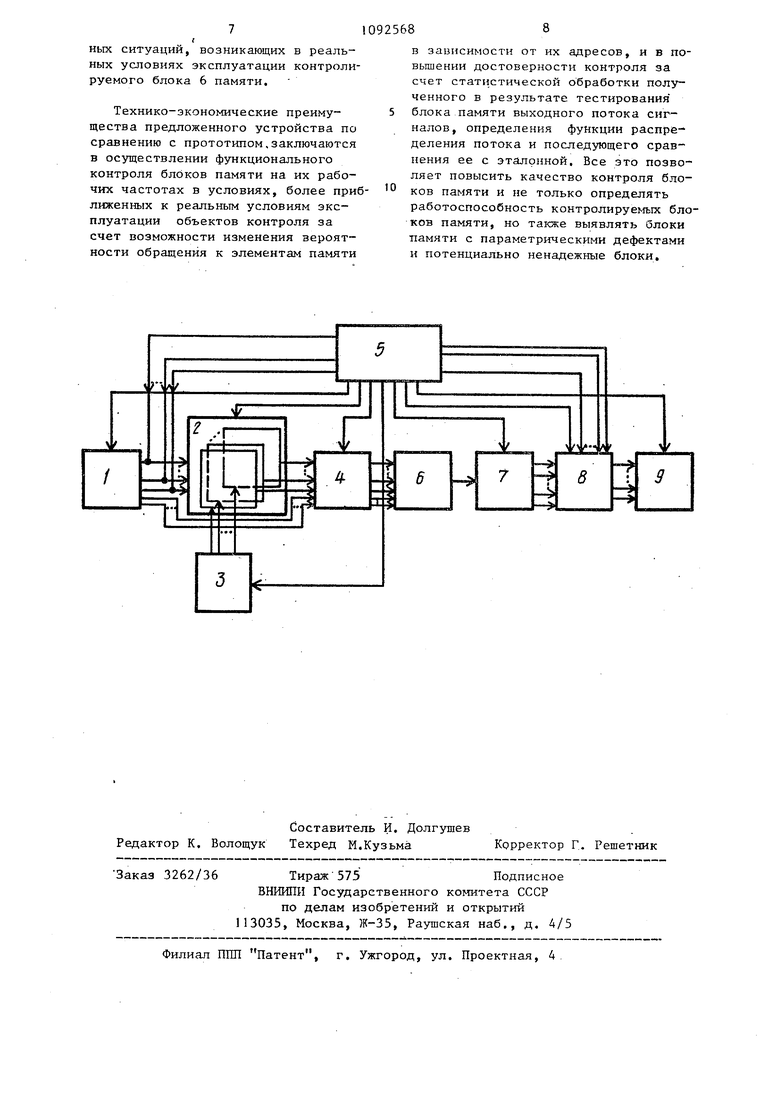

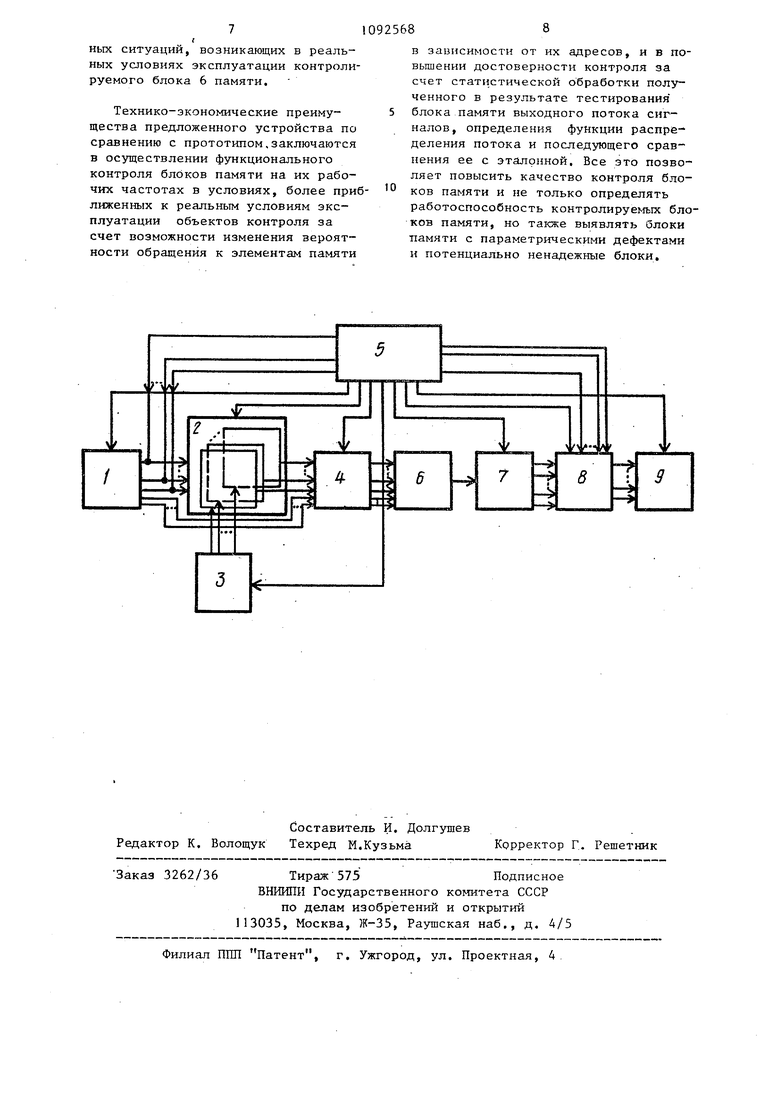

Изобретение относится у. запомина пщм устройствам и, в частности, пре назначено для входного функционального контроля.полупроводниковых опе ративных запоминающих устройств (ОЗУ) с произвольной выборкой. Известно устройство для контроля блоков памяти, содержащее контролируемый блок памяти, блок управления генератор случайных чисел, схему ср,авнения, формирователь кодов, эта лонный блок памяти и датчик временных интервашов, В этом устройстве происходит запись в запоминающие эл менты контролируемого и зталонного блоков памяти случайны с кодов, пост паклдих от генератора случайных чисе через формирователь, а затем считывание информации из обоих блоков и ее сравнение С 1 3. Недостаток данного устройства со стоит в неполном соответствии условий контроля объекта реальным услов ям его работы, что снижает достовер . ность испытания. Кроме того, для по ноге выявления дефектов, связанных с распределением информации в блоке памяти, необходимо многократное повторение циклов записи-считывания, что приводит к увеличению времени контроля. Наиболее близким к изобретению по технической сущности является устройство для контроля памяти, содержащее блок местного управления, входы которого соединены с выходами каналов многоканального генерато ра простейших потоков, выходы - с соответствующими входами блока памяти, а контрольный выход - с первы входом статистического Анализатора, второй вход которого соединен с выходом блока памяти, а выходы - с со ответствукнцнми входами блока сравнения, выходы которого соединены с информационными входам блока индикации, и блок управления, вырабатывающий в соответствии с программой контроля управляющ те сигналы для генератора, блока местного управления, статистического анализатора и блока индикации 2, Работа зтого устройства основана на подаче на адресные, управляющие и информационный входы контролируемой памяти простейших потоков, определении математического ожидания и дисперсии выходной последовательности и их сравнении в рамках установленного допуска, в результате чего делается заключение о годности объекта контроля . Одна1 о в. известном устройстве не предусматривается возможность изменения вероятности обращения к эле-. ментам памяти в зависимости от их адресов, не изменяя при этом экспоненциального характера вероятности обращения. Это приводит к тому, что в случае большой информационной емкости контролируемого блока nai-шти для достижения достаточно высокой достоверности контроля работоспособности запоминающих элементов, вероятность обращения к которым относительно мала, необходима весьма большая длина тестовой последовательности, что приводит к увеличению времени контроля. Кроме того, вызывает значительные трудности определение эталонной величины расхождения математического ожидания и дисперсии выходной последовательности. Цель изобретения - повышение достоверности контроля за счет возможности изменения вероятности обращения к элементам памяти. Поставленная цель достигается тем, что в устройство для контроля памяти, содержащее блок управления, многоканалсьный генератор простейших потоков, блок местного управления, выходы которого являются выходами устройства, блок сравнения и блок индикации, введены блок задания адресов, накопитель и блок статистической обработки, причем адресные входы накопителя соединены с выходами первой группы многоканального генератора простейших потоков и с одними выходами блока управления, информационные входы - с вглходами блока задания адресов, управляющий вход накопителя соединен с первым выходом блока управления, а его выходы - с входами первой группы блока местного управления, входы второй группы которого подключены к выходам второй группы многоканального генератора простейших потоков, а управляюш 1Й вход - ко второму выходу блока управления, информационный вход блока статистической обработки является входом устройства, его управляющий вход соединен с третьим выходом .блока управления, а вы3lходы - с одними входами блока сравнения , другие входы которого подключены к другим выходам блока управления , управляющий вход - к четвертому выходу блока управления, а выходы - ко входам блока индикации, управляющий вход которого соединен с пятым выходом блока управлемия, шестой и седьмой выходы которого подключены соответственно к управляющим входам многоканального генератора простейших потоков и бло ка задания адресов. На чертеже представлена структур ная схема устройства для контроля памяти. Устройство содержит многоканальный генератор 1 простейших потоков, накопитель 2, блок 3 задания адресов, блок 4 местного управления, блок 5 управления. Блок 6 является контролируемым блоком памяти. Устройство также содержит блок 7 статистической обработки, блок 8 сравнения и блок 9 индикации. Адресные входы накопителя 2 соединены с выходами первой группы мно гоканального генератора 1 простейши потоков и с одними выходами блока 5 управления, информационные входы с выходами блока 3 задания адресов, управляющий вход накопителя 2 соеди нен с первым выходом блока 5 управления, а его выходы - с входами пер вой группы блока 4 местного управле ния, входы второй группы которого подключены к выходам второй группы многоканального генератора 1 просте ших потоков, управляющий вход - ко второму выходу блока 5 управления, а выходы - ко входам контролируемого блока 6 памяти, информационный вход блока 7 статистической обра- ботки соединен с выходом контролиру емого блока 6 памяти, его управляющий вход соединен с третьим выходом блока 5 управления, а выходы с одни ми входами блока 8 сравнения, другие входы которого подключены к дру гим выходам блока 5 управления, управляющий вход - к четвертому выход блока 5 управления, а выходы - ко входам блока 9 индикации, управляющий вход которого соединен с пятым выходом блока 5 управления, шестой и седьмой выходы которого подключены соответственно к управляющим вхо дам многоканального генератора 1 пр 4 стейших потоков н блока 3 задания адресов. Устройство работает следующим образом, С помощью органов управления устройства в блоке 5 управления задаются время контроля (время работы многоканального генератора 1 простейших потоков), число повторений цикла раОоты устройства и эталонные данные, предназначенные для сравнения с данными, определяемыми при статической обработке выходного потока, полученного в результате тестироваНИН контролируемого объекта. Блок 5 управления в соответствии с программой контроля вырабатывает управляющ11е сигналы для многоканального генератора 1 простейших потоков, накопителя 2, блока 3 задания адресов, блока 4 местного управления, блока 7 статистической, обработки, блока 8 сравнения и блока 9 индикации, При поступлении управляющего сигнала от блока 5 управления в блоке 3 задания адресов вырабатьшаются и записываются в элементы памяти накопителя 2 коды адресов в определеняой последовательности, которая отражает распределение вероятности обращения к запоминающим элементам контролируемого блока 6 памяти в зависимости от ifx адресов, характерное для реальных условий эксплуатации объекта контроля. При этом сигналы управления режимом считывания в блок 3 задания адресов и режимом записи в накопитель 2 поступают из блока 5 управления, В качестве блока 3 задания адресов может использоваться, например, постоянное запоминающее устройство с записагшыми в определенной последовательности кодами адресов или генератор равномерно распределенных случайных чисел. Накопитель 2 представляет собой оперативное запоминающее устройство, в каждый элемент памяти которого записывается п-разрядный адресный код (п-число адресных входов контролируемого блока 6 памяти, равное числу адресных входов накопителя 2), причем количество элементов памяти накопителя 2 равно количеству запоминающих элементов контролируемого блока 6 памяти. Таким образом, организация накопителя 2 аналогична организации контролируемого блока 6 памяти с той разницей,что в элемент памяти накопителя 2 записывается п-разрядное слово, а в элемент памяти контролируемого блока 6 - один информационный бит, После записи в накопитель 2 кодов адресов управля(яцин сигнал от блока 5 управления запускает многоканальный генератор 1 простейших по токов, вырабатывающий (п+та) независимых простейших потоков, функция распределения каждого из которых выражается как -j . F,(t) - J - е , где А - интенсивность или среднее .число импульсов в единицу времени i-ro потока (i 1 ,2,3,. ,. ,n-hii) . n потоков поступают на адресные входы накопителя 2, а m - на m входов блока 4 местного управления. При этом из блока 5 управления в на копитель 2 поступают управляющие сигналы считывания кодов адресов из накопителя 2. Коды адресов из накопителя 2 и m простейших потоков от генератора 1 поступают на входы блока 4 местного травления для формирования в соответствии с технически№л характеристиками контролируемого блока 6 памя ти временной диаграм адресных и зтаравляющих сигналов (сигналов запи си-считыванияJ выбора микросхемы, информационного сигнала) на контролируемь1й блок 6 памяти. Кроме того, . в блоке 4 местного управления организуется режим строчной регенерации для данамических ОЗУ. Таким образом на Входы контролируемого блока 6 па мяти поступают простейшие потоки адресных и управляющих сигналов в соответствии с требуемой временной диаграммой. Случайный поток дво:ичньгх сигнало с выхода контролируемого блока 6 па мяти поступает на вход блока 7 статической обработки, в :котором проис ходит дискриминация длительностей временных интервалов между импульса ми выходного потока. Блоком 5 управ ления задаются минимальное и максимальное значения для каждой из rpym по которым распределяются величины временных интервалов мзжду импульсами потока, npmieM в данную группу попадает такой интерва.п, величина которого меньше максимальной, но больше мкнимашзной заданных для данной группы Benii4nH. В результате за время контроля блока 6 памяти в блоке 7 статистической обработки накапливается ряд сумм, численно выражающих распределение временных интервалов в зависимости от их длин. Кроме того 5 в блоке 7 подсчитывается общее число импульсов, поступивших за время контроля с выхода контролируемого блока 6 памяти. Исправный блок памяти представляет собой регулярную структуру, поэтому композиция простейших потоков на адресных, информационном и управляющих входах контролируемого блока 6 памяти обуславливает простейший характер выходного потека, при этом функция распределения выходно- . го потока выра кается как F,.t) 1 - .x-t , интенсивность выходного .потока. По истечении времени контроля по сигналу с блока 5 управления данные, полученные в блоке 7 статистической обработки, поступают в блок 8 сравнения, в котором нормируются путем деления на общее число импульсов, поступивших за время контроля с выхода контролируемого блока 6 памяти. Нормированные данные сравниваются в пределах установленного допуска с предварительно заданными значениями, поступающими из блока 5 управления, которые отображают эталонную функцию распределения, и в зависимости от результатов сравнения блоком 8 сравнения на блок 9 индикации вырабатываются сигналы Годен или Брак. Кроме того, по сигналам из блока 5 управления эталонные и нормированные значения поступают из блока 8 сравнения в блок 9 индикшдии.. на экране которого совместно строятся эталонная и полученная функция распределения, Описанный цикл работы предложенного устройства может быть повторен несколько раз. Число повторений задается в соответствии с программой контроля в блоке 5 управления, причем в каждом цикле испытания последовательность занесения кодов адресов в элементы памяти накопитея 2 меняется определенным образом, при этом моделЕ руется ряд возмож7ных ситуаций, возникающих в реальных условиях эксплуатации контролируемого блока 6 памяти. Технико-экономические преимущества предложенного устройства по сравнению с прототипом,заключаются в осуществлении функционального контроля блоков памяти на их рабочих частотах в условиях, более при лиженных к реальным условиям эксплуатации объектов контроля за счет возможности изменения вероятности обращения к элементам памяти в зависимости от их адресов, и в повышении достоверности контроля за счет статистической обработки полученного в результате тестирования блока памяти выходного потока сигналов, определения функции распределения потока и последующего сравнения ее с эталонной. Все это позволяет повысить качество контроля блоков памяти и не только определять работоспособность контролируемых блоков памяти, но также выявлять блоки памяти с параметрическими дефектами и потенциально ненадежные блоки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Устройство для контроля памяти | 1981 |

|

SU982100A1 |

| Устройство для статистического контроля логических блоков | 1983 |

|

SU1173415A1 |

| Устройство для диагностики абонентов вычислительной сети | 1989 |

|

SU1679488A1 |

| Устройство для автоматического контроля больших интегральных схем | 1985 |

|

SU1249518A1 |

| Устройство для тестового контроля цифровых блоков | 1983 |

|

SU1136169A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1166120A1 |

| Устройство для контроля цифровых интегральных схем | 1978 |

|

SU943747A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАМЯТИ, содержащее блок управления, многоканальный генератор простейших потоков, блок местного управления, которого являются выходами устройства, блок сравнения и блок индикации, -отличающееся тем, что, с целью повьшения достоверности контроля за счет возможности изк&нения вероятности обращения к элементам памяти, в него введены блок задания адресов, накопитель и .блок статистической обработки, причем адресные входы накопителя соединены с выходами первой группы многоканального генератора простейших потоков и с одними выходами блока управления, информацноньые входы с выходами блока задания адресов, управляющий вход накопителя соединен с первым выходом блока управления, а его выходы с входами первой группы блока местного управления, входы второй группы которого подключены к выходам второй группы многоканального генератора простейших потоков, а управляющий вход - к второму выходу блока управления, информационный вход блока статистической обработки является входом устройства, его управляющий вход соединен с третьим выходом блока (Л управления, а выходы - с одними вхо дами блока сравнения, другие входы которого подключены к другим выходам блока управления, управлякнций вход - к четвертому выходу блока управления, а выходы - ко входам блока индикации, управляющий вход о со го которого соединен с пятым выходом блока управления, шестой и седьмой выходы которого подключены соотел ветственно к управляющим входам мноО5 гоканального генератора простейших оо потоков и блока задания адресов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля блоков памяти | 1980 |

|

SU940240A1 |

| Солесос | 1922 |

|

SU29A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля памяти | 1981 |

|

SU982100A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-05-15—Публикация

1982-12-28—Подача