(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПАМЯТИ

1

Изобретение относится к запоминающим устройствам, в частности к устройствам для контроля блоков памяти, и может быть использовано для контроля в динамическом режиме оперативных запоминающих устройств (ОЗУ) с произвольной выборкой.

Известны устройства для контроля Сйперативных запоминающее устройств IJ иС2.,0

Одно из известных ОЗУ содержит блок управления, блок сравнения, формирователь кодов, причем вход блока управления соединен с выходом блока сравнения, одна группа входов которого соединена с 5 выходными шинами блока памяти, а вторая группа - с выходами формирователя кодов, входами подключенного к адресным шинам блока памяти i .

К недостаткам этого устройства отно- 20 сится невысокая эффективность качества контроля из-за того, что формируемые в этом устройстве проверочные тесты являются регулярными как по направлению обхода адресов, так и по распределению информапии в накопителе. В реальных же ОЗУ как направление обхода адресов, так и распределение информации в накопителе является произвольным.

Из известных устройств наиболее близким техническим решением к данному изобретению является устройство для контроля блоков памяти, содержащее блок управления, счетчик числа обращений, счет-. чик математических ожиданий, сумматор, генератор случайных чисел, формирователь кодов и схему сравнения, выход которой соединен с входом блока управления, выход блока управления соединен с входом проверямого блока памяти, другой вход которой соединен с выходом формирователя кода, а выход - с входом схемы сравнения .

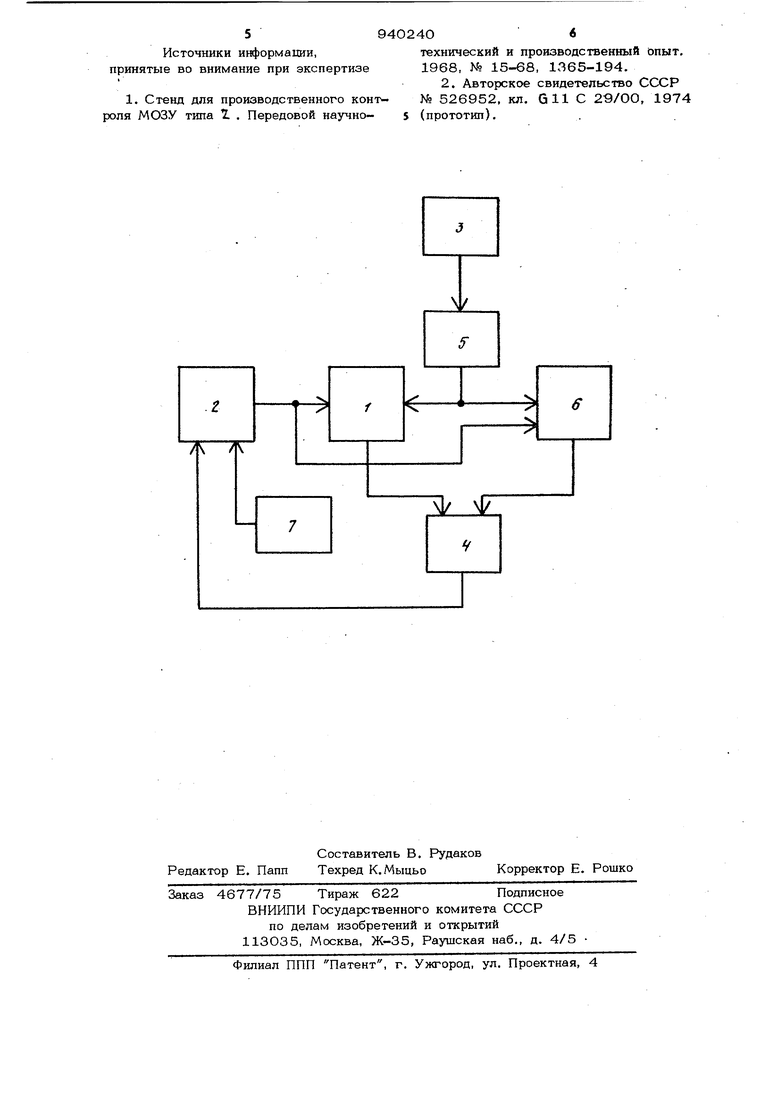

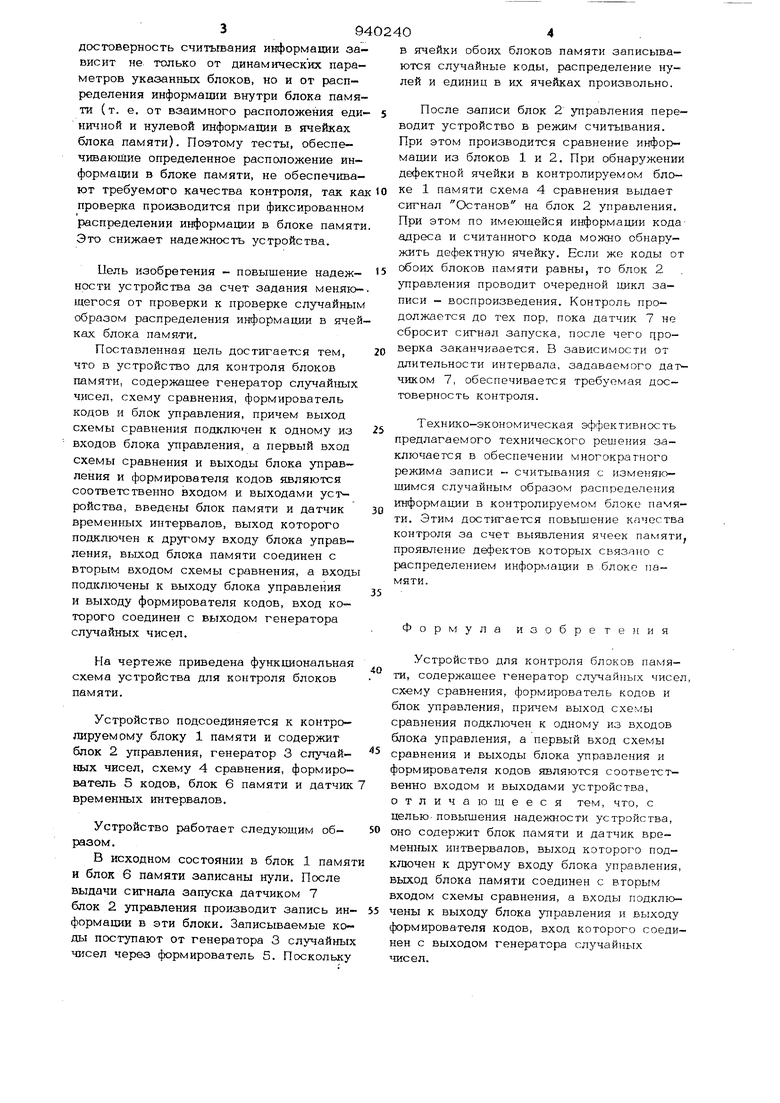

В этом устройстве обеспечивается возможность задания вероятностным методом множества направлений обхода адресов, что повьпиает качество контроля. Однако в существующих интегральных блоках ОЗУ достоверность считывания информации за висит не только от динамических пара метров указанных блоков, но и от рисп- ределения информаш1и внутри блока памя ти (т. е. от взаимного расположения еди ничной и нулевой информации в ячейках блока памяти). Поэтому тесты, обеспечивающие определенное расположение информации в блоке памяти, не обеспечива ют требуемого качества контроля, так к проверка производится при фиксированном распределении информации в блоке памят Это снижает надежность устройства. Цель изобретения - повышение надежности устройства за счет задания меняю щегося от проверки к проверке случайны образом распределения информации в яче ках блока памя-ти. Поставленная цель достигается тем, что Б устройство для контроля блоков памяти, содержащее генератор случайных чисел, схему сравнения, формирователь кодов и блок управления, причем выход схемы сравнения подключен к одному из входов блока управления, а первый вход схемы сравнения и выходы блока управления и формирователя кодов являются соответственно входом и выходами устройства, введены блок памяти и датчик временных интервалов, выход которого подключен к другому входу блока управления, выход блока памяти соединен с вторым входом схемы сравнения, а входы подключены к выходу блока управления и выходу формирователя кодов, вход которого соединен с выходом генератора случайных чисел. На чертеже приведена функциональная схема устройства для контроля блоков памяти. Устройство подсоединяется к контролируемому блоку 1 памяти и содержит блок 2 управления, генератор 3 случай- ных чисел, схему 4 сравнения, формирователь 5 кодов, блок 6 памяти и датчик временных интервалов. Устройство работает следующим об- разом. В исходном состоянии в блок 1 памя и блок 6 памяти записаны нули. После выдачи сигнала запуска датчиком 7 блок 2 управления производит запись ин формации в эти блоки. Записываемые коды поступают от генератора 3 случайных чисел через формирователь 5. Поскольку в ячейки обоих блоков памяти записываются случайные коды, распределение нулей и единиц в их ячейках произвольно. После записи блок 2 управления переводит устройство в режим считывания. При этом производится сравнение информации из блоков 1 и 2. При обнаружении дефектной ячейки в контролируемом блоке 1 памяти схема 4 сравнения выдает сигнал Останов на блок 2 управления. При этом по имеющейся информации кода адреса и считанного кода можно обнаружить дефектную ячейку. Если же коды от обоих блоков памяти равны, то блок 2 управления проводит очередной цикл записи - воспроизведения. Контроль продолжается до тех пор, пока датчик 7 не сбросит сигнал запуска, после чего проверка заканчивается. В зависимости от длительности интервала, задаваемого дат чиком 7, обеспечивается требуемая достоверность контроля. Технико-экономическая эффективность предлагаемого технического решения заключается в обеспечении многократного режима записи - считывания с изменяющимся случайным образом распределе}шя информации в контролируемом блоке памяти. Этим достригается повышение качества контроля за счет выявления ячеек памяти, проявление дефектов которых связано с распределением информагдаи в блоке памяти. Формула изобретения Устройство для контроля блоков памяти, содержащее генератор случайньгх чисел, схему сравнения, формирователь кодов и блок управления, причем выход схемы сравнения подключен к одному из входов блока управления, а первый вход схемы сравнения и выходы блока управления и формирователя кодов являются соответственно входом и выходами устройства, отличающееся тем, что, с целью- повышения надежности устройства, оно содержит блок памяти и датчик временных иптвервалов, выход которого подключен к другому входу блока управления, выход блока памяти соединен с вторым входом схемы сравнения, а входы подключены к выходу блока управления и выходу формирователя кодов, вход которого соединен с выходом генератора случайных чисел. Источники информации, принятые во внимание при экспертизе 1. Стенд для производственного кон роля МОЗУ типа 7. . Передовой научно06технический и производственный опыт, 1968, № 15-68, 1365-194, 2. Авторское свидетельство СССР № 526952. кл, G11 С , 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков памяти | 1974 |

|

SU526952A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1003150A1 |

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1358003A1 |

| Вероятностная вычислительная машина | 1986 |

|

SU1455344A1 |

| Устройство для контроля памяти | 1982 |

|

SU1092568A1 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1283859A1 |

| Устройство для контроля цифровыхОб'ЕКТОВ | 1978 |

|

SU798844A1 |

| Устройство для контроля блоков памяти | 1980 |

|

SU918975A1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU951408A1 |

| Устройство для перадачи информации | 1990 |

|

SU1711217A1 |

Авторы

Даты

1982-06-30—Публикация

1980-12-24—Подача