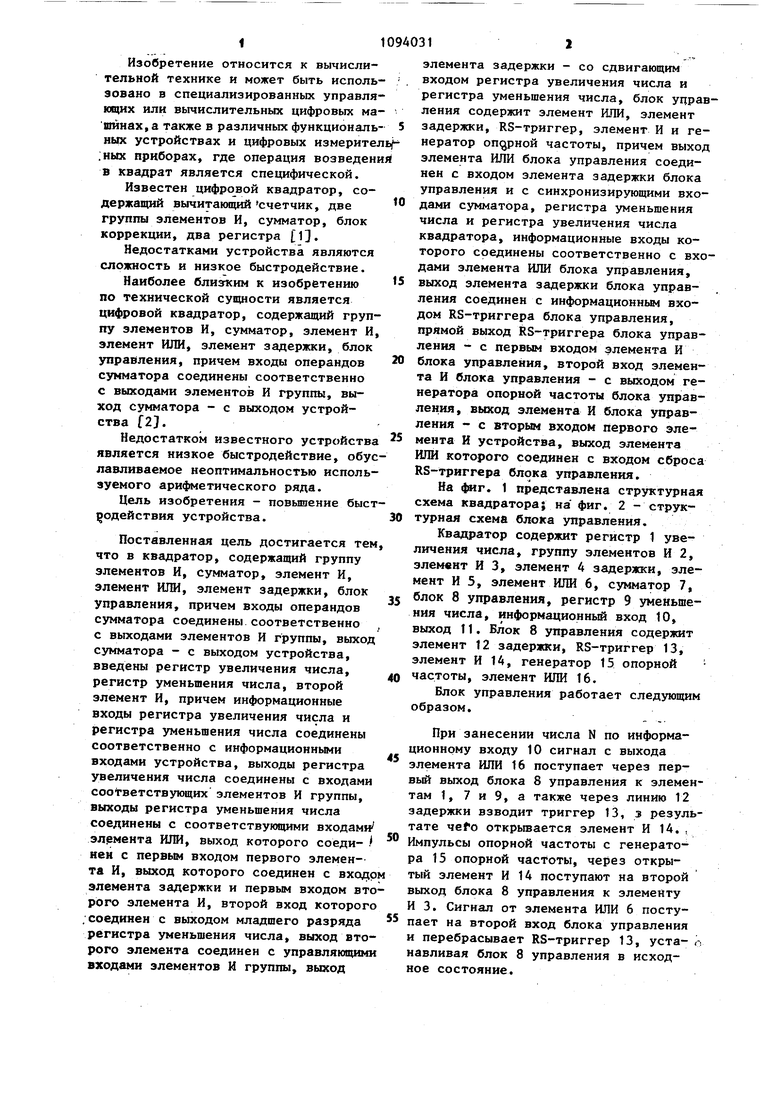

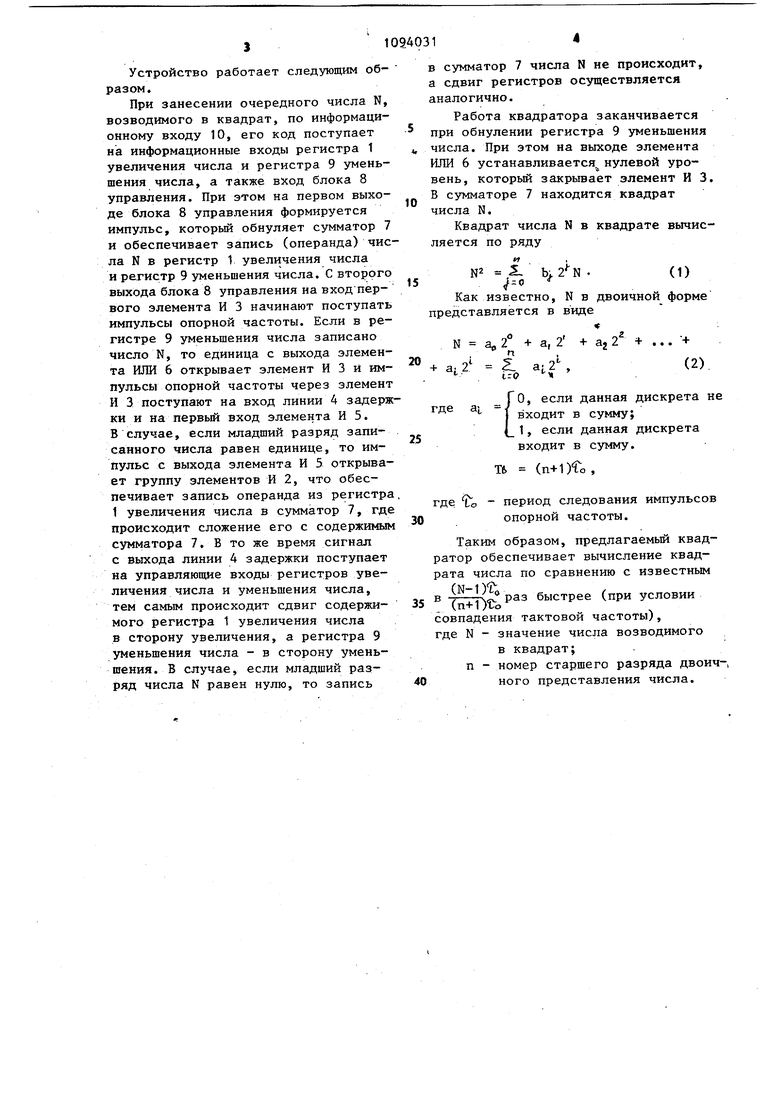

Изобретение относится к вычислительной технике и может быть испольэовано в специализированных управляющих или вычислительных цифровых машинах, а также в различных функциональных устройствах и цифровых измерител ;ных приборах, где операция возведени в квадрат является специфической. Известен цифровой квадратор, содержащий вычитающийсчетчик, две группы элементов И, сумматор, блок коррекции, два регистра 1. Недостатками устройства являются сложность и низкое быстродействие. Наиболее близким к изобретению по технической сущности является цифровой квадратор, содержащий группу элементов И, сумматор, элемент И элемент ИЛИ, элемент задержки, блок управления, причем входы операндов сумматора соединены соответственно с выходами элементов И группы, выход сумматора - с выходом устройства f2. Недостатком известного устройства является низкое быстродействие, обус лавливаемое неоптимальностью используемого арифметического ряда. Цель изобретения - повьшение быст родействия устройства. Поставленная цель достигается тем что в квадратор, содержащий группу элементов И, сумматор, элемент И, элемент ИЛИ, элемент задержки, блок управления, причем входы операндов сумматора соединены соответственно с выходами элементов И группы, выход сумматора - с выходом устройства, введены регистр увеличения числа, регистр уменьшения числа, второй элемент И, причем информационные входы регистра увеличения числа и регистра уменьшения числа соединены соответственно с информационными входами устройства, выходы регистра увеличения числа соединены с входами соответствующих элементов И группы, выходы регистра уменьшения числа соединены с соответствующими входами элемента ИЛИ, выход которого соедииен с первым входом первого элемента И, выход которого соединен с вход элемента задержки и первым входом вт рого элемента И, второй вход которог .соединен с выходом младшего разряда регистра уменьшения числа, выход вто рого элемента соединен с управляющим входами элементов И группы, выход элемента задержки - со сдвигающим входом регистра увеличения числа и регистра уменьшения числа, блок управления содержит элемент ИЛИ, элемент задержки, RS-триггер, элемент И и генератор опорной частоты, причем выход элемента ИЛИ блока управления соединен с входом элемента задержки блока управления и с синхронизирующими входами сумматора, регистра уменьшения числа и регистра увеличения числа квадратора, информационные входы которого соединены соответственно с входами элемента ИЛИ блока управления, выход элемента задержки блока управления соединен с информационньв) входом RS-триггера блока управления, прямой выход RS-триггера блока управления - с первым входом элемента И блока управления, второй вход элемента И блока управления - с выходом генератора опорной частоты блока управления, выход элемента И блока управления - с вторым входом первого элемента И устройства, выход элемента ИЛИ которого соединен с входом сброса RS-триггера блока управления. На . 1 представлена структурная схема квадратора; на фиг. 2 - структурная схема блока управления. Квадратор содержит регистр 1 увеличения числа, группу элементов И 2, элемент ИЗ, элемент 4 задержки, элемент И 5, элемент ИЛИ 6, сумматор 7, блок 8 управления, регистр 9 уменьшения числа, информационный вход 10, выход t1. Блок 8 управления содержит элемент 12 задержки, RS-триггер 13, элемент И 14, генератор 15 опорной частоты, элемент ИЛИ 16. Блок управления работает следующим образом. При занесении числа N по информационному входу 10 сигнал с выхода элемента ИЛИ 16 поступает через первый выход блока 8 управления к элементам 1, 7 и 9, а также через линию 12 задержки взводит триггер 13, з результате открывается элемент И 14. , Импульсы опорной частоты с генератора 15 опорной частоты, через открытый элемент И 14 поступают на второй выход блока 8 управления к элементу И 3. Сигнал от элемента ИЛИ 6 поступает на второй вход блока управления и перебрасывает RS-триггер 13, уста- о навливая блок 8 управления в исходное состояние.

Устройство работает следующим образом.

При занесении очередного числа N, возводимого в квадрат, по информационному входу 10, его код поступает на информационные входы регистра 1 увеличения числа и регистра 9 уменьшения числа, а также вход блока 8 управления. При этом на первом выходе блока 8 управления формируется импульс, который обнуляет сумматор 7 и обеспечивает запись (операнда) числа N в регистр 1 увеличения числа и регистр 9 уменьшения числа. С второго выхода блока 8 управления на вход первого элемента И 3 начинают поступать импульсы опорной частоты. Если в регистре 9 уменьшения числа записано число N, то единица с выхода элемента ИЛИ 6 открывает элемент И 3 и импульсы опорной частоты через элемент И 3 поступают на вход линии 4 задержки и на первьй вход элемента И 5. В случае, если младший разряд записанного числа равен единице, то импульс с выхода элемента И 5 открывает группу элементов И 2, что обеспечивает запись операнда из регистра 1 увеличения числа в сумматор 7, где происходит сложение его с содержимым сумматора 7. В то же время сигнал с выхода линии 4 задержки поступает на управляющие входы регистров увеличения числа и уменьшения числа, тем самым происходит сдвиг содержимого регистра 1 увеличения числа в сторону увеличения, а регистра 9 уменьшения числа - в сторону уменьшения. В случае, если младший разряд числа N равен нулю, то запись

в сумматор 7 числа N не происходит, а сдвиг регистров осуществляется аналогично.

Работа квадратора заканчивается при обнулении регистра 9 уменьшения числа. При этом на выходе элемента ИЛИ 6 устанавливается нулевой уровень, который закрывает элемент И 3. В сумматоре 7 находится квадрат числа N.

Квадрат числа N в квадрате вычисляется по ряду

Д b,. (1)

N2

Как известно, N в двоичной форме представляется в виде

« N а 2° + а, 2 + а 2 + ...+

(2)

2

а-. 2

+ а

i:0 К

О, если данная дискрета не

где входит в сумму; 1, если данная дискрета входит в сумму.

Т6 (п+1)Го ,

to

- период следования импульсов

где опорной частоты.

Таким образом, предлагаемый квадратор обеспечивает вычисление квадрата числа по сравнению с известным

35 7-г(т- Р быстрее (при условии совпадения тактовой частоты), где N - значение числа возводимого

в квадрат;

п - номер старшего разряда двоич-, 40 ного представления числа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство по модулю | 1985 |

|

SU1285468A1 |

| Матричное устройство для возведения в квадрат | 1989 |

|

SU1686439A1 |

| Устройство для вычисления функции @ | 1984 |

|

SU1166102A1 |

| Арифметическое устройство | 1988 |

|

SU1578708A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Квадратор | 1985 |

|

SU1258826A2 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Устройство для извлечения корня четвертой степени | 1985 |

|

SU1262487A1 |

| Режекторный фильтр | 1987 |

|

SU1429293A2 |

КВАДРАТОР, содержащий группу элементов И, сумматор, элемент И, элемент ИЛИ, элемент задержки, блок управления, причем входы операндов сумматора соединены соответственно с выходами элементов И группы, вход сумматора соединен с выходом квадратора, отличающийся тем, что, с целью повышения быстродействия, в него введены регистр увеличения числа, регистр уменьшения числа, второй элемент И, причем информационные входы регистра увеличения числа и регистра уменьшения числа соединены соответственно с информационными входами устройства, выходы регистра увеличения числа соединены с входами соответствующих элементов И группы, ,выходы регистра уменьшения числа соединены с соответствующими входами элемента ИЛИ, выход которого соединен с первым входом первого элемента И, выход которого соединен с входом элемента задержки и первым входом второго элемента И, второй вход которого соединен с выходом младшего разряда регистра уменьшения числа, выход второго элемента И соединен с управляющими входами элементов И группы, выход элем.ента задержки - со сдвигающим входом регистра увеличения числа и регистра уменьшения числа, блок управления содержит элемент И, элемент задержки, RS-триггер, элемент ИЛИ и генератор опорной частоты, причем выход элемента ИЛИ блока управления соединен с входом элемента задержки блока управления и с синхронизирующиКЛ ми входами сумматора, регистра уменьшения числа и регистра увеличения числа, квадратора, информационные входы которого соединены соответственно с входами элемента ИЛИ блока . управления, выход элемента задержки блока управления соединен с информа 1,ионным входом RS-триггера блока упсо 4 равления, прямой выход RS-триггера блока управления соединен с первым входом элемента И блока управления, второй вход элемента И блока управ:о ления - с выходом генератора опорной частоты блока управления, выход элемента И блока управления - с вторым входом первого элемента И устройства, выход элемента ИЛИ которого соединен с входом сброса RS-триггера блока управления.

Авторы

Даты

1984-05-23—Публикация

1983-01-21—Подача