Изобретение относится к автоматике и вычислительной технике и может быть использовано при построени двоично-десятичных преобразователей Известен преобразователь двоичнодесятичного кода в двоичный, содержащий регистр числа, блок управления переключатель эквивалентов, первое и второе запоминающее устройства хранения эквивалентов, два сукматора и два регистра, группу элементов И и счетчик переносов 1. Недостаток преобразователя - низкое быстродействие, связанное с последовательньм принципом работы, а также наличие сложного блока управления, i Наиболее близким к предлагаемому по технической сущности является преобразователь двоично-десятичных чисел в двоичные, содержащий регистр тетрады, переключатель эквивалентов первый блок хранения двоичных эквивалентов, накапливающий сумматор, выход которого является выходом преобразователя, а первый вход соединен с выходом первого блока хранения двоичных эквивалентов, информационный вход регистра тетрады соединен с информационным входом преобразователя, управляющий вход которого соединен с управляющими входами регистра тетрады и переключателя эквивалентов 2 . Кроме того, данный преобразователь содержит блок управления и блок сдвига. Недостаток преобразователя - низкое быстродействие, связанное с необходимостью трех тактов для преобразования одного десятичного разряда, и наличие сложного блока управления. Цель изобретения - увеличение быстродействия преобразователя и его упрощение. Поставленная цель достигается д счет того, что в преобразов-атель, двоично-десятичного кода в двоичный, содержащий регистр тетрады, переключатель эквивалентов, первый блок хранения двоичных эквивалентов, накапливающий сумматор, выход которого является выходом преобразователя, а первый вход соединен с выходом первого блока хранения двоичных эквивалентов, информационный вход регистра тетрады соединен с информационным входом преобразователя, управляющий вход которого соединен с управляющими вxoдa ш регисара тетрады и переключателя эквивалентов, введен второй блок хранения двоичных эквивалентов, два младших разряда адресного входа которого соединены с выходами двух стариих разрядов регистра тетрады, .stfKOjya двух младших разрядов которого соединены с двумя младшими раэрядаАШ (дресного входа первого блока хранения двоичных эквивалентов, старшие разряды адресного входа первого и второго блоков хранения двоичных эквивалентов соединены с выходами переключателя эквивалентов, выход второго блока, хранения двоичных эквивалентов соединен со. вторым входом накаплившощегр сумматора ..

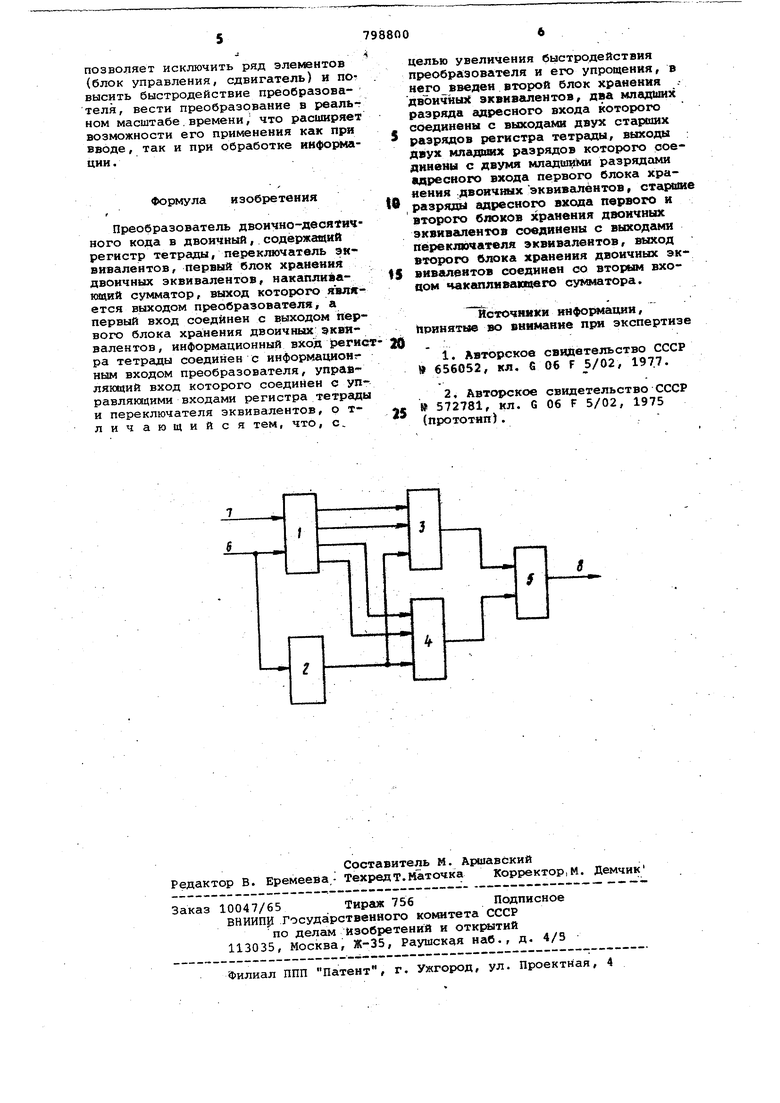

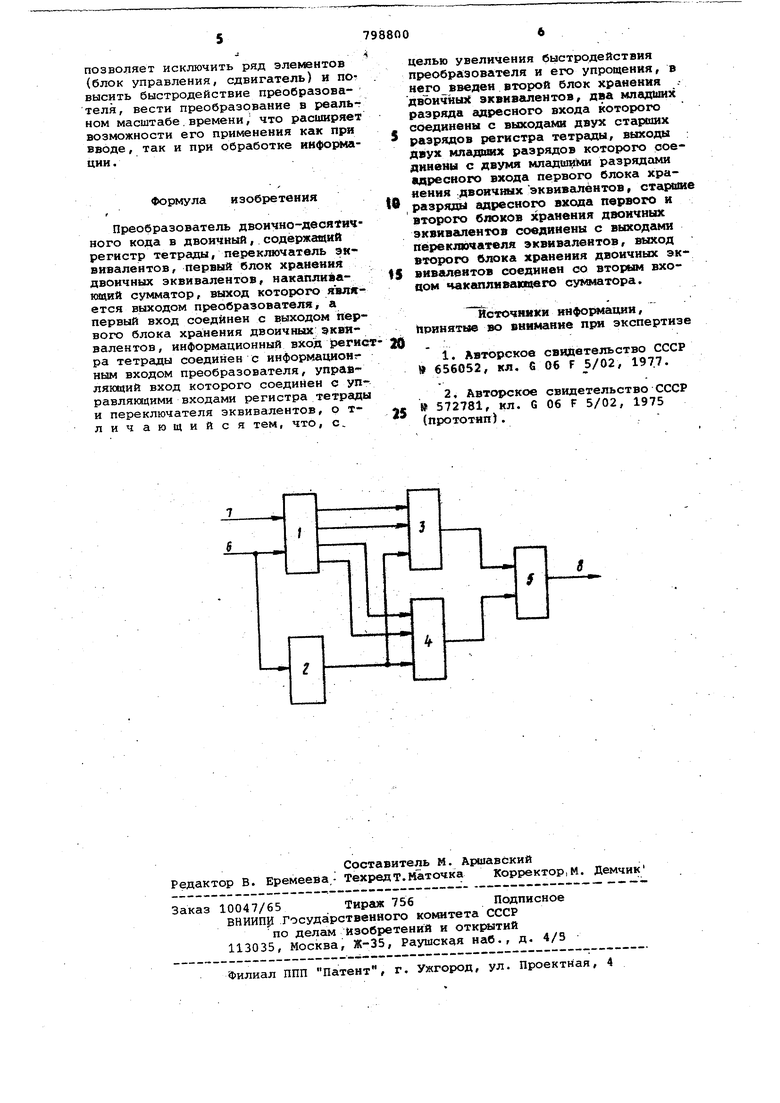

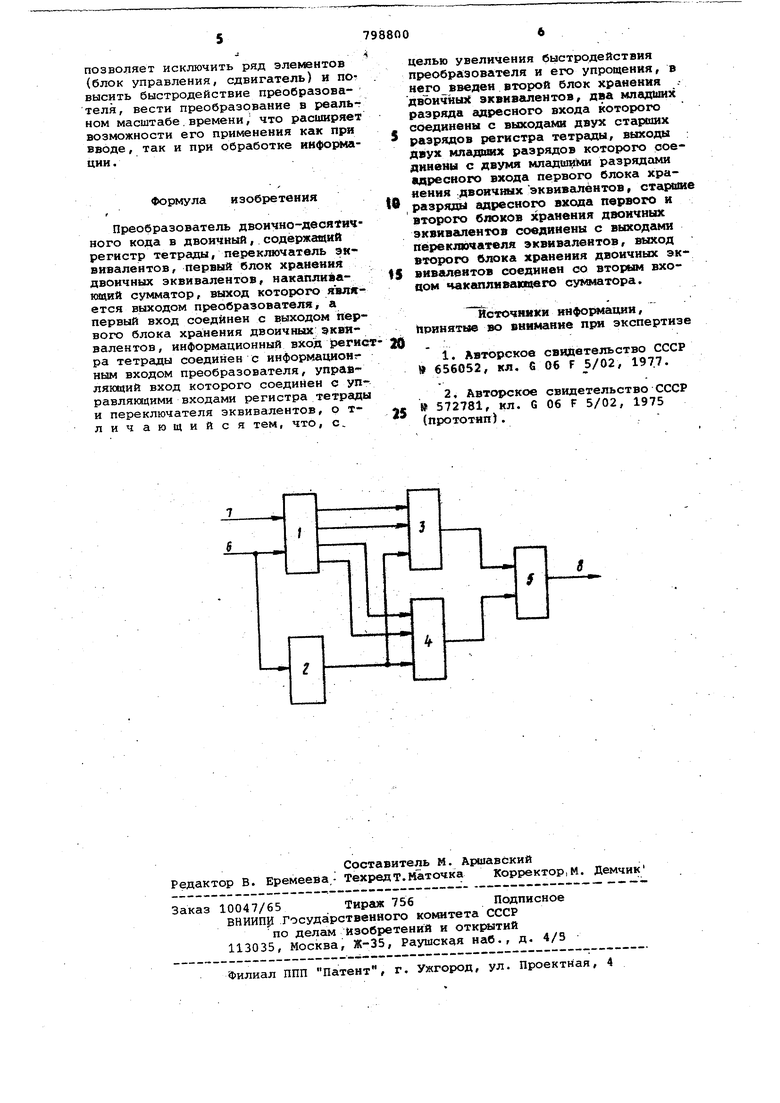

На чертеже представлена блок-схема предлагаемого преобразователя.

Преобразователь содержит регистр .1 тетрада, выполненный по схеме с параллельным приемся, информации,переключатель 2 эквивалентов, который может быть выполнен, например, на двоичном счетчике, пердый 3 и второй 4 блоки хранения двоичных эквивалентов, выполнейиые, нап{жмер, в виде полупроводниковых запоминашцнх устройств или диодных шифраторов, накапливающий сумматор 5, управляющий вход 6, информационный вход 7 и шосод 8 двоично-десятичного преобразователя. Первый и второй разряды аахояа регистра 1 тетрады соединены, соответственноt с первым и вторым ёщресншш входами первого 3 блока хранения дЬоичных эквивалентов, третий и четвертый разряды выхода регистра i тетрада соединены с перsoM и вторым адресными входами второго 4 блока хранё ия двоичных эквивалентов. Число разярдов переключателя 2 эквивалентов определяется количеством десятичных разрядов преобразуемого числа. Выход переключа. теля 2 экаивалентов подключен к старшим разрядам адресных входов первого 3 и второго 4 блоков хранения двоичных эквивалентов. Выходы первого 3 И второго 4 блоков хранения двоичных эквивалентов соединены, соответственно, с первым и вторым входами накапливающего сумматора 5. Количество двоичных разрядов на выходе первого 3 и второго 4 блоков хранения двоичных эквивалентов, а также разрядность накапливающего сумматора 5 определяется числом двоичных разрядов, содержащихся в двоичном эквиваленте старшего разряда:преобразуемого десятичного числа.

Предлагаемый преобразователь работает следующим образом. .

Преобразуемое число в двочино-десятичном коде через вход 7 поразрядно поступает, на вход регистра 1 тетрады. Приэтом каждый разряд исходнго числа представлен в виде двух слгаемых (А + в) , где А может быть любым из чисел 1, 2 и 3, а В числом 4 или 8,

К - номер десятичного разряда.

Одновременно с подачей кода на вход 6 на управлякиций вход регистра 1 тетрады и счетный вход переключателя 2 эквивалентов поступает управляющий импульс. Двоично-десятичный код преобразуемого числа запоминается на регистре 1 тетрады, а на е го выходе фор -ируются млгщшие раз ряды адресов выбора двоичных эквивалентов слагаемых преобразуемого разряда, где А может быть представлено двоичным кодом 10, 01 и 11, В - двоичньм кодом 10, 01. На выход переключателя 2 эквивалентов формирются старшие разряды адресов. Таким образом, адрес двоичного эквивалента первого слагаемого определяется номерюм разряда десятичного числа и двумя младшими двоичными разрядами числового значения преобразуемой цифры, а адрес двоичного эквивалента второго слагаемого определяется номером разряда и двумя старшими двоичньами разрядами преобрзуемой цифры. Первый и второй адреса выбора двоичных эквивалентов поступают на входы соответственно, первого 3 и второго 4 блоков хранения двоичных эквивалентов. Двоичные эквиваленты первого слагаемого хранятся в первом 3 блоке хранения двоичных эквивалентов (три двоичных эквивалента на десятичный разряд преобразуемого числа), двоичные эквиваленты второго слагаемого хранятся во втором 4 блоке хранения двоичных эквивалентов (два двоич 1ых эквивалента на десятичный разряд).

Выбранные двоичные эквивален. в виде слагаекьк А 10 и В 10 поступают параллельным кодом на вход накапливаквдего сумматора 5. Преобразование одного двоично-десятичного разряда производится за один так Подобным же образом происходит преобразование каждого последукхцего двоично-десятичного разряда, до тех пор, пока не будут преобразованы все двоично-десятичные разряды исходного числа, а в накапливающем сумматоре 5 не сформируется искомое двоичное число, которое считывается с выхода преобразователя 8. Общее время преобразования (Т) К-разрядного двоично-десятичного числа определяется выражением Т K-t, где t - длительность такта.

Использование второго 4 блока хранения двоичных эквивалентов и разделение на две функциональные части регистра 1 тетрады в совокупности с новыми связями упрощает программу управления преобразованием. позволяет исключить ряд элементов (блок управления, сдвигатель) и повысить быстродействие преобразователя, вести преобразование в реаль-г ном масштабе.времени, что расширяет возможности его применения как при вводе, так и при обработке иифО1 «И1ции. Формула изобретения - . Преобразователь двоично-десятиЧного кода в двоичный, содержаздий регистр тетрады, перекгаочатвль эквивалентов , Первый блок хранения двоичных эквивалентовf накапливающий сумматор, выход которого явлЖется выходом преобразователя, а первый вход соединен с выходом первого блока хранения двоичных эквивалентов, информационный вход регис ра тетрады соединен с информационг ным входом преобразователя, управляющий вход которого соединен с управляющими входами регистра тетрады и переключателя эквивалентов, о тлич ающийся тем, что, с целью увеличения быстродействия преобразователя и его упрощения, в него введен второй блок хранения двоичныя эквивалентов, два младишх разряда адресного входа которого соединены с выходами двух старших разрядов регистра тетрады, выходы ; двух младьтх разрядов которого соедииены с двумя младшими разрядами ядресвого входа первого блока хра«еиия двоичных эквивалентов, старшие разряды адресного входа первого и второго хранения двоичных эквивалентов соединены с выходами переключателя эквивалентов, выход второго блока хранения двоичных эквивалентов соединен со вторым входом накапливающего сумматора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 656052, кл. S 06 F 5/02, 1977. 2, Авто1 ское свидетельство СССР 572781, кл. G 06 F 5/02, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283978A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU883893A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1569993A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1285604A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

Авторы

Даты

1981-01-23—Публикация

1979-04-05—Подача