(Л

ю

00

PI/K/

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных ЭВМ для построения преобразователей больших потоков двоичной и двоично-десятичной информации.

Цель изобретения - расширение функциональных возможностей за счет обеспечения преобразования целых чисел и повышение быстродействия.

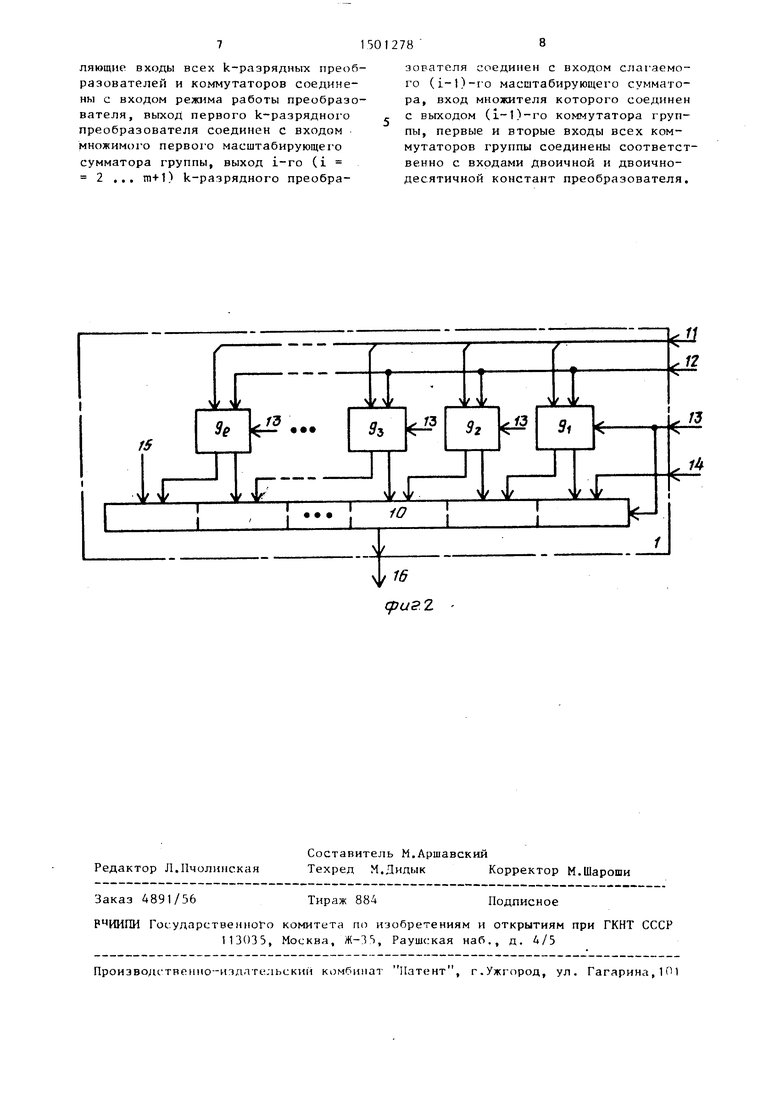

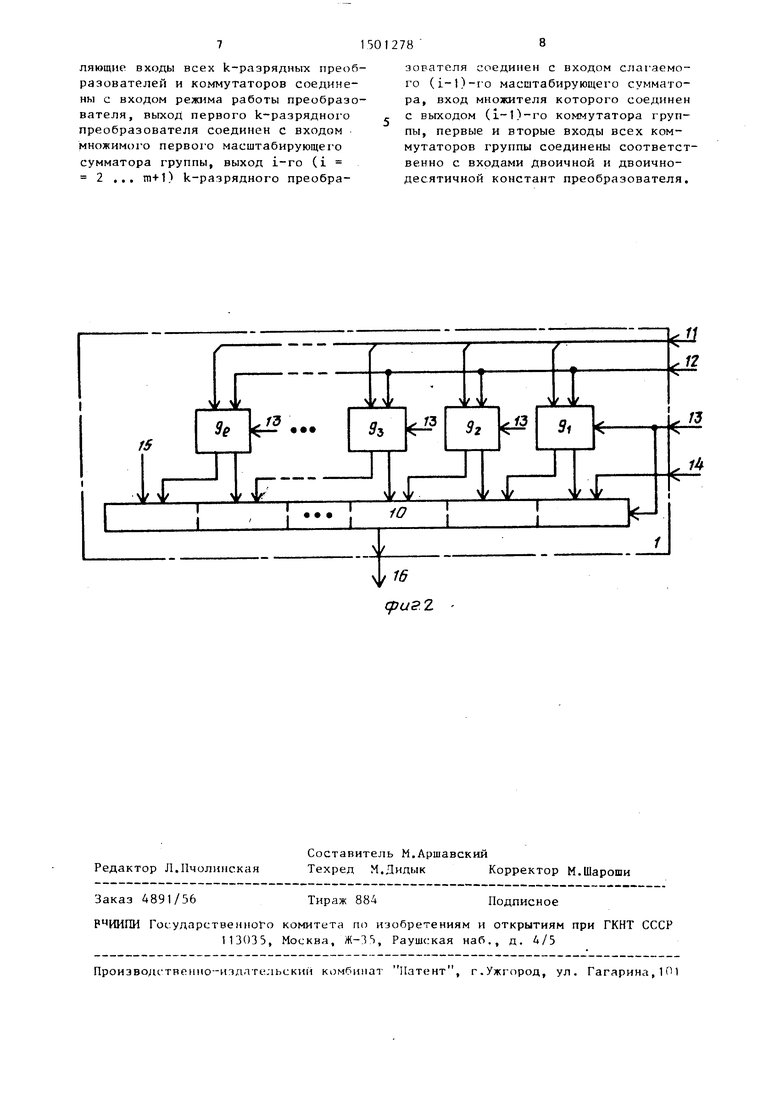

На фиг. 1 приведена блок-схема предлагаемого преобразователяJ на фиг. 2 - структурная схема одного из вариантов реализации масштабирующего сумматора.

Реверсивный преобразователь двоично-десятичного кода в двоичный содержит масштабирующие сумматоры 1 - 1 k-разрядные преобразователи 2 - m + i коммутататоры 3 - 3, информационные входы 4, - преобразуемых групп разрядов, вход 5 двоично- десятичной константы, вход 6 двоичной константы, вход 7 режима работы и выход 8 преобразователя.

Каждый масштабирующий сумматор 1 содержит узлы умножения, сумматор 10, вход 11 множимого, вход 12 множителя, управляющий вход 13, вход 14 слагаемого и вход 15 логического нуля.

В основу работы преобразователя положен следующий принцип.

При преобразовании двоично-деся- гичного кода в двоичный исходный п- разрядный код разбивается на группы по k десятичных цифр в каждой. Преобразование происходит по схеме Гор- нера, т.е. первая, самая старшая, группа разрядов.преобразуется в двоичный код и умножается на двоичную константу, значение KOTopofi определяется значением k. Так, например, при k 1 двоичная константа равна 1010, при k .2 константа равна 1100100 и т.д. К получившемуся произведению прибавляется двоичное значение соседней, младшей, группы десятичных разрядов. Результат суммирования опять умножается на двоичную константу и суммируется с двоичным значением следующей, более младшей, группы десятичных разрядов и т.д. до тех пор, пока не будет под- суммировано двоичное значение самой младшей группы десятичных разрядов. Преобразование из двоичного кода в двоично-десятичный происходит

аналогичным образом, но все действия выполняются в десятичной системе счисления. Значение двоично-десятичс ной константы в этом случае также зависит от количества двоичных разрядов в группах р. Так, например, при р 3 двоичио-десятичная константа равна 8, при р 6 константа

10 равна 64 и т.д.

В каждом из масштабирующих сумматоров могут выполняться операции над числами в двоичном и двоично- десятичном кодах. При преобразова5 НИИ в двоичный код они настраиваются управляющим потенциалом с входа 7 преобразователя на обработку информации в двоичном коде, а при преобразовании в двоично-десятичный код -0 на обработку информации в двоично- десятичном коде. На узлах умножения образуется в двухрядном коде произведение некоторого промежуточного значения преобразуемогсЗ

25 числа, поступающего с входа 11 множимого сумматора 1, на константу, поступающую с его входа 12 множителя. Сумматор 10 осуществляет сворачивание двухрядного кода получен30 ного произведения к однорядному.

При этом через его свободный младший вход 14 поступает и суммируется значение соседней, младшей, группы разрядов преобразуемого числа, а через

35 свободный старший вход - значение О с входа 15 преобразователя. Поступающий с входа 13 масштабирующего сумматора управляющий потенциал обеспечивает функционирование узлоь 40 Jумножения и сумматора 10 в соответствующем коде.

k-Разрядные преобразователи 2 - 2,, предназначены для преобразования из двоично-десятичного кода в

45 двоичньш и наоборот значений групп разрядов, поступающих с входов 4 - 4 , . При k 1 и р 3 необходимость в преобразователях отпадает. Управление работой преобразоватеJQ лей „+, осуществляется потенциалом с входа 7 устройства.

Коммутаторы 3 - 3 предназначены для передачи на входы множителя сумматоров 1, - 1 „ значений либо двоич55 но-десятичных (с входа 5 устройства), либо двоичных констант (с входа 6 устройства). Управление работой коммутаторов осуществляется потенциалом с входа 7 преобразователя.

Допустим, что каждый масштабирующий сумматор выполнен таким образом, что множимое в нем умножается на два десятичных разряда или на восемь двоичных разрядов множителя, а количество масштабирующих сумматоров равно трем. Тогда максимальное количество преобразуемых десятичных разрядов равно 8, а максимальное количество двоичных разрядов - 24.

Рассмотрим сначала преобразование из двоично-десятичного кода в двоичный. Пусть преобразуемое число равно 98356528, Перед началом выполнения операции на входах 4, 4, 4 и 4 устанавливаются двоично-десятичные значения соответственно 98, 35, 65 и 28. Управляющий потенциал с входа 7 режима работы устройства настраивает масштабирующие сумматоры 1, - 1 на обработку двоичных кодов, преобразователи - на преобразование в двоичный код, а коммутаторы 3 - Зз - на передачу двоичных конс- тант 1100100 с входа 6 двоичных констант преобразователя. В масштабирующем сумматоре 1 преобразованное в преобразователе 2 , в двоичный код значение 98 умножается на двоичную константу, одновременно прибавляется двоичное значение числа 35, сформированное на выходе преобразователя 2. С выхода масштабирующего сумматора 1 первый промежуточный результат преобразования поступает на вход множимого блока Ц, 1 де умножается на двоичную константу, к произведению прибавляется двоичное значение соседней, младшей, пары десятичных цифр 65, образованное на выходе преобразователя 2. Второй промежуточный результат в масштабирующем сумматоре 1 умножается на двоичную константу, к произведению прибавляется двоичное значение числа 28, полученное на выходе преобразователя 2, с выхода масштабирующего сумматора 1 считывается окончательный двоичный результат.

При преобразовании из двоичного в двоично-десятичный код на входе 7 преобразователя устанавливается управляющий потенциал, настраивающий масштабирующие Сумматоры 1 - 1 на Обработку двоично-десятичных кодов,

преобразователи 2 - 2 - на преобразование из двоичного кода в двоично-десятичный, коммутаторы 3 i - 3 j на передачу двоично-десятичных констант 64 с входа 5 устройства. На каждый из входов подается по шесть двоичных разрядов преобразуемого числа (на вход 4 - самые старшие шесть разрядов, на вход 4. - соседние, младшие, шесть разрядов и т.д.). После срабатывания масштабирующих сум.маторов 1 - 1 .J на выходе 8 образуется двоично-десятичный код преобразованного числа.

Формула изобретения

15

5

Реверсивный преобразователь двоично-десятичного кода в двоичный, содержащий группу масштабирующих сумматоров, вьсход каждог о масштабирую0 цего сумматора выходного кода группы, (Кроме последнего, соединен с входом множимого соседнего старшего масштабирующего сумматора группы, выход последнего масштабирующего сумматора

5 является информационным выходом преобразователя, вход режима работы которого соединен с управляющими входами всех масштабирующих сумматоров группы, причем каждый масштабирующий сум0 матор состоит из умножителя ц сумматора, первьй информационный вход которого соединен с выходом умножителя, второй информационный вход сумматора и вход умножителя являются соответственно входами слагаемого и множителя масштабирующего сумматора группы, управляющий вход которого соединен с управляющими входами сумматора и умножителя, о т л и ч а юд ш и и с я тем, что, с целью расширения функциональных возможностей за счет обеспечения преобразования целых чисел и повьш ения быстродействия, в него введены группы-коммус таторов и группу k-разрядных преобразователей, причем группы масштабирующих сумматоров и коммутаторов содержат по m г 1 блоков, где

Q п - число разрядов выходного кода, а k - число разрядов входного кода, обрабатываемых одним масштабирующиь сумматором, а группа k-разрядных преобразователей состоит из ()

с блоков, информационные входы первого и второго k-разрядкых преобразователей соединены соотяетственно с ин- форма1(ионными входами первой и второй групп преобразователя, а управляющнр входы всех k-раэрядных преобразователей и коммутаторов соединены с входом режима работы преобразователя, выход первого k-разрядного преобразователя соединен с входом множимого первого масштабирующего сумматора группы, выход i-ro (i 2 ,., tn+1) k-разрядного преобразователя соединен с входом слагаемого (i-l)-ro масштабирующего сумматора, вход множителя которого соединен с выходом (1-1)-го коммутатора группы, первые и вторые входы всех коммутаторов группы соединены соответственно с входами Двоичной и двоично- десятичной констант преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕВЕРСИВНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА В ДВОИЧНЫЙ | 1990 |

|

RU2022467C1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1624698A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для преобразования двоично-десятичного кода в двоичный | 1985 |

|

SU1300641A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Устройство для умножения | 1987 |

|

SU1509875A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения преобразователей больших потоков двоичной и двоично-десятичной информации. Целью изобретения является расширение функциональных возможностей за счет обеспечения преобразования целых чисел и повышение быстродействия. Поставленная цель достигается за счет того, что в реверсивный преобразователь двоично-десятичного кода в двоичный, содержащий группу масштабирующих сумматоров 1, дополнительно введены группа к-разрядных преобразователей 2 и группа коммутаторов 3. 2 ил.

W сриг2

| Красноголовый Б.Н., Шпилевой Б.Н | |||

| Преобразователи кодов | |||

| - Минск: Изд-во БГУ, 1983, с | |||

| Транспортер для перевозки товарных вагонов по трамвайным путям | 1919 |

|

SU105A1 |

| Преобразователь кода дробного числа из одной системы счисления в другую | 1986 |

|

SU1378064A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-08-15—Публикация

1988-01-06—Подача