о ю о о

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоично-десятичного кода в двоичный код и обратно | 1990 |

|

SU1755375A1 |

| Реверсивный преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1501278A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1649672A1 |

| РЕВЕРСИВНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА В ДВОИЧНЫЙ | 1990 |

|

RU2022467C1 |

| Устройство для преобразования двоично-десятичного кода в двоичный | 1985 |

|

SU1300641A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1292187A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1662004A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1569993A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283978A1 |

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных ЭВМ для построения преобразователей кодов. Целью изобретения является расширение класса решаемых задач за счет обеспечения обратного преобразования. Поставленная задача достигается тем, что в преобразователь двоично-десятичного кода в двоичный, содержащий k-разрядные преобразователи 1.1-1 .т+ 1 двоично-десятичного кода в двоичный, умножители 2.1-2.т, блок суммирования 4, дополнительно введены коммутаторы 3.1-3.т, преобразователи выполнены реверсивными, а умножители и коммутаторы - управляемыми. 1 ил.

Й/Т«

Изобретение относится к вычислительной технике и может быть использовано для построения преобразователей кодов в универсальных и специализированных ЭВМ.

Цель изобретения - расширение класса решаемых задач за счет обеспечения возможности обратного преобразования.

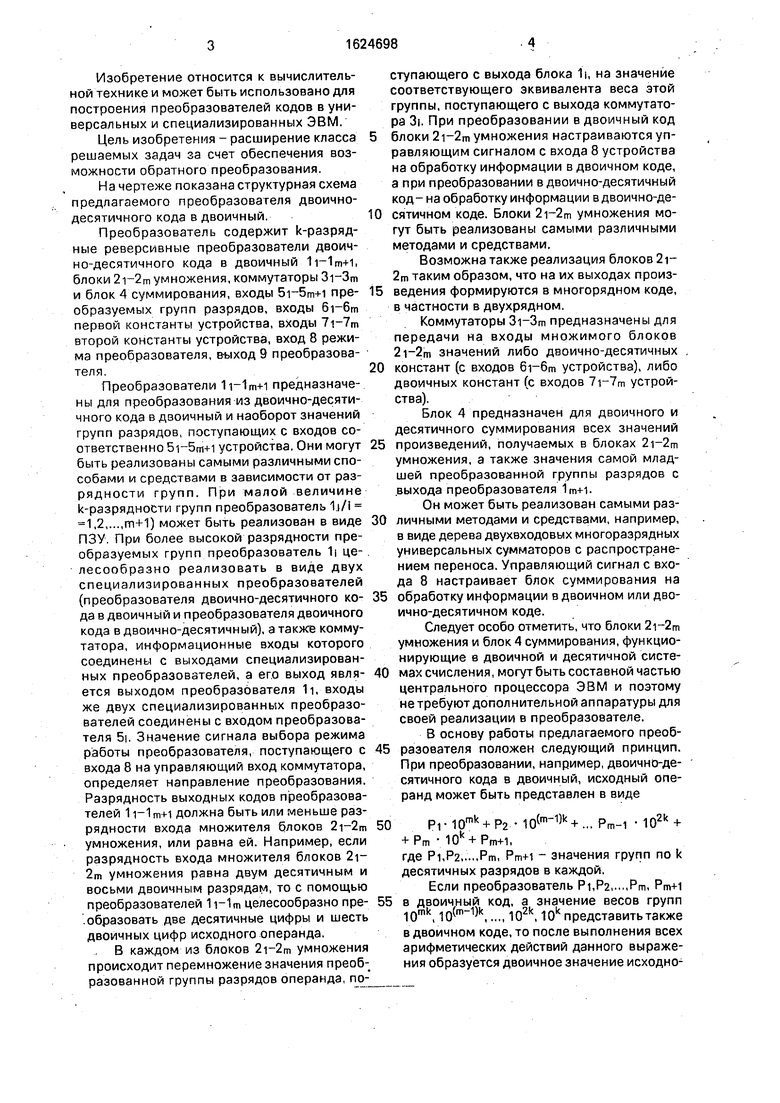

На чертеже показана структурная схема предлагаемого преобразователя двоично- десятичного кода в двоичный.

Преобразователь содержит k-разряд- ные реверсивные преобразователи двоично-десятичного кода в двоичный 1i-1m+i, блоки 2i-2m умножения, коммутаторы 3i-3m и блок 4 суммирования, входы 5i-5m+i преобразуемых групп разрядов, входы 6i-6m первой константы устройства, входы 7i-7m второй константы устройства, вход 8 режима преобразователя, выход 9 преобразователя.

Преобразователи предназначены для преобразования из двоично-десятичного кода в двоичный и наоборот значений групп разрядов, поступающих с входов соответственно 5i-5(fl+i устройства. Они могут быть реализованы самыми различными способами и средствами в зависимости от разрядности групп. При малой величине k-разрядности групп преобразователь 1i/i 1,2,...,m+1) может быть реализован в виде ПЗУ. При более высокой разрядности преобразуемых групп преобразователь 1| целесообразно реализовать в виде двух специализированных преобразователей (преобразователя двоично-десятичного кода в двоичный и преобразователя двоичного кода в двоично-десятичный), а также коммутатора, информационные входы которого соединены с выходами специализированных преобразователей, а его выход является выходом преобразователя 1i, входы же двух специализированных преобразователей соединены с входом преобразователя 5i, Значение сигнала выбора режима работы преобразователя, поступающего с входа 8 на управляющий вход коммутатора, определяет направление преобразования. Разрядность выходных кодов преобразователей 11-1 т+1 должна быть или меньше разрядности входа множителя блоков 2i-2m умножения, или равна ей. Например, если разрядность входа множителя блоков 2i- 2m умножения равна двум десятичным и восьми двоичным разрядам, то с помощью преобразователей 1i-1m целесообразно преобразовать две десятичные цифры и шесть двоичных цифр исходного операнда,

В каждом из блоков 2i-2m умножения происходит перемножение значения преобразованной группы разрядов операнда, поступающего с выхода блока 1i, на значение соответствующего эквивалента веса этой группы, поступающего с выхода коммутатора 3i. При преобразовании в двоичный код

блоки 2i-2m умножения настраиваются управляющим сигналом с входа 8 устройства на обработку информации в двоичном коде, а при преобразовании в двоично-десятичный код- на обработку информации вдвоично-десятичном коде. Блоки 2i-2m умножения могут быть реализованы самыми различными методами и средствами.

Возможна также реализация блоков 21- 2m таким образом, что на их выходах произведения формируются в многорядном коде, в частности в двухрядном.

Коммутаторы 3i-3m предназначены для передачи на входы множимого блоков 2i-2m значений либо двоично-десятичных

констант (с входов 6i-6m устройства), либо двоичных констант (с входов 7i-7m устройства).

Блок 4 предназначен для двоичного и десятичного суммирования всех значений

произведений, получаемых в блоках 2i-2m умножения, а также значения самой младшей преобразованной группы разрядов с выхода преобразователя 1т-и.

Он может быть реализован самыми различными методами и средствами, например, в виде дерева двухвходовых многоразрядных универсальных сумматоров с распространением переноса. Управляющий сигнал с входа 8 настраивает блок суммирования на

обработку информации в двоичном или двоично-десятичном коде.

Следует особо отметить, что блоки 2i-2m умножения и блок 4 суммирования, функционирующие в двоичной и десятичной системах счисления, могут быть составной частью центрального процессора ЭВМ и поэтому не требуют дополнительной аппаратуры для своей реализации в преобразователе.

В основу работы предлагаемого преоб5 разователя положен следующий принцип. При преобразовании, например, двоично-десятичного кода в двоичный, исходный операнд может быть представлен в виде

0 Pi 10mk + Pa 10()k + ... Pm-i 102k +

+ Pm 10k + Pm+1,

где Pi,P2Pm, Pm+1 - значения групп по k

десятичных разрядов в каждой.

Если преобразователь Pi,P2,..,,Pm, Pm+1

5 в двоичный код, а значение весов групп

10mk 10(ro-i)k1Q2k 1Qk представить также

в двоичном коде, то после выполнения всех арифметических действий данного выражения образуется двоичное значение исходного двоично-десятичного операнда. Аналогично двоичный операнд может быть представлен в виде суммы произведений двоично-десятичных эквивалентов групп разрядов и двоично-десятичных эквивалентов их весов.

Преобразование в предлагаемом устройстве происходит за один такт. При преобразовании двоично-десятичного кода в двоичный управляющий сигнал настраивает преобразователи 1i-1m+i на преобразо- вание значений соответствующих групп десятичных разрядов в двоичный код (преобразователь 1т+1 преобразует младшую группу разрядов, а преобразователь 1i - самую старшую), коммутаторы 3i-3m - на передачу информации с входов 7i-7m второй константы преобразователя, блоки 2i- 2m умножения и блок 4 суммирования - на функционирование в двоичной системе счисления. Поступающие с входов 5i-5m+i преобразователя соответствующие группы разрядов исходного операнда преобразуются в двоичный код в преобразователях 11-1 т+1 соответственно. В блоке 2, умножения происходит перемножение значения преобразованной группы разрядов операнда, поступающего с выхода соответствующего преобразователя 1( на значение соответствующего двоичного эквивалента веса этой группы, поступающего с выхода коммутатора Зь С выходов блоков умножения и выхода преобразователя 1 т+1 информация поступает на входы блока 4, в котором происходит ее двоичное суммирование. Через некоторое время, определяв- мое временем переходного процесса, на выходе 9 устройства образуется окончательный результат преобразования. Аналогично выполняется преобразование двоичного кода в двоично-десятичный. Уп- равляющий сигнал с входа 8 выбора режима в этом случае настраивают преобразователи 11-1 т+1 на преобразование значений соответствующих групп двоичных разрядов в двоично-десятичный код, коммутаторы 3i-

3m - на передачу информации с входов 6i- 6m первой константы устройства, блок 2 i-2m умножения и блок 4 суммирования - на функционирование в десятичной системе счисления.

Формула изобретения Преобразователь двоично-десятичного кода в двоичный, содержащий m блоков умножения (m n/k - 1), где п - количество десятичных цифр операнда, k - количество десятичных цифр, обрабатываемых на одном блоке умножения (k 2,3, ...п/2), (т+1) k-разрядных реверсивных преобразователей двоично-десятичного кода в двоичный и блок суммирования, выход которого является выходом преобразователя, j-ная 0 1- -(m+lXk-разрядная группа входов преобразователя соединена с группой входов j-ro k-разрядного реверсивного преобразователя двоично-десятичного кода в двоичный, выход которого, кроме (гп+1)-го, соединен с входом множителя блока умножения, выход которого соединен с входом j-ro слагаемого блока суммирования, выход (т+1)-го k-разрядного реверсивного преобразователя двоично-десятичного кода в двоичный соединен с входом (т+1)-го слагаемого блока суммирования, отличающийся тем, что, с целью расширения класса решаемых задач за счет обеспечения возможности обратного преобразования, в нею дополнительно введены m коммутаторов, причем j-й вход первой константы преобразователя соединен с первым информационным входом j-ro коммутатора, второй информационный вход которого соединен с j-м входом второй константы преобразователя, вход множимого j-ro блока умножения соединен с выходом j-ro коммутатора, управляющий вход которого соединен с входом режима преобразователя и управляющими входами блоков умножения, блока суммирования и k-разрядных реверсивных преобразователей двоично-десятичного кода в двоичный.

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1983 |

|

SU1095169A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

Авторы

Даты

1991-01-30—Публикация

1988-06-20—Подача