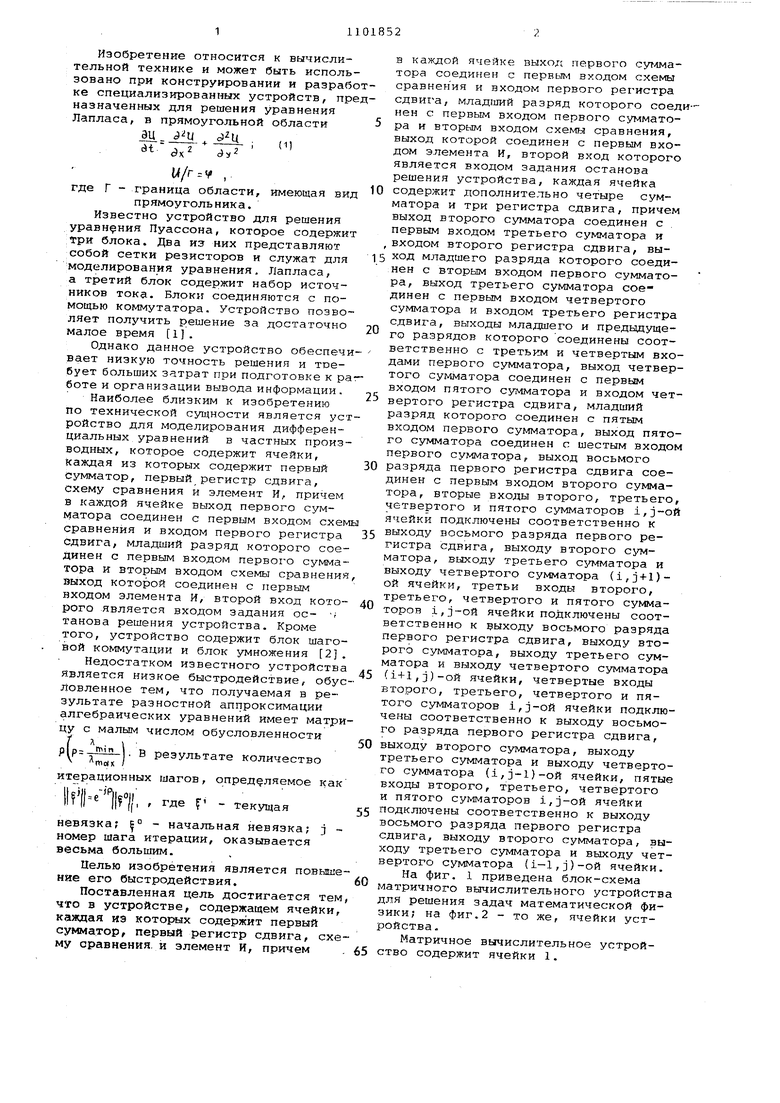

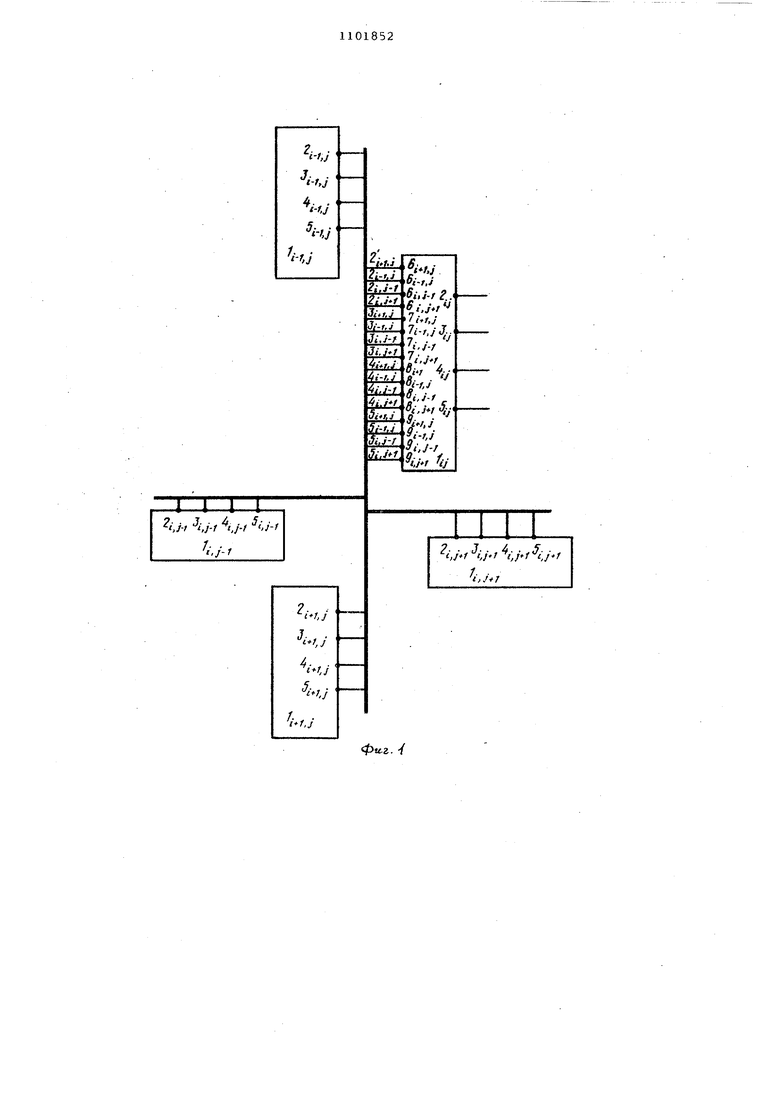

Изобретение относится к вычислительной технике и может быть использовано при конструировании и разрабо ке специализированных устройств, пре назначенных для решения уравнения Лапласа, в прямоугольной области Ж- , di /r.V ,. Г - граница области, имеющая вид прямоугольника. Известно устройство для решения уравнения Пуассона, которое содержит три блока. Два из них представляют собой сетки резисторов и служат для моделирования уравнения. Лапласа, а третий блок содержит набор источников тока. соединяются с помощью коммутатора. Устройство позволяет получить решение за достаточно малое время 1. Однако данное устройство обеспечи вает низкую точность решения и тоебует больших затрат при подготовке к ра боте и организации вывода информации. Наиболее близким к изобретению по технической сущности является ус ройство для моделирования дифференциальных уравнений в частных произ водных, которое содержит ячейки, Каждая из которых содержит первый сумматор, первый регистр сдвига, схему сравнения и элемент И, причем в каждой ячейке выход первого сумматора соединен с первым входом схем сравнения и входом первого регистра сдвига, младший разряд которого сое динен с первым входом первого сумма тора и вторым входом схемы сравнени выход которой соединен с первым входом элемента И, второй вход кото рого является входом задания ос- ; танова решения устройства. Кроме того, устройство содержит блок шаго вой коммутации и блок умножения 2 Недостатком известного устройств является низкое быстродействие, обу ловленное тем, что получаемая в результате разностной аппроксимации алгебраических уравнений имеет матр цу с малым числом обусловленности В результате количество определяемое как итерационных шагов. . f - текущая невязка; ° - начальная невязка; j номер шага итерации, оказьшается весьма большим. Целью изобретения является повыш ние его быстродействия. Поставленная цель достигается те что в устройстве, содержащем ячейки каждая иэ которых содержит первый сумматор, первый регистр сдвига, сх му сравнения, и элемент И, причем в каждой ячейке выход первого сумматора соединен с первым входом схемы сравнения и входом первого регистра сдвига, младгиий разряд которого соеди-нен с первым входом первого сумматора и вторым входом схемы сравнения, выход которой со€эдинен с первым входом элемента И, второй вход которого является входом задания останова решения устройства, каждая ячейка содержит дополнительно четыре сумматора и три регистра сдвига, причем выход второго сумматора соединен с . первым входом третьего сумматора и входом второго регистра сдвига, выход младшего разряда которого соединен с вторым входом первого сумматора, выход третьего сумматора соединен с первым входом четвертого сумматора и входом третьего регистра сдвига, выходы младшего и предыдущего разрядов которого соединены соответственно с третьим и четвертым входами первого сумматора, выход четвертого сумматора соединен с первым входом пятого сумматора и входом четвертого регистра сдвига, младший разряд которого соединен с пятым входом первого сумматора, выход пятого сумматора соединен с шестым входом первого сумматора, выход восьмого разряда первого регистра сдвига соединен с первым входом второго сумматора, вторые входы второго, третьего, четвертого и пятого сумматоров i,j-oй ячейки подключены соответственно к выходу восьмого разряда первого регистра сдвига, выходу второго сумматора, выходу третьего сут гматора и выходу четвертого сумматора (i,j+l)ой ячейки, третьи входы второго, третьего, четвертого и пятого сумматоров i,j-oй ячейки подключены соответственно к выходу восьмого разряда первого регистра сдвига, выходу второго сумматора, выходу третьего сумматора и выходу четвертого сумматора (i+l,j)-oй ячейки, четвертые входы второго, третьего, четвертого и пятого сумматоров i,j-oй ячейки подключены соответственно к выходу восьмого разряда первого регистра сдвига, выходу второго сумматора, выходу третьего сумматора и выходу четвертого сумматора (i,j-l)-oй ячейки, пятые входы второго, третьего, четвертого и пятого сумматоров i,j-oй ячейки подключены соответственно к выходу восьмого разряда первого регистра сдвига, выходу второго сумматора, выходу третьего сумматора и выходу четвертого сумматора (i-,j)-oй ячейки. На фиг. 1 приведена блок-схема матричного вычислительного устройства для решения задач математической физики; на фиг.2 - то же, ячейки устройства . Матричное вычислительное устройство содержит ячейки 1. Ячейка l;j содержит выходы 2,5;j , входы 6,1, ; 6i.i,j ; б{,.., и 6;, , входы ; 7,-.,. ; i.j- , входы 8 it-ij i f-T.j 8i,j-t 8;j4 , входы Э;,, ; 9i,j,t ; 9 i, , су7 1маторы Ю 14.. , регистры 15 j - 18 i сдвига, схему 19 ij сравнения, элемент И 20;. вход 21ij задания останова решения и выход 22ц останова. Устройство работает следующим образом. В начальный момент в регистрах 1 всех ячеек 1 записан нуль. В ячейка 1, расположенных вблизи границы, на входы поступает информация из граничных узлов (не показаны). На выходах сумматора 14 этих ячеек 1 формир ется новое значение функции ((if. кк+1 Ч ,-) - V Под vu t понимается величина .aA.., Y,.AU,, xl.AYf. ,2.ЛХ. ; (21 Л Ч-еМ(Г). где М(г)- множество граничных узлов; ap,a,a,j, а,Ь,Ь,,- постоянные ко эффициенты. Л хх v Величины коэффициентов зависят о разностной сетки, аппроксимирующей непрерывное пространство, на котором ищется решение. В рассматриваемом случае лх ду (4х - шаг сетки по х йу - шаг сетки по у) и ад Ь а 6/16; а2 1/16; а 3 1/256. Все коэффициенты кратны степени двойки, поэтому умножение на коэффи циенты можно существенно упростить. С этой целью умножим и разделим пра вую часть на 256, тогда ( ) Деление на 256 производится в регис тре 18 за счет сдвига. Рассмотрим теперь произвольный момент к и ячейку 1 , После заверше ния (к-1) шага на входы сумматора 10 поступает информация из соседних яче ек li,j ; Ij. ; Ij,}.-, ; li,;, с выходов 2, .; 2 . J ; 2,j.i ; + i ответственно. Эти выходы обеспечивают сдвиг содержимого регистров 18 на восемь разрядов впрйво (умножения на 1/256). На выходе сумматора 10,.j формируется величина YJ, , которая поступает на регистр ISij , где производится умножение на 256 (сдвиг влево на восемь разрядов). Одновременно с этим информация с выхода сумматора 10(у поступает на вход сутчматора Им- г куда поступает информация с выходов сумматоров 11 i+i,j lli-( j ; ll,,,-i и . На выходе сумматора 11,j формируется величина X J. , которая умножается на 64 и 32 в регистре 16 j; .Один выход соответствует умножению на 32, а другой - на 64. Аналогично - для сумматОров 12;; и 13;; , но с той лишь разницей, что умножение в первом случае производится на 16, а во втором - 1. На выходе сумматора 14 ,-j формируется величина 256 vt)., ко.торая записывается в регистр 18,.. . Решение прекращается, если U, и ij i Е. Условие останова определяется схемой 19,- сравнения, Скорость сходимости решения в известном устройстве, в котором реализуется разностная схема к+1 , i, i AU,j ,, определяется выражением Л l/2(sin.f sin. mc. ,;n- l/2( ), 2K 2R где N -число дискретов по х; k -число дискретов по у. В предложенном устройстве скорость сходимости решения равна )-3(...|L). -Ki-- t)-(), C. -.,z(.s -U Таким образом 1 Р min , Р т.е. скорость сходимости возрастает в четыре раза. При этом затраты оборудования практически не возрастают.

фи-г. {

М о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления корня к-ой степени | 1976 |

|

SU736096A1 |

| Матричное вычислительное устройство | 1979 |

|

SU809173A1 |

| Вычислительный узел цифровой сеточнойМОдЕли для РЕшЕНия диффЕРЕНциАльНыХуРАВНЕНий B чАСТНыХ пРОизВОдНыХ | 1979 |

|

SU798859A1 |

| Вычислительная ячейка | 1985 |

|

SU1287145A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Устройство для вычисления матрицы направляющих косинусов | 1983 |

|

SU1233142A1 |

| Матричное устройство для решения уравнений в частных производных | 1985 |

|

SU1302276A1 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| Вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных | 1980 |

|

SU926667A1 |

| Вычислительный узел цифровойСЕТОчНОй МОдЕли для РЕшЕНия диффЕРЕН-циАльНыХ уРАВНЕНий B чАСТНыХ пРОизВОд-НыХ | 1978 |

|

SU798858A1 |

МАТРИЧНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧ МАТЕМАТИЧЕСКОЙ ФИЗИКИ, содержащее ячейки, каждая из которых содержит первый сумматор, первый регистр сдвига, схему сравнения и элемент И, причем в каждой ячейке выход первого сумматора соединен с первым входом схемы сравнения и входом первого регистра сдвига, младший разряд которого соединен с первым входом первого сутиматора и вторым входом схемы сравнения, выход которой соединен с первым входом элемента И, второй вход которого является входом задания останова решения устройства, отличающееся тем, что, с целью повышения его быстродействия, каждая ячейка содержит дополнительно четыре сумматора и три регистра сдвига, причем выход второго сумматора соединен с первым входом третьего сумматора и входом второго регистра сдвига, выход младшего разряда которого соединен с вторым входом первого сумматора, выход третьего сумматора соединен с первым входом четвертого сумматора и входом третьего регистра сдвига, выходы младшего и предыдущего разрядов которого соединены соответственно с третьим и четвертым входами первого сумматора, выход четвертого сумматора соединен с первым входом пятого сумматора и входом четвертого регистра сдвига, младший разряд которого соединен с пятым входом первого сумматора, выход пятого сумматора соединен с шестым входом первого сумматора, выход восьмого разряда первого регистра сдвига соединен с первым входом второго сумматора, вторые входы второго, третьего, четвертого и пятого сумматоров i,j-oй ячейки подключены соответственно к выходу восьмого разряi да первого регистра сдвига, выходу второго сумматора, выходу третьего (Л сумматора и выходу четвертого сумматора

tovi ««ГчГ f

v л

BO осГ «s

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ отливки металлических деталей из жидкого металла | 1959 |

|

SU130637A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление к индикатору для определения момента вспышки в двигателях | 1925 |

|

SU1969A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ЗАДАЧ ТЕПЛОПРОВОДНОСТИ | 0 |

|

SU373735A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-07—Публикация

1982-04-30—Подача