Изобретение относится к вычислительной технике и может быть использовано в специализированных вычисши- тельных устройствах.

Целью изобретения является расширение функциональных возможностей за счет получения результата непосредственно в двоично-десятичной системе счисления.

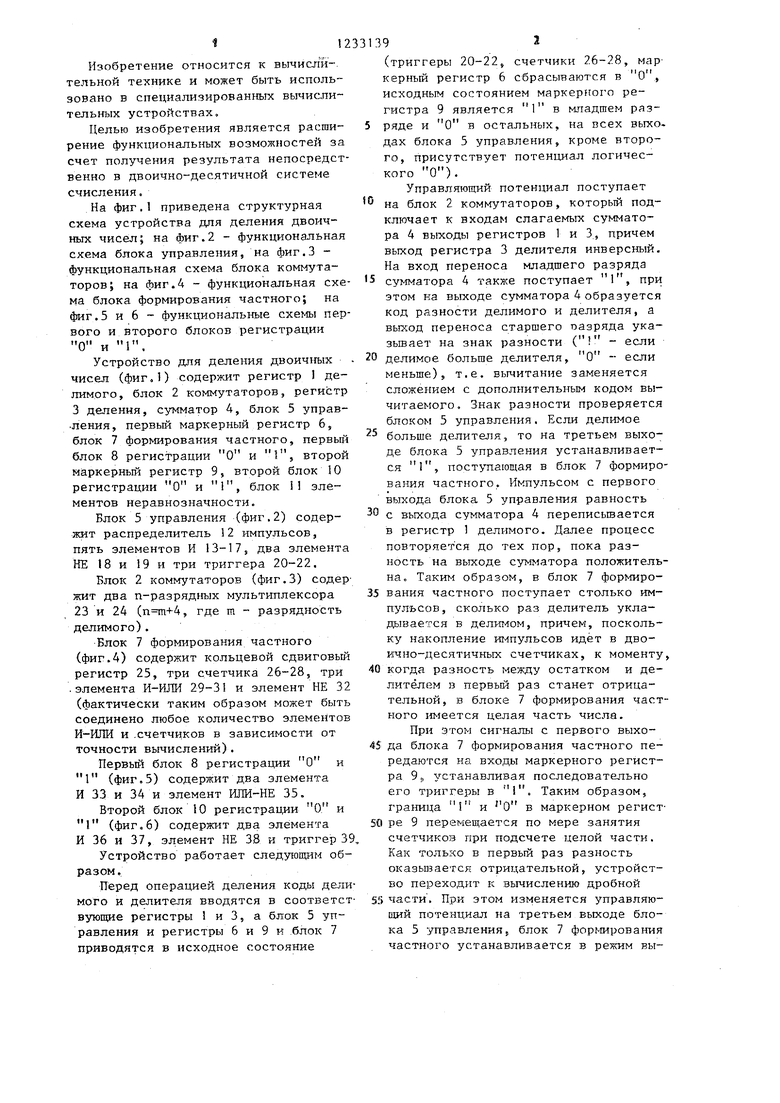

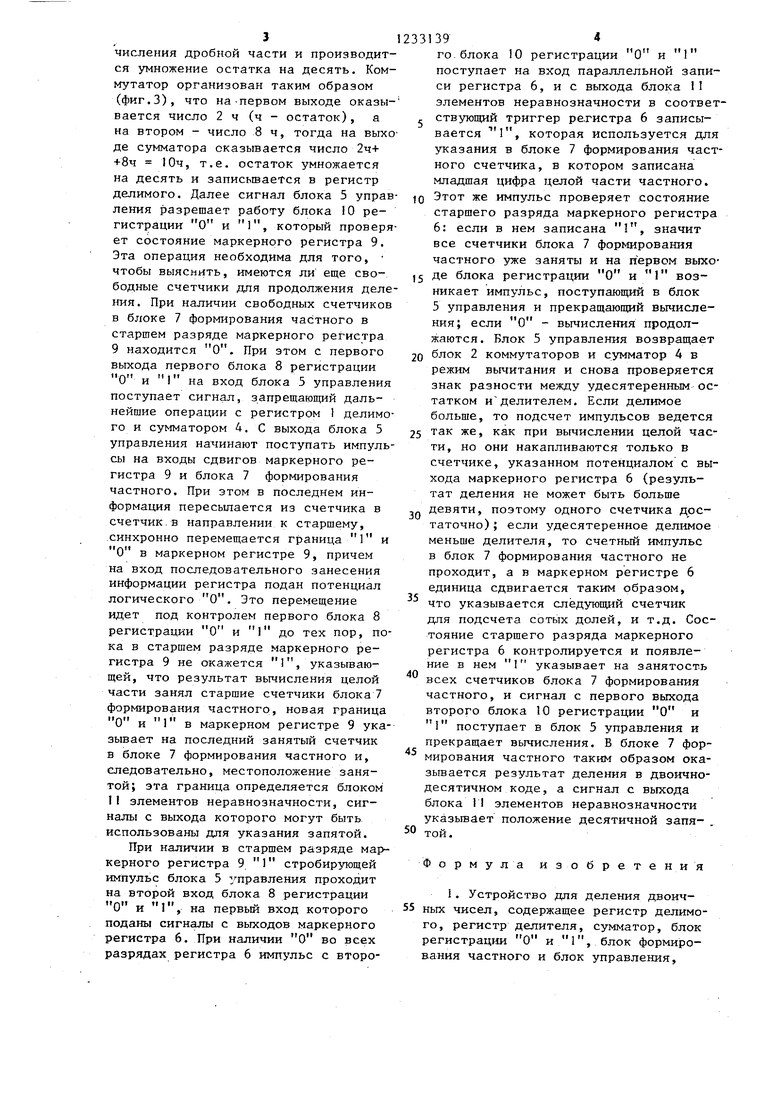

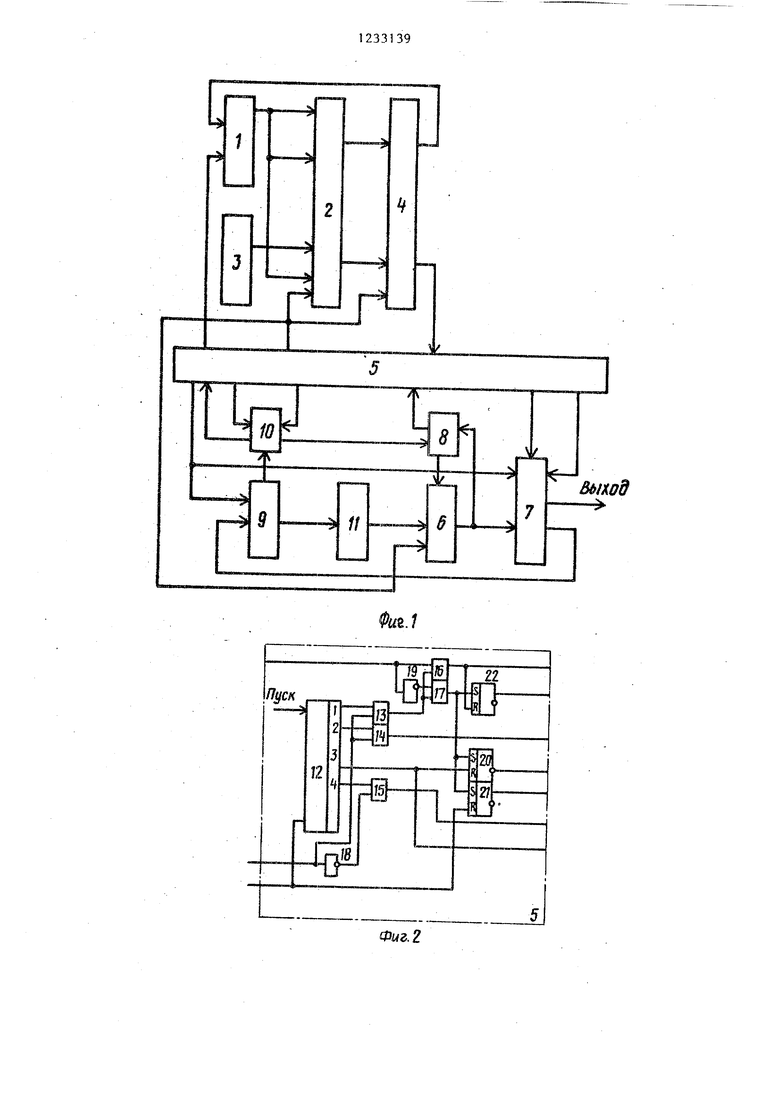

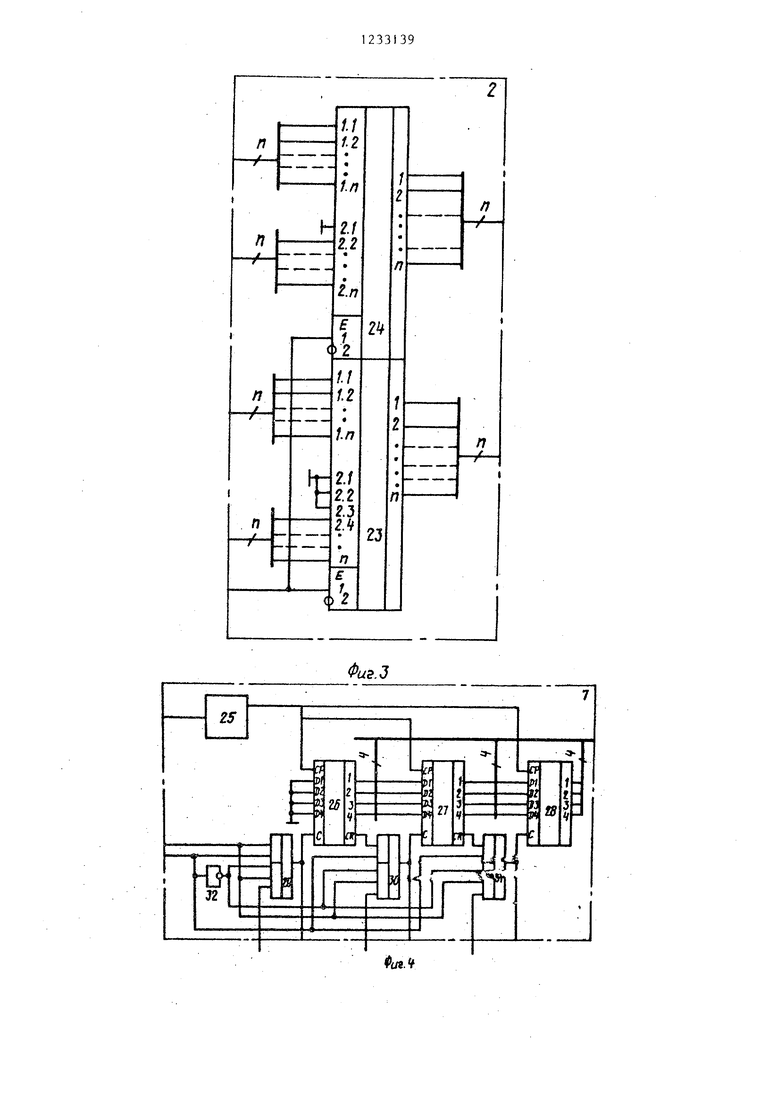

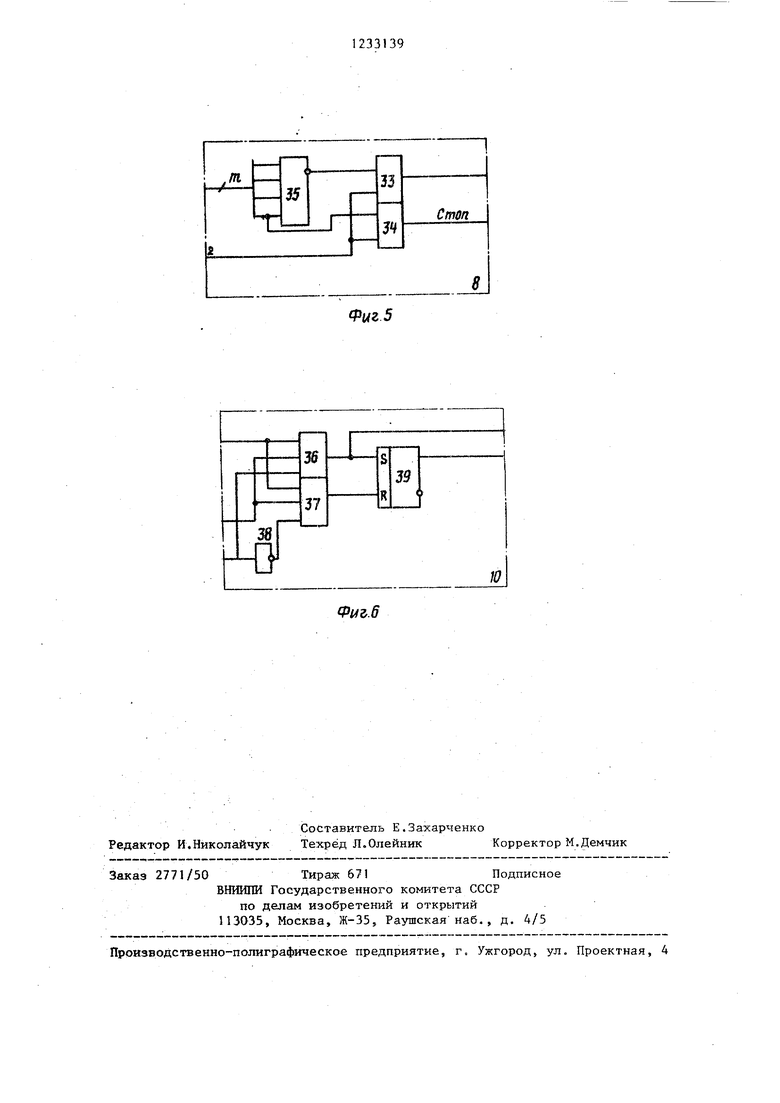

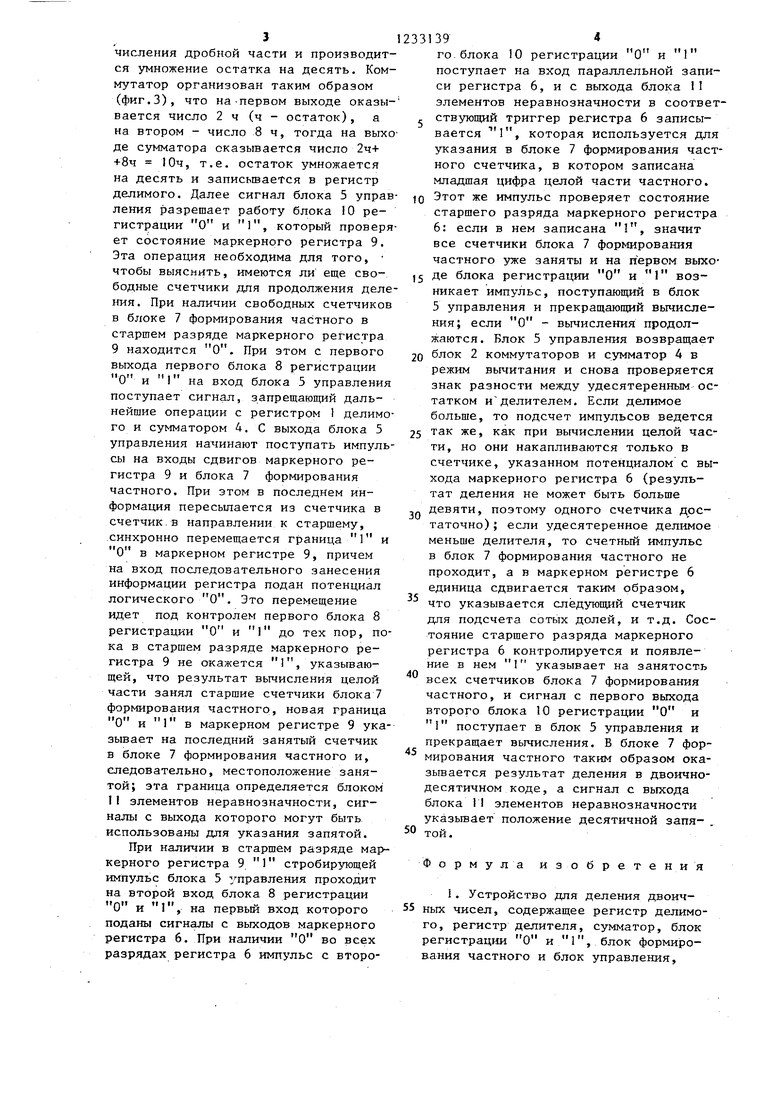

На фиг.1 приведена структурная схема устройства для деления двоичных чисел; на фиг.2 - функциональная схема блока управления, на фиг.З - функциональная схема блока коммутаторов; на фиг.4 - функциональная схема блока формирования частного; на фиг.5 и 6 - функциональные схемы первого и второго блоков регистрации О и Г

Устройство для деления двоичных чисел (фиг.1) содержит регистр 1 делимого, блок 2 коммутаторов, регистр 3 деления, сумматор 4, блок 5 управ- ления, первый маркерный регистр 6, блок 7 формирования частного, первый блок 8 регистрации О и 1, второй маркерный регистр 9, второй блок 10 регистрации О и 1, блок И элементов неравнозначности.

Блок 5 управления (фиг.2) содержит распределитель 12 импульсов, пять элементов И 13-17, два элемента НЕ 18 и 19 и три триггера 20-22.

Блок 2 коммутаторов (фиг.З) содер жит два п-разрядных мультиплексора 23 и 24 (, где m - разрядность делимого).

Блок 7 формирования частного (фиг.4) содержит кольцевой сдвиговый регистр 25, три счетчика 26-28, три .элемента И-ИЛИ 29-3 и элемент НЕ 32 (фактически таким образом может быть соединено любое количество элементов И-ИЛИ и .счетчиков в зависимости от точности вычислений).

Первый блок 8 регистрации О и 1 (фиг.5) содержит два элемента И 33 и 34 и элемент ИЛИ-НЕ 35,

Второй блок 10 регистрации О и 1 (фиг,6) содержит два элемента И 36 и 37, элемент НЕ 38 и триггер 39

Устройство работает следующим образом ,

Перед операцией коды делимого и делителя вводятся в соответствующие регистры и 3, а блок 5 управления и регистры 6 и 9 и .блок 7 приводятся в исходное состояние

(триггеры 20-22, счетчики 26-28, мар- керньй регистр 6 сбрасываются в О , исходным состоянием маркерного регистра 9 является 1 в младшем разряде и О в остальных, на всех выходах блока 5 управления, кроме второго, присутствует потенциал логического О).

Управляющий потенциал поступает

на блок 2 коммутаторов, который подключает к входам слагаемых сумматора 4 выходы регистров 1 и 3, причем выход регистра 3 делителя инверсный. На вход переноса младшего разряда

сумматора 4 также поступает 1 , при этом на выходе сумматора 4 образуется код разности делимого и делителя, а выход переноса старшего оазряда ука- зьшает на знак разности (1 - если

делимое больше делителя, О - если меньше), т.е. вычитание заменяется сложением с дополнительным кодом вычитаемого. Знак разности проверяется блоком 5 управления. Если делимое

больше; делителя, то на третьем выходе блока 5 управления устанавливается 1, поступающая в блок 7 формирования частного. Импульсом с первого выхода блока 5 управления равность

с выхода сумматора 4 переписьшается в регистр делимого. Далее процесс повторяется до тех пор, пока разность на выходе сумматора положительна, Такш- образом, в блок 7 формирования частного поступает столько импульсов , сколько раз делитель укладывается в делимом, причем, поскольку накопление иг пульсов идёт в двоично-десятичных счетчиках, к моменту,

когда разность между остатком и делителем в первьй раз станет отрицательной, в блоке 7 формирования частного имеется целая часть числа.

При этом сигналы с первого выхода блока 7 формирования частного передаются на входы маркерного регистра 9э устанавливая последовательно его триггеры в 1. Таким образом, граница и О в маркерном регистре 9 перемещается по мере занятия счетчиков при подсчете целой части. Как только в первый раз разность оказьшается отрицательной, устройство переходит к вьтислению дробной

части . При этом изменяется управляю- пщй потенциал на третьем выходе блока 5 управления, блок 7 формирования частного устанавливается в режим вычисления дробной части и производится умножение остатка на десять. Коммутатор организован таким образом (фиг.З), что на-первом выходе оказывается число 2 ч (ч - остаток), а на втором - число 8ч, тогда на выхо де сумматора оказывается число 2ч+ +8ч 10ч, т.е. остаток умножается на десять и записьтается в регистр делимого. Далее сигнал блока 5 управления разрешает работу блока 10 регистрации О и 1, который проверяет состояние маркерного регистра 9, Эта операция необходима для того, чтобы выяснить, имеются ли еще свободные счетчики дпя продолжения деления. При наличии свободных счетчиков в блоке 7 формирования частного в старшем разряде маркерного регистра 9 находится О. При этом с первого выхода первого блока 8 регистрации О и 1 на вход блока 5 управления поступает сигнал, запрещающий дальнейшие операции с регистром 1 делимого и сумматором 4. С выхода блока 5 управления начинают поступать импульсы на входы сдвигов маркерного регистра 9 и блока 7 формирования частного. При этом в последнем информация пересылается из счетчика в счетчик в направлении к старшему, синхронно перемещается граница 1 и О в маркерном регистре 9, причем на вход последовательного занесения информации регистра подан потенциал логического О. Это перемещение идет под контролем первого блока 8 регистрации О и 1 до тех пор, пока в старшем разряде маркерного регистра 9 не окажется 1, указывающей, что результат вычисления целой части занял старшие счетчики блока 7 формирования частного, новая граница О и 1 в маркерном регистре 9 указывает на последний занятый счетчик в блоке 7 формирования частного и, следовательно, местоположение занятой; эта граница определяется блоком 11 элементов неравнозначности, сигналы с выхода которого могут быть использованы для указания запятой.

При наличии в старшем разряде маркерного регистра 9 1 стробирующей импульс блока 5 управления проходит на второй вход блока 8 регистрации О и 1, на первый вход которого поданы сигналы с выходов маркерного регистра 6. При наличии О во всех разрядах регистра 6 импульс с второ

233139

го.блока 10 регистрации О и 1 поступает на вход параллельной записи регистра 6, и с выхода блока П элементов неравнозначности в соответствующий триггер регистра 6 записывается 1, которая используется для указания в блоке 7 формирования частного счетчика, в котором записана младщая цифра целой части частного.

0 Этот же импульс проверяет состояние старшего разряда маркерного регистра 6: если в нем записана 1, значит все счетчики блока 7 формирования частного уже заняты и на первом выхоJ5 де блока регистрации О и 1 возникает импульс, поступающий в блок 5 управления и прекращающий вычисления; если О - вычисления продолжаются. Блок 5 управления возвращает

2Q блок 2 коммутаторов и сумматор 4 в режим вычитания и снова проверяется знак разности между удесятеренным остатком и делителем. Если делимое больше, то подсчет импульсов ведется

25 так же, как при вычислении целой части, но они накапливаются только в счетчике, указанном потенциалом с выхода маркерного регистра 6 (результат деления не может быть больше девяти, поэтому одного счетчика достаточно) ; если удесятеренное делимое меньше делителя, то счетный импульс в блок 7 формирования частного не проходит, а в маркерном регистре 6 единица сдвигается таким образом, что указывается следующий счетчик для подсчета сотых долей, и т.д. Состояние старшего разряда маркерного регистра 6 контролируется и появление в нем 1 указывает на занятость всех счетчиков блока 7 формирования частного, и сигнал с первого выхода второго блока 10 регистрации О и F поступает в блок 5 управления и прекращает вычисления. В блоке 7 формирования частного таким образом оказывается результат деления в двоично- десятичном коде, а сигнал с выхода блока Г элементов неравнозначности указывает положение десятичной запя40

45

50

той.

Формула изобретения

. Устройство для деления двоич- 55 ных чисел, содержащее регистр делимого, регистр делителя, сумматор, блок регистрации О и 1, блок формирования частного и блок управления.

to

15

20

25

ервый вход которого соединен с выхоом переноса сумматора, выход суммы оторого соединен с информационным ходом регистра делимого, вход записи которого соединен с первым выхоом блока управления, второй выход оторого соединен с входом переноса сумматора, а третий выход - с первым ходом блока формирования частного, отличающееся тем, что, с целью расширения функциональных возможностей за счет получения результата непосредственно в двоично-десятичной системе счисления, в.него введены блок коммутаторов, выполненньй в виде двух мультиплексоров, второй блок регистрации О и i, два маркерных регистра и группа элементов неравнозначности, выходы которых соединены с информационными входами первого маркерного регистра, вход сдвига которого соединен с управляющими входами первого и второго мультиплексоров блока коммутаторов и вторым выходом блока управления, четвертый выход которого соединен с вторым входом бло ка формирования частного и входом сдвига второго маркерного регистра, информационные входы которого соединены с первым выходом блока формирования частного, третчй вход которого соединены с выходом первого маркерного регистра и информационными входами первого блока регистрации О и , стробирующий вход которого со- единен с первым выходом второго блока регистрации О и 1, информационный вход которого соединен с выходом старшего разряда, второго маркерного регистра, разрядные выходы которого соединены с соответств тощими входами элементов неравнозначности группы, выход результата устройства соединен с вторым выходом блока формирования частного, четвертый вход которого соединен с пятым выходом блока управления, шестой и седьмой выходы которого соединены соответственно со стробирующим входом и входом разрешения проверки маркерных регистров второго блока регистрации О и Г, второй выход которого соединен с вторым входом блока управления, третий вход которого соединен с первым выходом первого блока ре- - гистрации О и 1, второй выход которого соединен с входом записи первого маркерного регистра, инверс30

40

45

50

ВЫХОД регистра делителя соединен с первой группой информационьсьгх входов первого мультиплексора блока коммутаторов, вторая группа информацион- Hijix входов которого соединена с выходом регистра делимого и первой и второй группами информационных входов второго мультиплексора блока коммутаторов, выходы первого и второго мультиплексоров которого соединены соответственно с входами первого и второго слагаемых сумматора, четвертый вход блока управления соединен с входом Пуск устройства.

2, Устройство по п.1, о т л и - чающееся тем, что блок управления содержит распределитель импульсов, пять элементов И, два элемента j НЕ и три триггера, причем первый вход блока управления соединен с входом первого элемента НЕ и первым входом первого элемента И, второй вход которого соединен с первым входом второго элемента И и выходом третьего элемента И, первый вход которого соединен с первым выходом распределителя импульсов, второй выход которо- го соединен с первым входом четвертого элемента- И, второй вход которого соединен с вторым входом третьего эх емепта И, вторым входом блока управления и входом второго элемента НЕ, выход которого соединен с первым входом пятого элемента И, выход которого соединен с четвертым выходом блока управления, третий выход которого соединен с выходом первого триггера, вход установки в 1 которого соединен с входами установки в 1 второго и третьего триггеров и выхо- дом второго элемента И, второй вход которого соединен с выходом первого элемента НЕ, выход первого элемента И соединен с пятым выходом блока управления и входом установки в О третьего триггера, выход ко.торого соединен с седьмым выходом блока управления S первый выход которого соединен с выходом четвертого элемента И, второй вход которого соединен рым выходом распределителя сигналов, третий вькод которого соединен с шестым вьпсодом блока управления и входом установки в О второго триггера, вьссод которого соединен с вторым вкгходом блока управления, третий вход которого соединен с входом уста-; НОНКИ в О первого триггера и входом сброса распределителя сигналов, четвертый выход которого соединен с вторым входом пятого элемента И, а счетный вход - с четвертым входом блока управления.

3.Устройство по п.1, отличающееся тем, что блок формирования частного содержит кольцевой сдвиговый регистр, три счетчика, три элемента И-ИЛИ и элемент НЕ, вход которого соединен с первым входом блока формирования частного и первыми входами элементов И-ИПИ, вторые входы которых соединены с третьим входом блока формирования частного, второй вход которого соединен с третьим и четвертым входами первого элемента И-ИЛИ и третьими входами второго и третьего элементов И-ИЛИ, чет- вертые входы которых соединены с выходами переполнения первого и второго счетчиков, выход элемента НЕ соединен с пятыми входами элементов И-ИЛИ, выходы которых соединены с синхровходами соответствующих счетчиков и первым входом блока формирования частного, второй вход которого соединен со счетным входом кольцевого сдвигового регистра, выход которо го соединен со счетными входами соответствующих счетчиков, выходы первого счетчика соединены с информационными входами второго счетчика, выходы которого соединены с информацион- ными входами третьего счетчика, выходы всех счетчиков соединены с вторым выходом блока формирования частного.

4.Устройство по nvI, отличающееся тем, что второй

блок регистрации О и 1 содержит триггер, два элемента И и элемент НЕ вход которого соединен с информационным входом второго блока регистрации О и 1 и первым входом первого элемента И, второй вход которого соединен с первым входом второго элемента И и стробирующим входом второго блока регистрации О и 1, вход разрешения проверки маркерных регистров которого соединен с вторым входом второго элемента Ни третьим входом первого элемента И, вьйсод которого соединен с входом установки в триггера и первым выходом второго блока регистрации О и 1, второй выход которого соединен с выходом триггера, выход установки в О которого соединен с выходом второго элемента И, второй вход которого соединен с выходом элемента НЕ.

5. Устройство по п.1, о т л и - чающееся тем, что первый блок регистрации О и Ч содержит элемент ИЛИ-НЕ и два элемента И, причем информационные входа первого блока регистрации О и 1 соединены с входами элемента ИЛИ-НЕ, выход которого соединен с первым входом первого элемента И, второй вход которого соединен с первым входом второго элемента И и стробирующим входом первого блока регистрации О и 1, первый и второй выходы которого соединены соответственно с выходом второго и первого элементов И, второй вход второго элемента И соединен с первым входом элемента РШИ-НЕ.

- V k

ra

/5

I

Bbiwd

-

f/

Ф«г.2

Фиг.З

Фиъ.6

Редактор И.Николайчук

Составитель Е.Захарченко

Я.Олейник Корректор М.Демчик

Заказ 2771/50Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушсв:ая наб. , д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1151957A1 |

| Устройство для деления чисел | 1981 |

|

SU1056183A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления десятичных чисел | 1990 |

|

SU1774328A1 |

| Устройство для деления п-разрядных десятичных чисел | 1976 |

|

SU742933A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления двоичных чисел | 1985 |

|

SU1270758A1 |

| Устройство для деления десятичных чисел | 1989 |

|

SU1688239A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

Изобретение относится к области вычислительной техники и может быть использовано в специализированных вы числительных устройствах. Целью изобретения является расширение функциональных возможностей за счет получения результата непосредственно в двоично-десятичной системе счисления. Устройство содержит регистр делимого, регистр делителя, сумматор, регистр частного, первый блок регистрации О и , блок управления, два маркерных регистра. В него введены блок элементов неравнозначности и второй блок регистрации О и так, что в процессе деления методом последовательного вычитания делителя из делимого результат накапливается в регистре частного в двоично-десятичном коде с указанием положения десятичной запятой. 4 з.п. ф-лы, 6 ил. I (Л IsD СО СО со со

| Самофалов К.Г | |||

| и др | |||

| Электронные цифровые вычислительные машины.- Киев, 1976, с | |||

| Водяной двигатель | 1921 |

|

SU325A1 |

| Устройство для деления | 1977 |

|

SU615477A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления двоичных чисел | 1975 |

|

SU646331A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-23—Публикация

1984-10-17—Подача