вого и второго дешифраторов - к входам, блоков управления и разрешения сдвига соответственно. Вход первого триггера соединен с выходом младших разрядов параллельного сумматора, нулевой вход первого триггера - с выходами первого и второго элементов «И.

Предложенное устройство реализует следуюш,ий алгоритм деления двоичных чисел с фиксированной запятой.

Берутся два п разрядных двоичных числа: делимое А, делитель В.

1.Делимое А сравнивается с делителем В.

а), то устанавливается прямой код делимого А, справа от :которого приписывается п пулевых разрядов. Проводятся нормализапия влево значения делителя В и соответствуюший этой нормализации сдвиг влево на /г разрядов значения делимого А.

б)Если , то берется прямой код делимого А, слева от которого приписывается п пулевых разрядов. Осуществляются нормализация влево значения делителя В и соответствуюкщй этой нормализации сдвиг влево на

k разрядов значения делимого /1.

2.Запоминается первый старший значащий разряд делимого А в аналогичном ьм разряде частного, на его месте заннсывается нуль, а к полученному числу прибавляется число, на единицу большее обратного кода нормализованного значения делителя, сдвинутого влево на число разрядов, на единицу меньшее номера позиции, которую занимала первая старшая значащая цифра в делимом, считая с (/г+1)-го разряда числа.

3.Запоминается очередной старший значащий разряд вновь образованного числа, прибавляется к аналогичному i-му разряду частного, а на его месте записывается нуль, и к полученному числу прибавляется число, на единицу большее обратного кода нормализованного значения делителя, сдвинутого влево на число разрядов, на единицу меньшее номера позиции, которую занимала старшая значащая цифра вновь образованпого чнсла, считая с его (га+1)-го разряда.

4.Проводятся операции, аналогичные предыдущей, до появления нулей в п старших разрядах чнсла. При этом к п младшим разрядам числа прибавляется число, на единицу большее обратного кода нормализоваиного значения делителя. В случае появления в (и-Ь)-м разряде числа единицы, она прибавляется к младшему разряду частного.

Па этом операция делеиия чисел -заканчивается.

Пусть, например, даны делимое

А 0,000100111000000,

делитель 5 0,000000000110001. , в соответствии с п. , б алгоритма имеем: 0,000000000000000 000100111000000, проводим нормализацию влево делителя В и соответствующий ей сдвиг влево делимого: 0000000000100111 000000000000000 0110001000000000

Далее образуем число С, которое на едини цу больше обратного кода нормализованного значения делителя: 0 0,001111000000000.

Выполняем и. 2 алгоритма

0,000000000100111 000000000000000

+ 00111 1000000000(фор.м1фование частного)

00000000000001110 100000000000000 0,000000000100000

Выполняем пп. 3 и 4 aлгopитJмa, до появлеиия нулей в старших разрядах числа 0,000000000001110 100000000000000 0,000000000100000 +I 111000000000-I-I

,5 0,000000000001000 011000000000000 0,000000000101000 +I 111000000000-ь1

0,000000000000010 010000000000000 0,000000000110000 ч-11110000000000 4-1

0,000000000000000 101110000000000 0,000000000110010 в старших разрядах числа содержатся нули, поэтому к младшнм разрядам числа прибавляем число С 250,000000000000000 101110000000000

4-1111000000000

0,00000000000000 111IOIOOOOOOGOO Так как в шестпадцатол разряде числа едипица отсутствует, то значение частного, равное 0,000000000110010, остается неизменным. Пусть тенерь даны делнмое

/1 0,000000010000000 и делитель В 0,001110000000000. Поскольку , в соответствии си. . и алгоритма, имеем 0,000000010000000 000000000000000, проводим нормализацию влево делителя В и соответствующий ей сдвиг влево делимого

0,000001000000000 ООООООООООООООЭ

0,111000000000000 Далее образуем число

С--- 0,001000000000000.

Проводим операцию деления, выно.чияя последующие нупкты алгоритма

(формирование частного)

0,000001003000000 000000000000000 0,000000000000000 -1000000 000000---1

О,000000001000000 000000000000000 о,000001000000000 +1030 000000000-;-I

55 0,000000000001000 000000000000000 0,000001001000000 +1 000000000000-i-1

00000000000000001 000000000000000 0,000001001001000 +1000000000000 -f1

0,000000000000000 001000000000000 0,000001001001001 +I000000000000

о,000000000000000 о10000000000000 65Результат деления: 0,000001001001001.

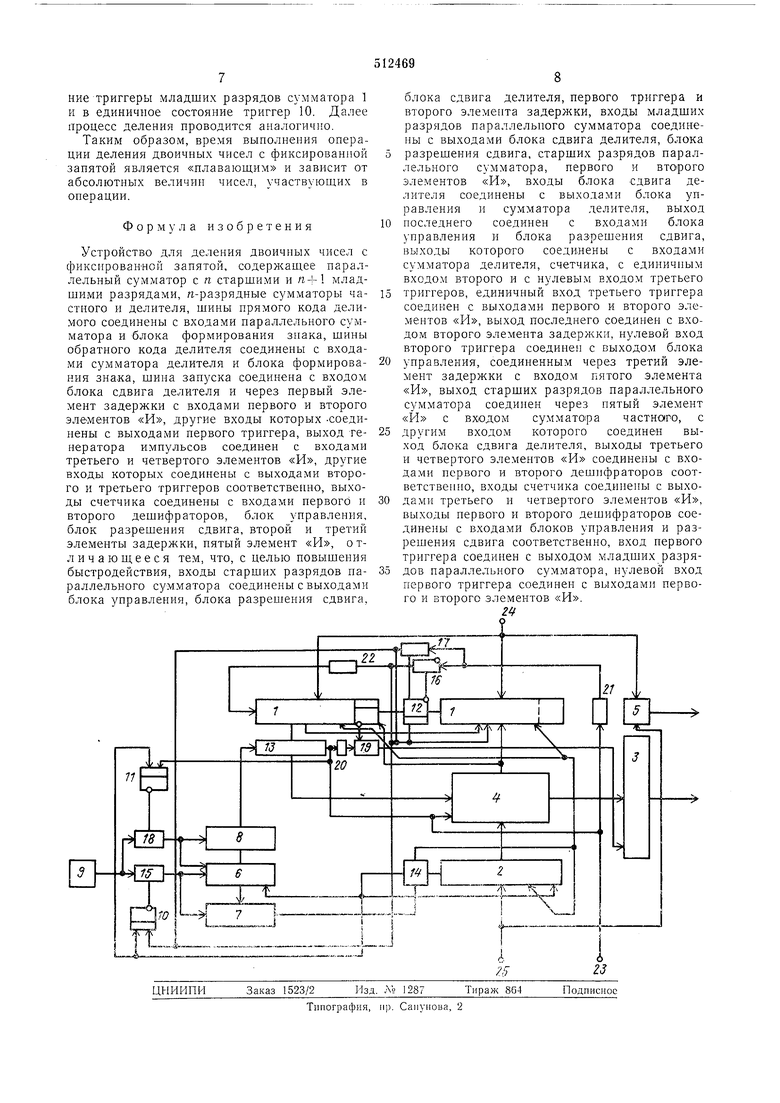

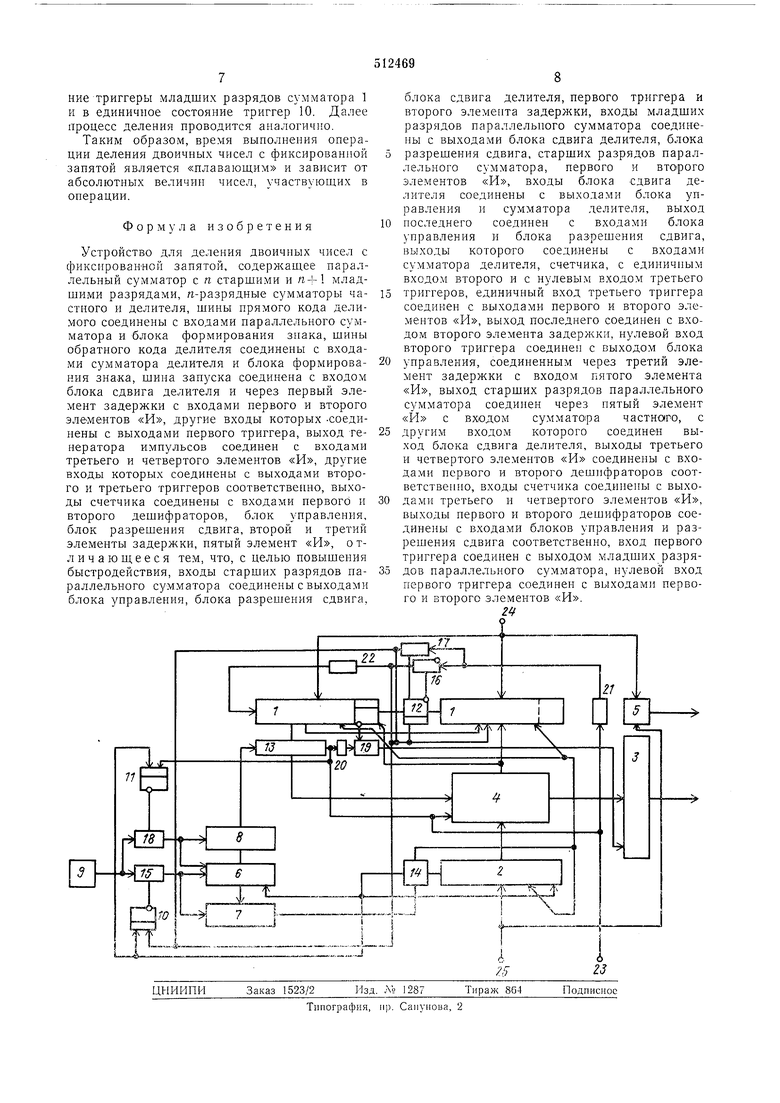

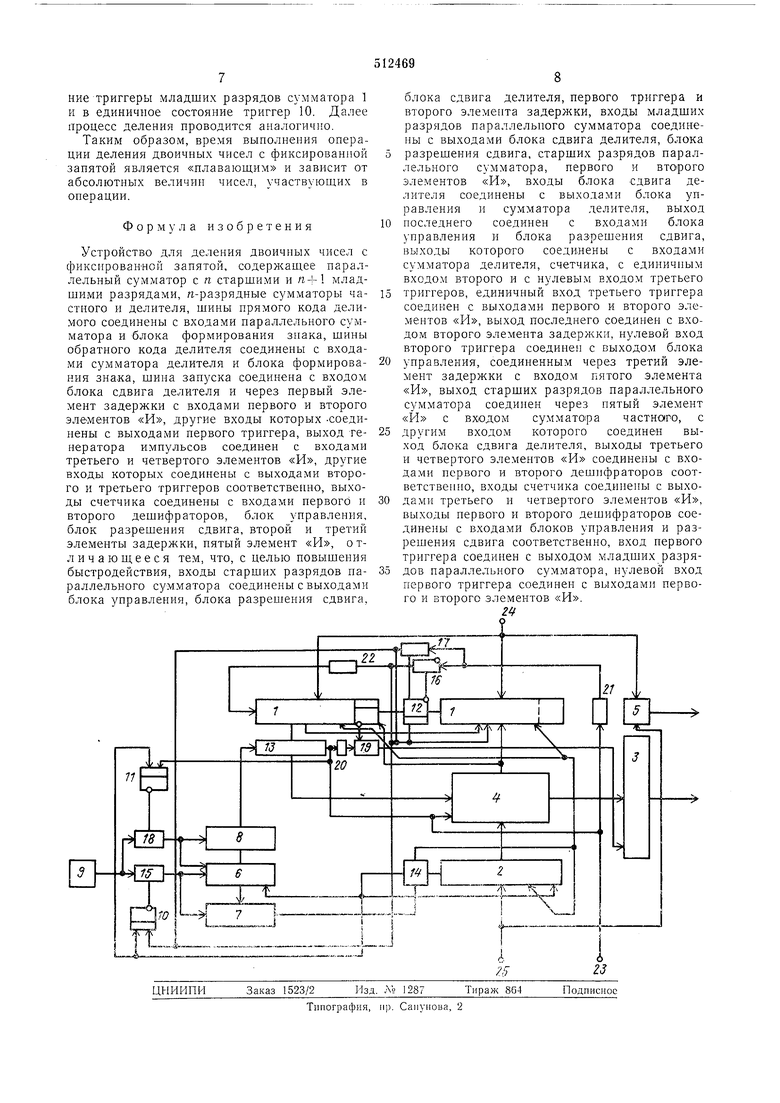

Схема устройства продетаплспа ir;i иорге/кс.

Устройство содержит параллельны сумматор 1, содержащий п старших и ra-f-l младших разрядов, сумматор 2 делителя (на п разрядов), сумматор 3 частного (на п разрядов), блок 4 сдвига делителя, блок 5 формирования зпака, счетчик 6, дешифраторы 7 и 8, генератор 9 имиульсов, триггеры 10, 11 п 12, блок 13 управления, с.чужащий для счи ывания обратного кода делителя и занесения единицы в сумматор частного, б;гок 14 разреп ения сдвига, используемый для сдвига делимого и делителя в соответствуюших сумматорах, элементы «И 15-19, элементы 20, 21, 22 задержки, вход 23 запуска, входы 24 делимого, входы 25 делителя.

Работает устройство следуюпдим образом.

Значения прямого кода делимого с входов 24 подается на параллельный сумматор 1, одновременно на старшие и младшие разряды сумматора, а значение прямого и обратного кода делителя - с входов 25 на сумматор 2 делителя.

Импульс запуска устройства с входа 23 поступает на блок 4 сдвига делителя, считывая несдвипутое зпачение обратного кода делителя в сумматор 1. Таким образом, проводится вычитание из значения делимого значения делителя, т. е. анализ величин делимого и делителя.

Если делимое больше делителя, то триггер 12 устанавливается в единичное состояние, тем самым позволяя импульсу запуска, задержанному па элементе 21 (на время вычитания чисел), пройти через элемент «И 16 и через элемент 22. Этот импульс разрешает считываиие значения делимого из старших разрядов сумматора 1 иа младшие разряды сумматора, причем считывание проводится на триггеры младших разрядов сумматора, начиная со второго.

Перед считыванием импульс с выхода элемента «И 16 устанавливает в пуль триггеры младших разрядов сумматора 1 и триггер 12, входяищй в состав младших разрядов сумматора 1. Одновремепно импульс с выхода элемента «И 16 поступает па установку в единичное состояние триггера 10, который разрешает прохождение импульсов с генератора 9 через элемент «И 15 па счетчик 6 и дешифратор 7. С дешифратора 7 импульсы сдвига подаются на блок 14 разрешения сдвига. Этот блок состоит из двух элементов «И, управляемых со старшего (га-го) триггера сумматора 2 делителя. Блок 14 разрешает ирохождение импульсов сдвига через первый элемент «И, в соответствии с алгоритмо.м деления, на сдвиг делимого и делителя, в случае единичного состояния п-го триггера сумматора 2 делителя.

При установке п-го триггера сумматора 2 в нулевое состояние, очередной импульс сдвига через другой элемент «И устанавливает в нуль триггер 10, прибавляет единицу в младший разряд сумматора делителя и устанавливает в ) сЧ( О; одновременно этот же имнульс иорсиодит в единичное состояние триггер 11, который разрешает прохождение через элемент «И 18 импульсов с генератора 9 через элемент «П иа счетчик 6 и дешифратор 8.

С дешифратора 8 импульсы, период которых равен времени одного сложения чисел в с мматоре 1, ноступают на вход блока 13 нравлення для считывания кода с сумматора 2 делителя и для занесения еднниц в сумматор 3 частного.

Блок 13 управления работает так, что импульс деления, последовательио проходя через элементы «И сквозного переноса, управляемые с единичных нлеч триггеров старших разрядов сумматора 1, отыскивает первый находяш,1Йся в единичном состоян1 и триггер старших разрядов сумматора, перебрасывает

его в нулевое состояние и поступает с выходной шины блока управления, соответствующей перебрасываемому триггеру, на вход блока 4 сдвига делителя и на вход соответствующего-г-го разряда сумматора 3 частного.

В блоке 4 сдвига делителя импульс считывает в сумматор 1 (для сложения) числа, на единицу большие значения обратного кода делителя, сдвинутого влево на единицу меньшего номера познции, которую занимали старН1ие значаниш цнфры в старших разрядах сумматора 1.

Сдвиг в блоке сдвига делителя осуществляется за счет соответствующей коммутации потенциальпых выходов триггеров сумматора

делителя с импульсными выходными шинами блока управления в соответствии с изложенным алгоритмом деления чисел.

Следующий за первым импульс с дешифратора 8 проводит аналогичные действия. Указапные операции выполняются до тех пор, пока не будут устаьовлены в нулевое состоянне все трпггеры старших разрядов сумматора 1. При этом очередг.ой импульс с выхода денлифратора 8, пройдя сквозным переносом через

элемент «И блоха управления, поступает в блОК сдвига делнтеля для считывания (в мла.т,шие разряды сумматора 1) числа, которое иа един1щу больше обратного кода делителя, а также переводит в нулевое состоя 1ие триггер 11.

В том случае, если в младшем разряде из старших разрядов сумматора 1 появляется единица, то этим же импульсом, через элемент 20 задержки и элемент «И 19 (управляемый по потенциальному входу с младшего разряда старших разрядов сумматора 1). эта единица заносится в младший разряд сумматора 3 частного.

Знак частного образуется в блоке 5 формирования знака. На этом процесс деления чисел заканчивается.

В случае, еслн делимое меньше делителя, то импульс запуска, пройдя через элемент «И 17, управляемый с единичного п.теча

триггера 12, устаиавливает в нулевое состоя

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для деления | 1988 |

|

SU1513444A1 |

| Устройство для деления чисел | 1981 |

|

SU1012241A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для деления двоичных чисел | 1985 |

|

SU1270758A1 |

| Устройство для деления | 1976 |

|

SU662938A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления двоичных чисел | 1982 |

|

SU1103224A1 |

| Устройство для деления с плавающей запятой | 1979 |

|

SU860063A1 |

Авторы

Даты

1976-04-30—Публикация

1974-03-07—Подача