Изобретение относится к автоматике и вычислительной технике и может быть использовано в специализированных вычислительных устройствах.

Целью изобретения является повышение точности вычисления.

Сущность изобретения заключается в приближенном вычислении модуля по следующей формуле:

/Re//Re/ - /Re/4/I i/,

T/Rel+{|ln,(

/Re/4/Re/+ /I «li/Re/i/Im/j

5i

M--tnax

4|lml4 Re/ /Ir /4/im/-4/«e/,/b/i/Re/3

Пfc0bI

lm /Im/i|/Im/+ /Re/J/b/ /l e/

b, bo де M - значение модуля числа; Re - значение действительной

части комплексного числа; Im - значение мнимой части комплексного числа.

Контроль устройства осуществляется сравнением (2х,+2Ь,+2k2+b2)mod Mmod3 ,

где kjjkj - значение контрольных

разрядов соответственно большей и меньшей составляющих комплексного числа;

значение трех младших разрядов большей составляющей комплексного числа;

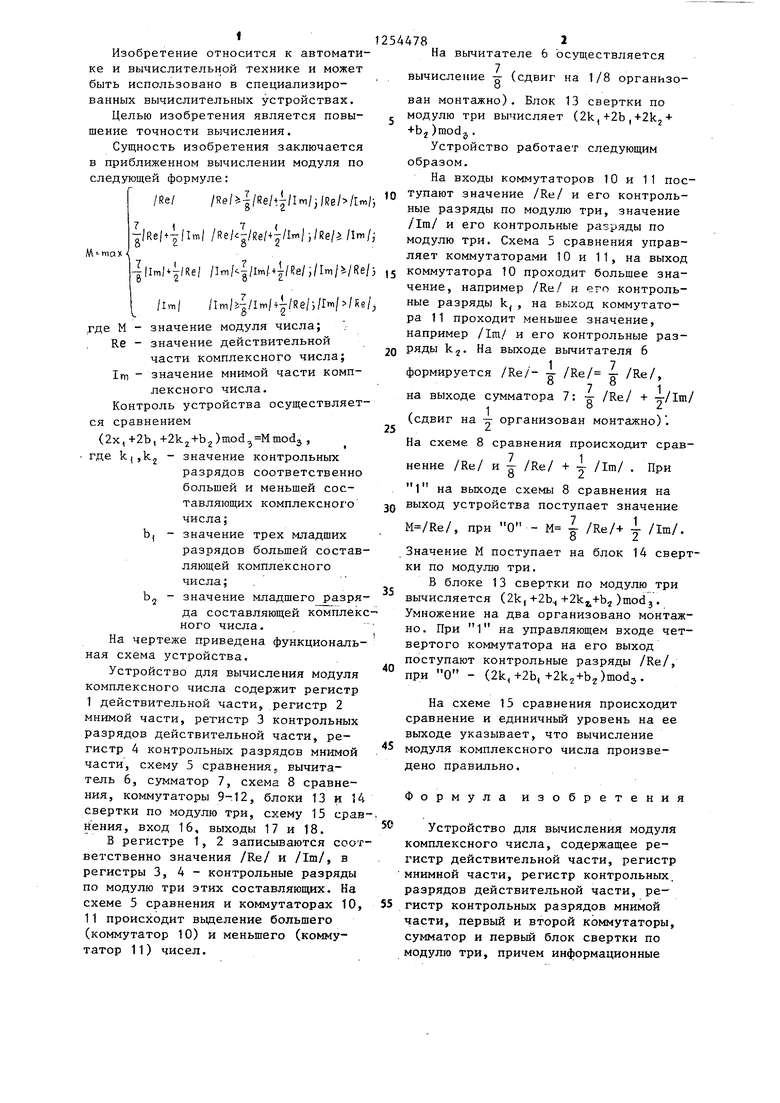

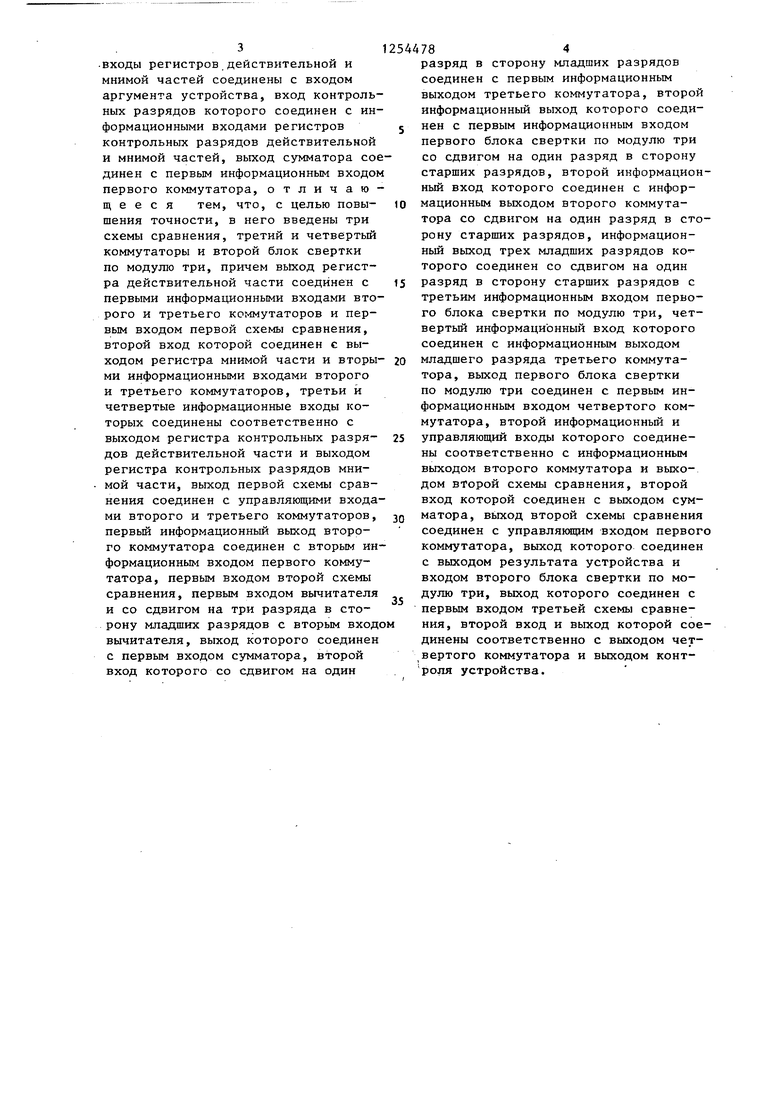

значение младшего разря- да составляющей комплексного числа. На чертеже приведена функциональ-

ная схема устройства.

Устройство для вычисления модуля

комплексного числа содержит регистр

Iдействительной части, регистр 2 нимой части, регистр 3 контрольных разрядов действительной части, регистр 4 контрольных разрядов мнимой части, схему 5 сравнения, вычита- тель 6, сумматор 7, схема 8 сравнения, коммутаторы 9-12, блоки 13 и 14 свертки по модулю три, схему 15 срав-, н ения, вход 16, выходы 17 и 18.

В регистре 1, 2 записьшаются соотетственно значения /Re/ и /Im/, в егистры 3, 4 - контрольные разряды о модулю три этих составляющих. На схеме 5 сравнения и коммутаторах 10,

I1происходит вьщеление большего (коммутатор 10) и меньшего (коммутатор 11) чисел.

544782

На вычитателе 6 осуществляется

вычисление - (сдвиг на 1/8 организо- о

ван монтажно). Блок 13 свертки по

, модулю три вычисляет (2k,+2Ь,+2k2+ Ь)modj.

Устройство работает следующим образом.

На входы коммутаторов 10 и 11 пос0 тупают значение /Re/ и его контрольные разряды по модулю три, значение /1га/ и его контрольные разряды по модулю три. Схема 5 сравнения управляет коммутаторами 10 и 11, на выход

5 коммутатора 10 проходит большее значение, например /Re/ и его контрольные разряды kj , на выход коммутатора 11 проходит меньшее значение, например /1га/ и его контрольные раз0 ряды k2. На выходе вычитателя 6

формируется /Re/- -5- /Re/ -5- /Re/,

7 1

на выходе сумматора 7: - /Re/ + Wlm/

1.

(сдвиг на -т: организован монтажно). 52

На схеме 8 сравнения происходит сравнение /Re/ и - /Re/ + /Im/ . При

1 на выходе схемы 8 сравнения на Q выход устройства поступает значение

, при О - М /Re/+ /Im/.

И 2.

Значение М поступает на блок 14 свертки по модулю три.

В блоке 13 свертки по модулю три вычисляется (2k, +2b. +2k. )mod j . Умножение на два организовано монтажно. При 1 на управляющем входе четвертого коммутатора на его выход поступают контрольные разряды /Re/,

5

0

5

при О - (2k,+2Ь,+2k2+b2)mod3.

На схеме 15 сравнения происходит сравнение и единичный уровень на ее выходе указывает, что вычисление модуля комплексного числа произведено правильно.

Формула изобретения

50 Устройство для вычисления модуля комплексного числа, содержащее регистр действительной части, регистр мнимной части, регистр контрольных, разрядов действительной части, ре55 гистр контрольных разрядов мнимой части, первый и второй коммутаторы, сумматор и первый блок свертки по модулю три, причем информационные

входы регистров действительной и мнимой частей соединены с входом аргумента устройства, вход контрольных разрядов которого соединен с информационными входами регистров контрольных разрядов действительной и мнимой частей, выход сумматора соединен с первым информационным входом первого коммутатора, отличающееся тем, что, с целью повы- шения точности, в него введены три схемы сравнения, третий и четвертый коммутаторы и второй блок свертки по модулю три, причем выход регистра действительной части соединен с первыми информационными входами второго и третьего ког-мутаторов и первым входом первой схемы сравнения, второй вход которой соединен с выходом регистра мнимой части и вторы- ми информационными входами второго и третьего коммутаторов, третьи и четвертые информационные входы которых соединены соответственно с выходом регистра контрольных разря- дов действительной части и выходом регистра контрольных разрядов мнимой части, выход первой схемы сравнения соединен с управляющими входами второго и третьего коммутаторов, первый информационный выход второго коммутатора соединен с вторым информационным входом первого коммутатора, первым входом второй схемы сравнения, первым входом вычитателя и со сдвигом на три разряда в сторону младших разрядов с вторым вход вычитателя, выход которого соединен с первым входом сумматора, второй вход которого со сдвигом на один

разряд в сторону младших разрядов соединен с первым информационным выходом третьего коммутатора, второй информационный выход которого соединен с первым информационным входом первого блока свертки по модулю три со сдвигом на один разряд в сторону старших разрядов, второй информационный вход которого соединен с информационным выходом второго коммутатора со сдвигом на один разряд в сторону старших разрядов, информационный выход трех младших разрядов ко торого соединен со сдвигом на один разряд в сторону старших разрядов с третьим информационным входом первого блока свертки по модулю три, четвертый информационный вход которого соединен с информационным выходом младшего разряда третьего коммутатора, выход первого блока свертки по модулю три соединен с первым информационным входом четвертого коммутатора, второй информационный и управляющий входы которого соединены соответственно с информационным выходом второго коммутатора и выходом второй схемы сравнения, второй вход которой соединен с выходом сумматора, вьпсод второй схемы сравнения соединен с управлякяцим входом первог коммутатора, выход которого соединен с выходом результата устройства и входом второго блока свертки по модулю три, выход которого соединен с первьм входом третьей схемы сравнения, второй вход и выход которой соединены соответственно с выходом четвертого коммутатора и выходом конт- роля устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1287151A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ КОМПЛЕКСНОГО ЧИСЛА | 2014 |

|

RU2562411C1 |

| Устройство для вычисления модуля комплексного числа | 1982 |

|

SU1104505A2 |

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1193662A1 |

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1233145A1 |

| Устройство для вычисления модуля комплексного числа | 1989 |

|

SU1693599A1 |

| Устройство для умножения комплексных чисел | 1986 |

|

SU1388851A1 |

| Устройство для вычисления гиперболических синуса и косинуса | 1987 |

|

SU1497615A1 |

| Устройство для контроля умножения чисел по модулю | 1985 |

|

SU1259269A1 |

| Устройство для быстрого преобразования Фурье | 1982 |

|

SU1170462A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в специализированных вычислительных устройствах. Целью изобретения является повышение точности вычисления. Устройство содержит регистры действительной и мнимой частей аргумента, регистры контрольных разрядов действительной и мнимой частей аргумента, четыре коммутатора, три схемы.сравнения, два блока свертки по модулю три, вычитатель и сумматор. Точность выполнения повышена за счет использования нового алгоритма вычисления модуля комплексного числа. 1 ил. to р1 (Ь 4 00

| Электродинамический громкоговоритель | 1930 |

|

SU27719A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления модуля комплексного числа | 1982 |

|

SU1104505A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-30—Публикация

1985-03-27—Подача