1

Изобретение относится к области вычислительной техники и предназначено для выполнения элементарных функций.

Известно арифметическое устройство специализированной цифровой вычислительной машины (СЦВМ), содержащее сумматорсдвигатель, группы управляемых вентилей, регистры кодов слагаемых величин и логические схемы.

Однако для вычисления каждой элементарной функции необходимо выполнение большого количества операций. Например, вычисление простейших функций синуса и косинуса требует выполнения 50-80 арифметических операций. Это существенло удлиняет весь вычислительный процесс и снижает быстродействие машины.

Цель изобретения - повышение быстродействия вычислительной машины путем сокращения времени вычисления элементарных функций решаемой задачи.

Это достигается тем, что предлагаемое устройство содержит два дополнительных вентиля и сдвигающий регистр приращения кода зоны, выход которого непосредственно и через логический элемент «НЕ присоединен к первым входам двух управляемых вентилей. К их вторым входам подключена шина стробирующего сигнала. Выходы вентилей подсоединены к соответствующим входам двух групп управляемых вентилей.

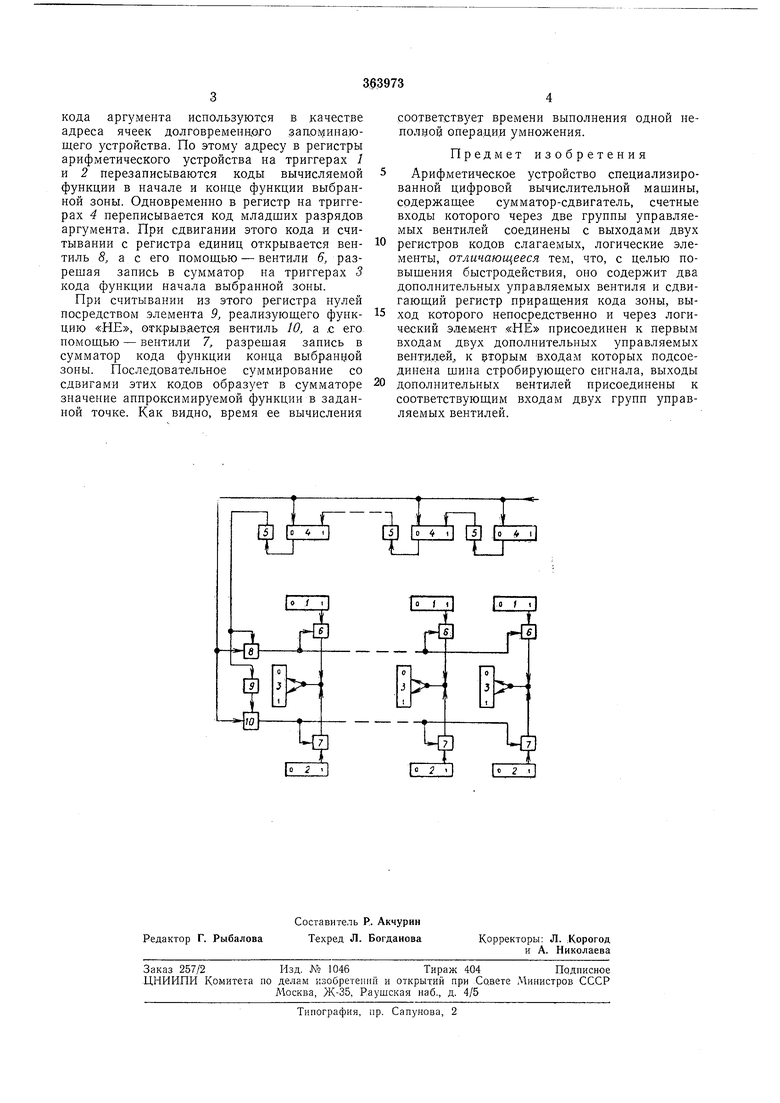

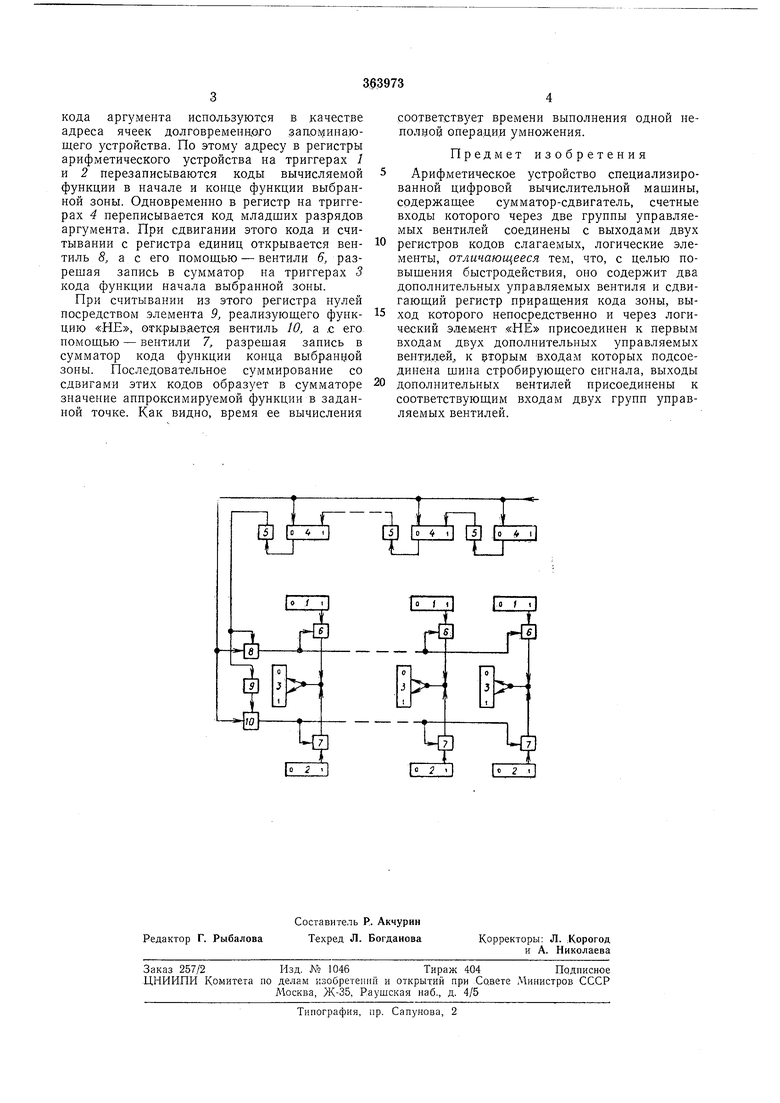

На чертеже показана схема предлагаемого устройства.

Триггеры 1 и 2 образуют регистры слагаемых, триггеры 3 - сумматор-сдвигатель, а

триггеры 4 с дифференцирующе-задерживающими элементами 5 - сдвигающий регистр. Через группы управляемых вентилей 6 и 7 выходы регистров слагаемых соединены со счетными входами сумматора-сдвигателя. Выход сдвигающего регистра непосредственно связан с дополнительным управляющим вентилем 8 и через логический элемент «НЕ 9 - с дополнительным управляемым вентилем 10. Вторые входы вентилей 8 и W соединены с линией стробирующе-сдвигающих импульсов, а выходы этих вентилей - с входами управляемых вентилей 5 и 7.

Способ вычисления элементарных функций, используемый в работе предлагаемого

устройства, основан на известном методе линейно-кусочно аппроксимированных функций. По этому способу калсдая функция предварительно разбивается на зоны. При этом старшие разряды кода аргумента должны определять номера этих зон, тогда младшие - приращение в пределах выбранной зоны. Долговременное запоминающее устройство машины должно хранить дискретные значения вычисляе.мых функций, соответствующие

границам их зон.

При вычислении функций старшие разряды кода аргумента используются в качестве адреса ячеек долговременного запоминающего устройства. По этому адресу в регистры арифметического устройства на триггерах 1 и 2 перезаписываются коды вычисляемой функции в начале и конце функции выбранной зоны. Одновременно в регистр на триггерах 4 переписывается код младших разрядов аргумента. При сдвигании этого кода и считывании с регистра единиц открывается вентиль 8, а с его помощью - вентили 6, разрешая запись в сумматор на триггерах 3 кода функции начала выбранной зоны. При считывании из этого регистра нулей посредством элемента 9, реализующего функцию «НЕ, открывается вентиль W, а с его помощью - вентили 7, разрешая запись в сумматор кода функции конца выбранцой зоны. Последовательное суммирование со сдвигами этих кодов образует в сумматоре значение аппроксимируемой функции в заданной точке. Как видно, время ее вычисления соответствует времени выполнения одной неполной операции умножения. Предмет изобретения Арифметическое устройство специализированной цифровой вычислительной машины, содержащее сумматор-сдвигатель, счетные входы которого через две группы управляемых вентилей соединены с выходами двух регистров кодов слагаемых, логические элементы, отличающееся тем, что, с целью повышения быстродействия, оно содержит два дополнительных управляемых вентиля и сдвигающий регистр приращения кода зоны, выход которого непосредственно и через логический эл.ем-ент «НЕ присоединен к первым входам двух дополнительных управляемых вентилей,, к вторым входам которых подсоединена шина стробирующего сигнала, выходы дополнительных вентилей присоединены к соответствующим входам двух групп управляемых вентилей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| Устройство для деления | 1987 |

|

SU1541597A1 |

| Цифровое устройство для вычисления синусно-косинусных зависимостей | 1983 |

|

SU1104510A1 |

| Специализированный процессор | 1981 |

|

SU1023339A1 |

| Устройство для вычисления квадрата числа | 1983 |

|

SU1115051A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1103225A1 |

| Цифровой функциональный преобразователь | 1986 |

|

SU1361547A1 |

| Устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1494002A2 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

Авторы

Даты

1973-01-01—Публикация