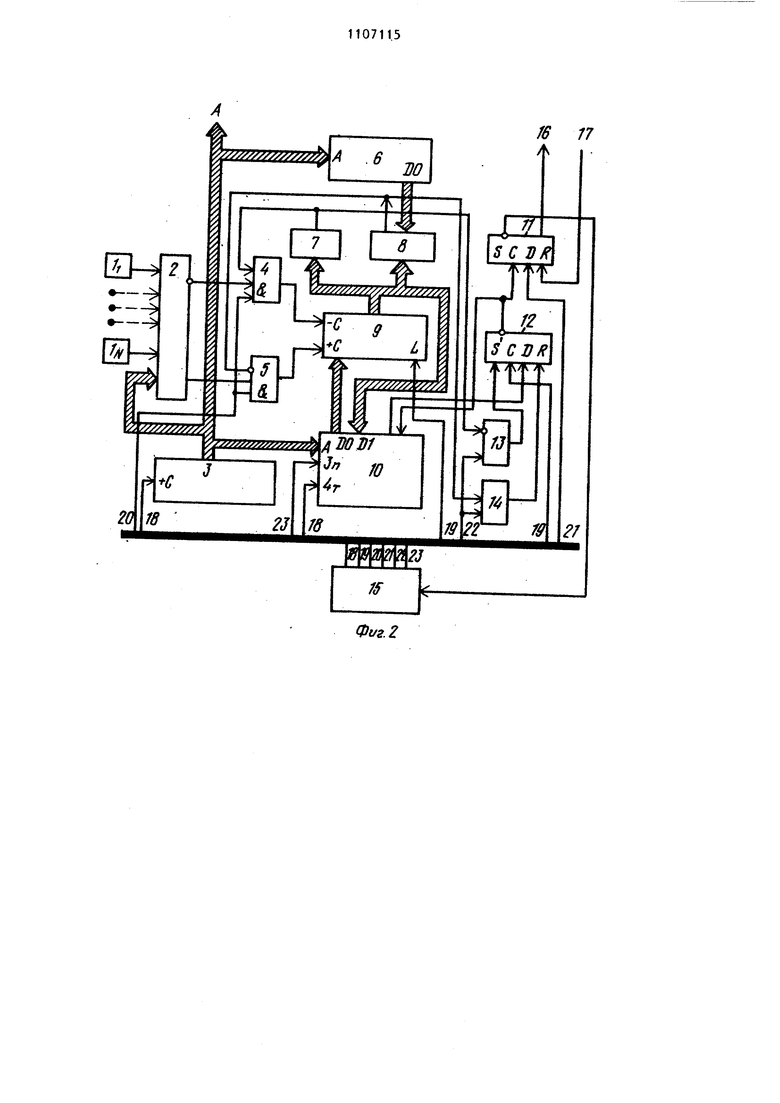

1сод формирователя временных интервалов соединен с третьими входами первого и третьего элементов И, четвертый выход формирователя временньпс интервалов соединен с Г -входом первого триггера, пятый выход фррмирователя временных интервалов соединен с вторым входом второго и первым прямь м входом четвертого элементов И, второй прямой вход последнего соединен с прямым выходом мультиплексора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1986 |

|

SU1314326A1 |

| Устройство для ввода информации | 1987 |

|

SU1471187A2 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| Устройство для обмена информацией между персональной ЭВМ и управляющим вычислительным комплексом | 1991 |

|

SU1838819A3 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ, содержащее входные датчики, формирователь временных интервалов, мультиплексор, первый и второй триггеры, счетчик адреса, выходы соединены с адресными входами мультиплексора, информационные входы которого соединены с выходами датчиков, отличающееся тем, что, с целью повышения достоверности вводимой информации путем уменьшения влияния помех, в него введены первый и второй блоки памяти, реверсивный .счетчик, первый, второй, третий и четвертый элементы И, схема сравнения, элемент ИЛИ, выходы счетчика адреса соединены с входами первого и второго блоков памяти и являются выходами адреса прерывания устройства, один из информационных выходов второго блока памяти соединен с D -входом второго триггера, а остальные информационные выходы второго блока памяти соединены с информационными входами реверсивного счетчика, выходы которого соединены с входами элемента ИЛИ, с информационными входами второго блока памяти и с первьми входами схемы сравнения, к вторым входам которой подключены выхо;ц | первого блока памяти, выход схемы сравнения соединен с первьв4 входом первого элемента И и с первым входом второго элемента И, выход которого соединен с R-входом второго триггера, инверсный выход которого соединен с одним из информационных входов второго блока памятни с С-входом первого триггера, R-вход которого является входом сброса прерывания устройства, прямой выход первого триггера является выходом запроса прерывания устройства, инверсный выход первого триггера соединен с входом остановки формирователя времен- ных интервалов, выход элемента ИЛИ .соединен с первым входом третьего элемента И и инверсньм входом четвертого элемента И, выход которого соединен с 5-входом второго триггера, О прямой выход мультиплексора соединен J с вторым входсм первого элемента И, выход которого соединен с суммирующим входом реверсивного счетчика, инверсный выход мультиплексор соедиел нен с вторьм входом третьего элемента И, выход которого соединен с вычитающим входом реверсивного счетчика, первый выход формирователя временных интервалов соединен с суммирующим входом счетчика адреса и с входом чтения второго блока памяти, вход записи которого соединен с шестым выходом формирователя временных интервалов, второй выход которой соединен с входом занесения реверсивного счетчика.и с С-входом второго триггера, третий вы

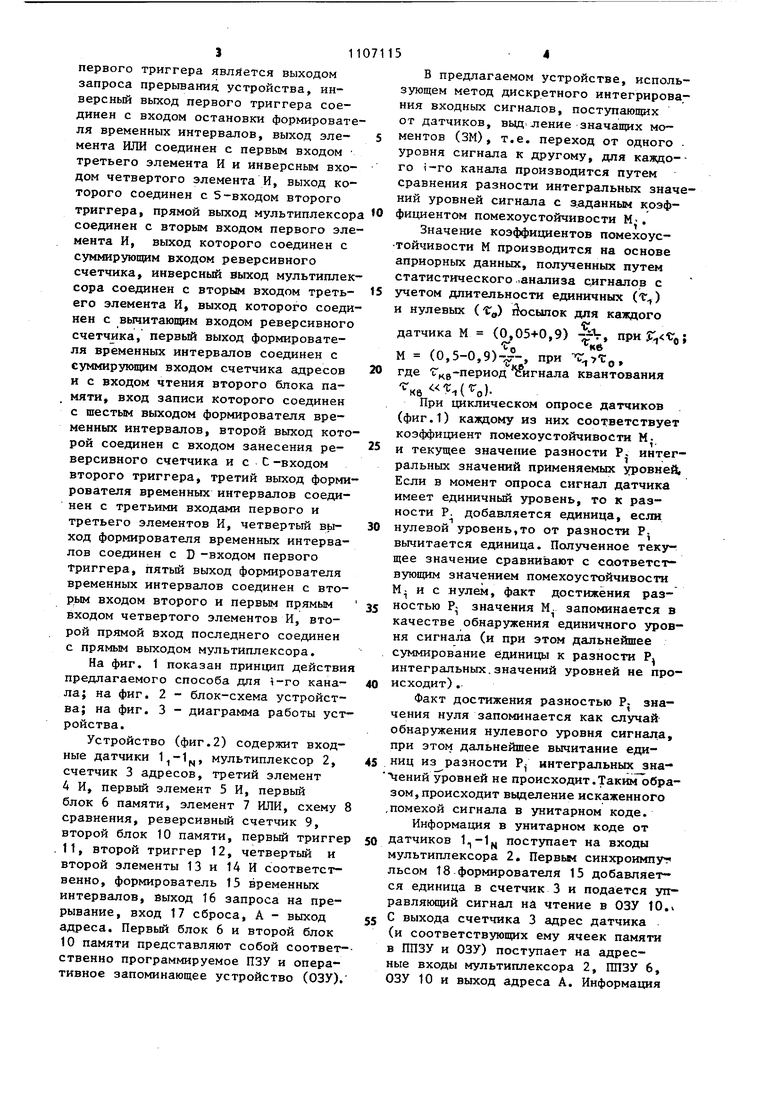

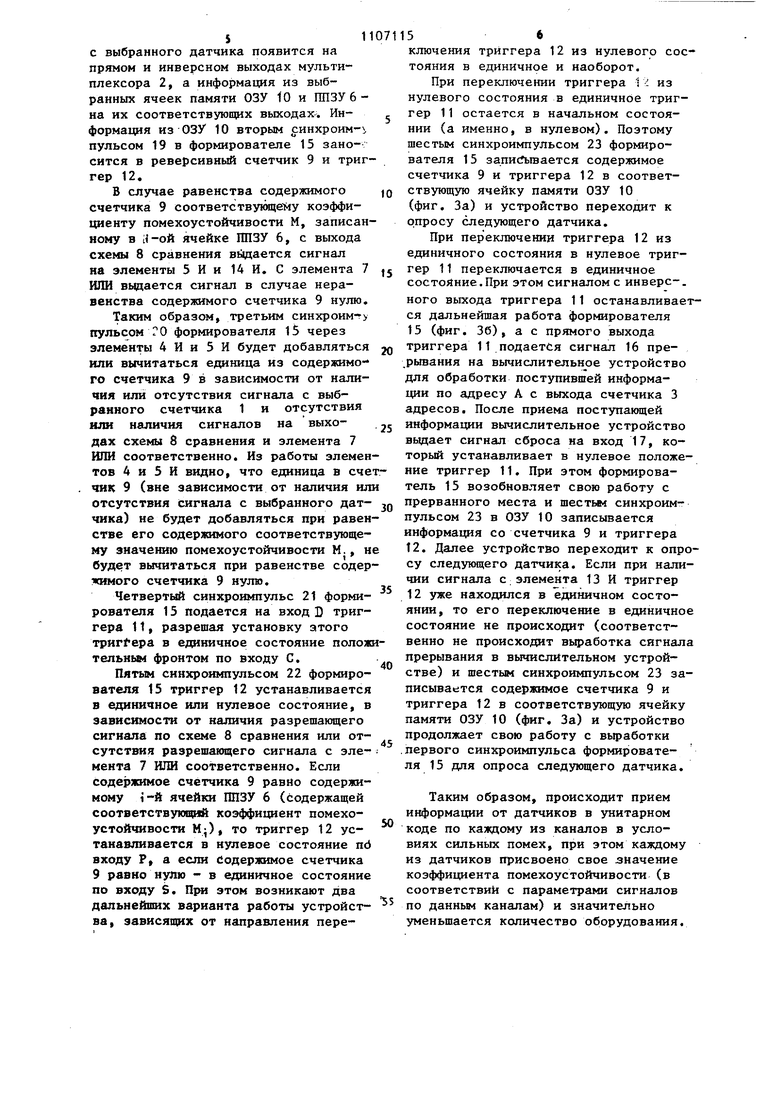

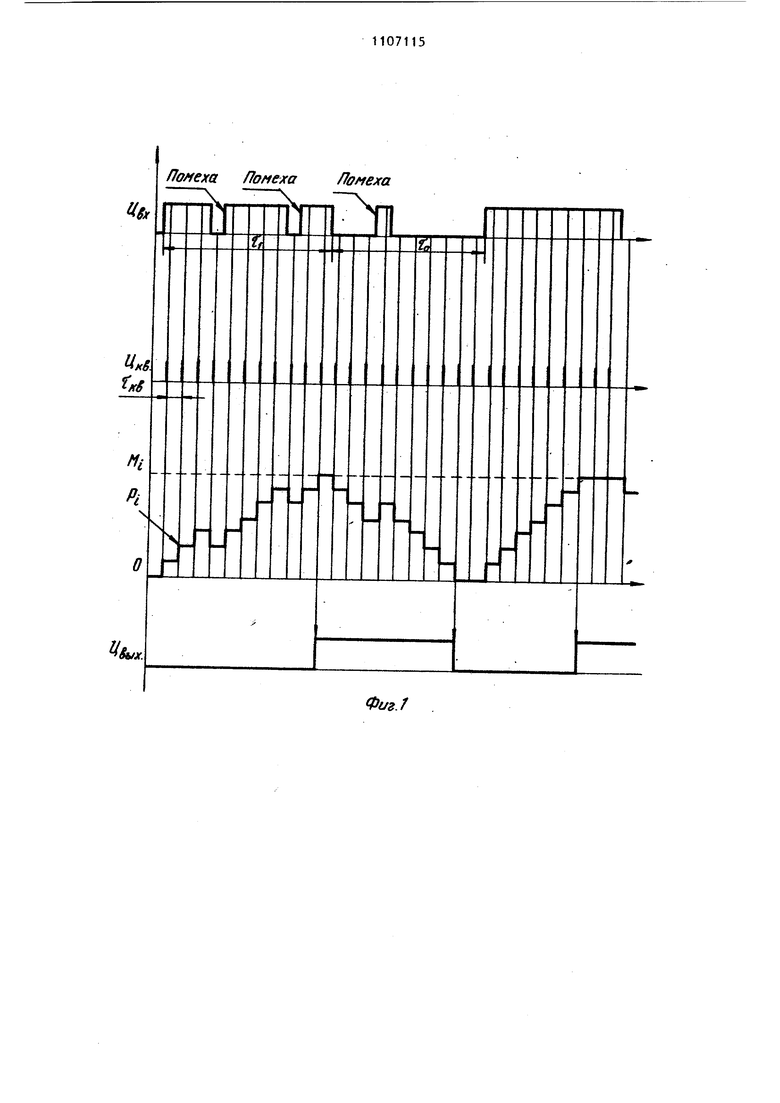

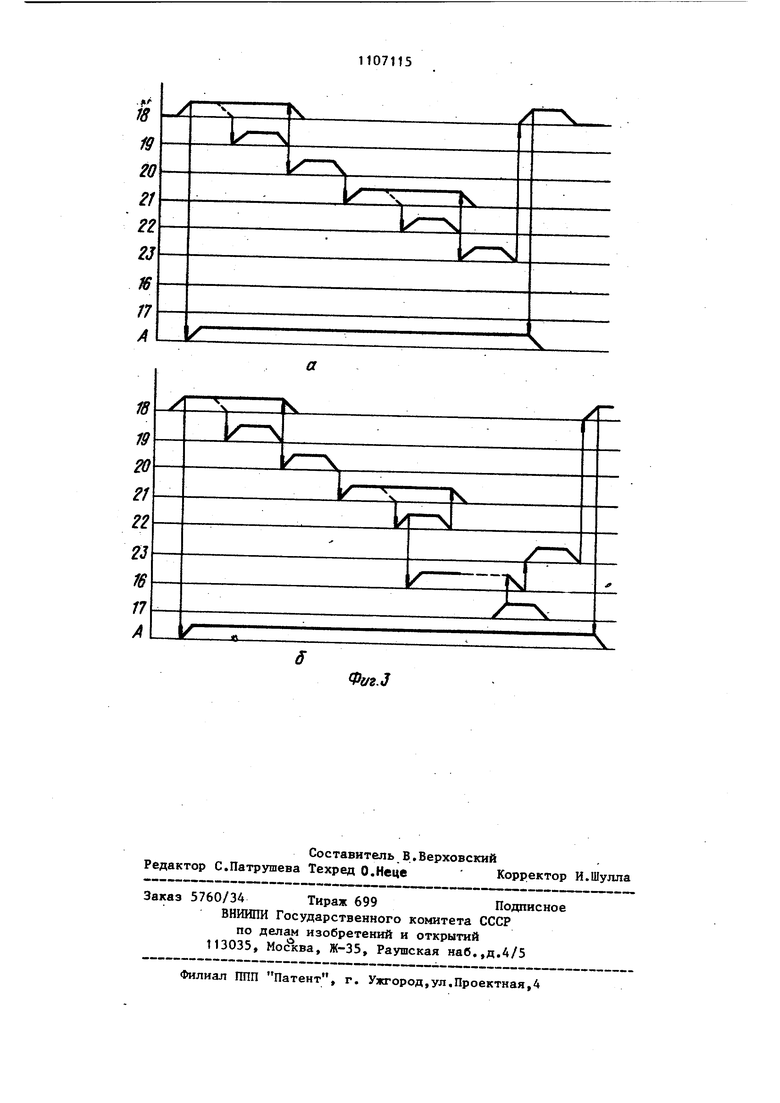

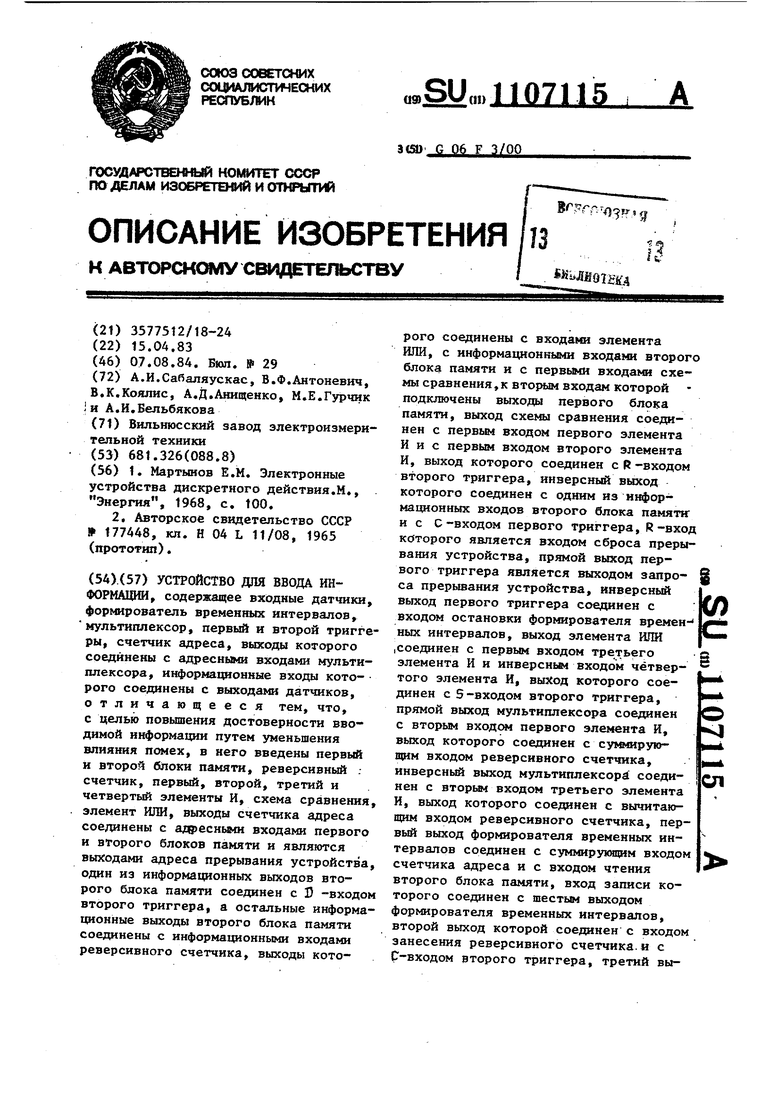

Изобретение относится к автоматике и измерительной технике и может быть использовано в систе ах учета и контроля потребления энергии. Известно устройство для ввода информации, содержащее последовательно соединенные датчик сигналов, аналоговые интеграторы, компараторы уровней СП. В данном устройстве для подавления импульсных помех, вызывакяцих дробление полезного сигнала и имеюащх более короткую длительность по отношению к нему, используют метод аналогового интегрирования. При этом для каждого датчика надо иметь отдельна интегри рующую цепь, что приводит к значитель ному увеличению оборудования и трудоемкости наладки и эксплуатации в многоканальных устройствах. Нестабильность номинальных величин интегрирующих элементов приводит к сниже,ншо достоверности приема информации. Наиболее близким решением к предлагаемому является устройство для реалиэащш дискретно-интегрального способа регистрации телеграфных посылок, содержащее датчик сигналов, формирователь временных интервалов, мультиплексор, схему совпадений, счетчик адреса, первый и второй триг геры« генератор, формирователи импул сов, выходы счетчика адреса соединены с адресными входами мультиплексора, информахщонные входы которого со единены с выходами датчиков, выход генератора через первый формировател соединен с входсм первого триггера первый и второй выходы которого чере формирователи соединены соответствен но с входом схемы .совпадения, входом схемы синхронизации, второй вход схе мы совпадения соединен с выходом вто рого триггера 12}. Однако известное устройство не обеспечивает задциты полезного сигнала от помех, вызывающих эффект дробления . Цель изобретения - повышение достоверности ввода информации путем уменьшения влияния помех. Поставленная цель достигается тем, что в устройство для ввода информации, содержащее входные датчики, мультиплексор, первый и второй триггеры, формирователь временных интервалов, с.четчик адреса, выходы котсфого соединены с адресньв4И входами мультиплексора, информационные входы которого соединены с выходами датчиков, дополнительно введены первый и второй блокк памяти, реверсивный счетчик, схема сравнения,первый,второй,третий и четвертый элементы И, схема сравнения, элемент ИЛИ,выходы счетчика адреса соединены с адресными входа ш первого и второго блоков памяти и являются выходами адреса прерывания устройства,один из информационных выходов второго блока памяти соединен с }- -входе второго триггера, а остальные информационные выходы второго блока памяти соединены с информационными входами реверсивного счетчика, выходы которого соединены с входами элемента ИЛИ, с информащюнными входами второго блока памяти и с первыми входами схемы сравнения, к вторым входам которой подключены выходы первого блока памяти, выход схемы сравнения соединен с первым входом первого элемента И и с первым входом второго элемента И, выход Которого соединен с R -входом второго триггера, инверсный выход которого соединен с одним из информационных входов второго блока памяти и с С-входом первого триггера,R-вход которого являе тся входом сброса прерывания устройства, прямой выход к первого триггера является выходом запроса прерывания устройства, инверсный выход первого триггера соединен с входом остановки формировате ля временных интервалов, выход элемента ИЛИ соединен с первым входом третьего элемента И и инверсным входом четвертого элемента И, выход которого соединен с S-входом второго триггера, прямой выход мультиплексор соединен с вторым входом первого эле мента И, выход которого соединен с суммирующим входом реверсивного счетчика, инверсный выход мультиплек сора соединен с вторым входом третьего элемента И, выход которого соеди нен с вычитающим входом реверсивного счетчика, первый выход формирователя временных интервалов соединен с суммирукицим входом счетчика адресов и с входом чтения второго блока памяти, вход записи которого соединен с шестым выходом формирователя временных интервалов, второй выход кото рой соединен с входом занесения реверсивного счетчика и с С-входом второго триггера, третий выход форми рователя временных интервалов соединен с третьими входами первого и третьего элементов И, четвертый выход формирователя временных интервалов соединен с D -входом первого Триггера, пятый выход формирователя временных интервалов соединен с вторым входом второго и первым прямым входом четвертого элементов И, второй прямой вход последнего соединен с прямым выходом мультиплексора. На фиг. 1 показан принцип действи предлагаемого способа для i-ro кана- ла; на фиг. 2 - блок-схема устройства; на фиг. 3 - диаграмма работы уст ройства. Устройство (фиг.2) содержит входные датчики ,v,, мультиплексор 2, счетчик 3 адресов, третий элемент 4 И, первый элемент 5 И, первый блок 6 памяти, элемент 7 ИЛИ, схему сравнения, реверсивный счетчик 9, второй блок 10 памяти, первый тригге 11, второй триггер 12, четвертый и второй элементы 13 и 14 И соответственно, формирователь 15 временных интервалов, выход 16 запроса на прерывание, вход 17 сброса, А - выход адреса. Первый блок 6 и второй блок 10 памяти представляют собой соответ ственно программируемое ПЗУ и оперативное запоминающее устройство (ОЗУ) В предлагаемом устройстве, использующем метод дискретного интегрирования входных сигналов, поступающих от датчиков, выд ление значащих моентов (ЗМ), т.е. переход от одного . ровня сигнала к другому, для каждо-го i-ro канал-а производится путем сравнения разности интегральных значеий уровней сигнала с заданным коэфициентом помехоустойчивости М-. Значение коэффициентов помехоусойчивости М производится на основе приорных данных, полученных путем татистического .анализа слгналов с четом длительности единичных (f) нулевых (Сд) йосылок для каждого V датчика М (,9) V, npHj; f(,; М (0,5-0,9), при где Тцр-период изгнала квантования при циклическом опросе датчиков (фиг.1) каждому из них соответствует коэффициент помехоустойчивости Ми текущее значение разности Р. интегральных значений применяемых уровней. Если в момент опроса сигнал датчика имеет единичный уровень, то к разности р. добавляется единица, если нулевой уровень,то от разности Р. вычитается единица. Полученное текущее значение сравнивают с соответствующим значением помехоустойчивости М- и с нулем, факт достижения разностью р. значения М запоминается в качестве обнаружения единичного уровня сигнала (и при этом дальнейшее суммирование единицы к разности Р интегральных.значений уровней не происходит) . Факт достижения разностью Р- значения нуля запоминается как случай обнаружения нулевого уровня сигнала, при этом дальнейшее вычитание единиц из разности PJ интегральных уровней не происходит. Таким образом, происходит вьщепение искаженного .помехой сигнала в унитарном коде. Информация в унитарном коде от датчиков поступает на входы мультиплексора 2, Первые синхроимпуг льсом 18 формирователя 15 добавляется единица в счетчик 3 и подается управляющий сигнал на чтение в ОЗУ 10. С выхода счетчика 3 адрес датчика (и соответствующих ему ячеек памяти в ПИЗУ и ОЗУ) поступает на адресные входы мультиплексора 2, ППЗУ 6, ОЗУ 10 и выход адреса А. Информация S11 с выбранного датчика появится на прямом и инверсном выходах мультиплексора 2, а информация из выбранных ячеек памяти ОЗУ 10 и ГШЗУ6на их соответствующих выходах Информация из ОЗУ 10 вторым синхроим-v пульсом 19 в формирователе 15 заносится в реверсивный счетчик 9 и триггер 12, В случае равенства содержимого счетчика 9 соответствугаде1 1у коэффициенту помехоустойчивости М, записанному в -ой ячейке ГШЗУ 6, с выхода схемы 8 сравнения видается сигнал на элементы 5 И и 14 И. С элемента 7 ИЛИ выдается сигнал в случае неравенства содержимого счетчика 9 нулю, Таким образом, третьим синхроим-г пульсом ГО формирователя 15 через элементы 4 И и 5 И будет добавляться или вычитаться единица иэ содержимого счетчика 9 в зависимости от наличия или отсутствия сигнала с выбранного счетчика 1 и отсутствия или наличия сигналов на выходах схемы 8 сравнения и элемента 7 ИЛИ соответственно. Из работы элемен тов 4 и 5 И видно, что единица в сче чик 9 (вне эависимости от наличия ил отсутствия сигнала с выбранного датчика) не будет добавляться при равен стве его содеряммого соответствующему значению помехоустойчивости М., н будет вычитаться при равенстве содер жимого счетчика 9 нулю, Четвертый синхроимпульс 21 формирователя 15 подается на вход D триггера 11, разрешая установку этого триггера в единичное состояние полож тельн1 м фронтом по входу С, Пятым синхроимпульсом 22 формирователя 15 триггер 12 устанавливается в единичное или нулевое состояние, в эависимости от наличия разрешающего сигнала по схеме 8 сравнения или отсутствия разрешающего сигнала с элемента 7 ИЛИ соответственно. Если содержимое счетчика 9 равно содержимому i-й ячейки ППЗУ 6 (содержащей соответствующий коэффициент помехоустойчивости М-), то триггер 12 устанавливается в нулевое состояние пб входу Р, а если Содержимое счетчика 9 равно нулю - в единичное состояние по входу S, При этом возникают два дальнейших варианта работы устройства, зависящих от направления пере56ключения триггера 12 из нулевого состояния в единичное и наоборот. При переключении триггера 1 . из нулевого состояния в единичное триггер 11 остается в начальном состоянии (а именно, в нулевом). Поэтому шестым синхроимпульсом 23 формирователя 15 запиЛгаается содержимое счетчика 9 и триггера 12 в соответствующую ячейку памяти ОЗУ 10 (фиг. За) и устройство переходит к опросу следующего датчика. При переключении триггера 12 из единичного состояния в нулевое триггер 11 переключается в единичное состойние.При этом сигналом с инверс-. ноге выхода триггера 11 останавливается дальнейшая работа формирователя 15 (фиг, 36), а с прямого выхода триггера 11 подается сигнал 16 прерывания на вычислительное устройство для обработки поступившей информации по адресу А с выхода счетчика 3 адресов. После приема поступающей информации вычислительное устройство вьадает сигнал сброса на вход 17, который устанавливает в нулевое положение триггер 11, При этом формирователь 15 возобновляет свою работу с прерванного места и шест1 1 синхроимпульсом 23 в ОЗУ 10 записывается информация со счетчика 9 и триггера 12, Далее устройство переходит к опросу следующего датчика. Если при наличии сигнала с элемента 13 И триггер 12 уже находился в единичном состоянии, то его переключение в единичное состояние не происходит (соответственно не происходит выработка сигнала прерывания в вычислительном устройстве) и шестьи синхроимпульсом 23 записывается содержимое счетчика 9 и триггера 12 в соответствующую ячейку памяти ОЗУ 10 (фиг. За) и устройство продолжает свою работу с выработки первого синхроимпульса формирователя 15 для опроса следующего датчика. Таким образом, происходит прием информации от датчиков в унитарном коде по каждому из каналов в условиях сильных помех, при этом каждому из датчиков присвоено свое значение коэффициента помехоустойчивости (в соответствий с параметрами сигналов по данньм каналам) и значительно уменьшается количество оборудования.

U$,

U,B

Hi

Pi

Фиг.7

Фиг. 2

Фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Мартьшов Е.М | |||

| Электронные устройства дискретного действия.М., Энергия, 1968, с | |||

| Облицовка комнатных печей | 1918 |

|

SU100A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-08-07—Публикация

1983-04-15—Подача