1 1зобт1етепие относится к областл аптома/гики и в.1Ч1и:лп гйлыю11 техпикгт и может obiTjj использовано в и зы- )ijc,,: .Hbix смстоыах с мик1:1пп{:)ограм-- iн;.}:1 :, i;r i.mj reTtjiei-u

).| лт-,0 ji3O(5 ieTe iiiJi является йот- - lueiiiie (;ыстродейств71я устройства,

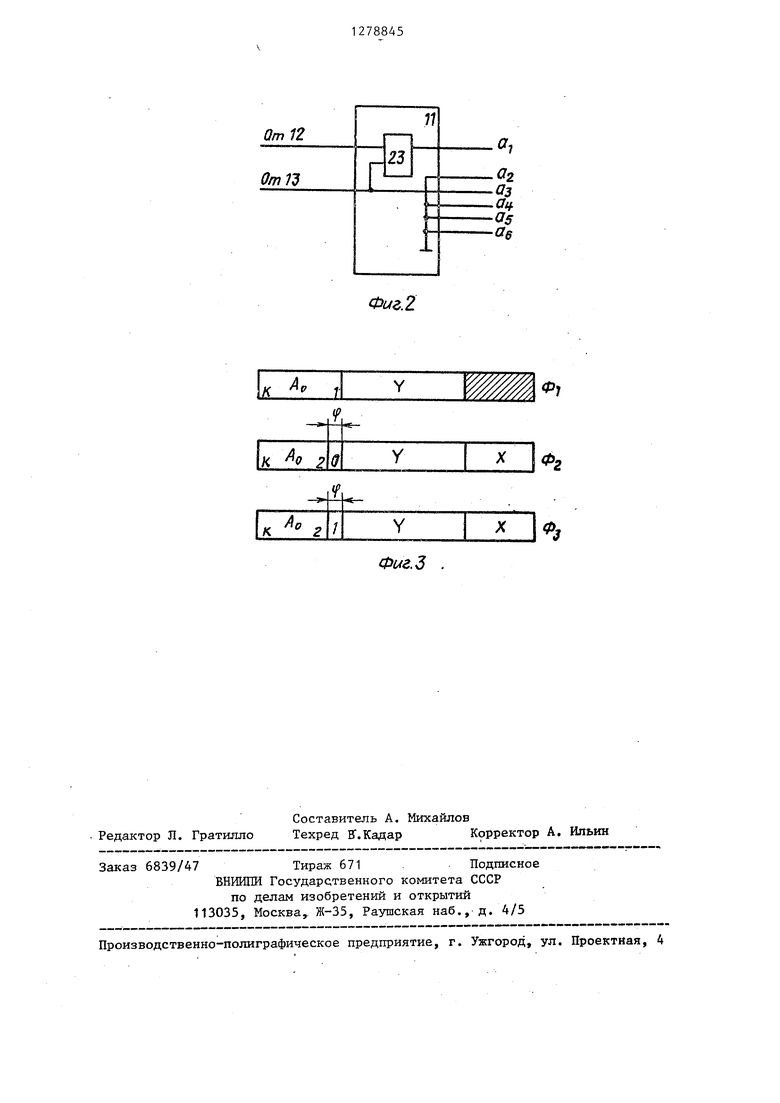

Иа );, 1 приведена фуь;кш-юпаль- пая схема предлагломого )олрог-рам ьпюго ус гронстт-:а упранлеиз я; лга , ф1 г, 2 фуикпиолальпаут схема шифратора; 1га фиг, 3 - ( лорматы 7еализуе.- ijiix м:прс 1окома71д,

Мнкгюпрограммное устроитеTHCJ, узг-- раЕЛоп1- я с контролем (фиг.. 1) содержит блок 1 памяти tIкpoкo a,ц, ттмею- п нй втлхол 1, М1- крооперац1-п 5 льпсод 1 КО/1Я л(. Т ичес1 Пх усло.) и- Я11 Х Д 1 стат И Их -.тазиядов лдргг о. iieruc i n 2 (;а„ тлс 3 г- тгиоол ча11ий,. i мртЪ : плт :соп ; . то р тческих усм юлий, ко(ьгутатор 5 , .1утатор б мпадлюгс; адтизса , триггер / С1шибки, тр 1гг ч р 8 ус ка J г еператор 9 тякт| Ч Ь ч импул1 с,о7з с 9/ и вто:: Ым 9,., ucoii - ; г.yi-iMnTori 10, шифратор 11, л ерв -rf ; 1/: и втэг оп 13 дл:е- мопты И; олемаит И--11Е 1 :. пторой 15 г:: иерв ь : (- ИП 1., вход 17 хода г;омалд;л у стройстна, вход пуска, У: i -:v: x--i4;a кход 19 .логп- ус. кити/ J выход 20 ми д;оопара-11т;|т ycTlK/jiCTSa, ЛЬ ХОДМ 21), --Vflj, MJ K -

pooriori i ,г.й ггот-ца команды и колця работы ::.оогуг1ХХ1 реннОэ выхо;: ; 21 тчибки устрохо ) ; -, льгход 27. мл;1Д 1аго разряда a,u)cc;i. ojToxa 1 па -|;г ги шкрокомапд,,

5

0

а с выхода 20 регистра 3 снимается единнчттый сигна л.

Работа уст 5ойства иачи1 ается после постзптления на вход 18 сигнала по которому устанавливается в един1-тл пое состояние три1 гер 8. Генератор 9 начинает работу. По первому тактовому ргмпульсу с выхода 9 гене- ратора 9 в регистр 2 заносится код команды с входа 17, при единичном сигнале - с выхода 20,; регистра 3,

По коду,, записанному в регистр 2, из блока 1 пдмятг; выбирается MHKDGKO- манда,.

В первом реет- на (формат линейной микрокомапды приведен на фиг. 3) операп,ггон,на,;: часть Т кода л,инейной ,1 кро соманл;,1 по задлему фронту второ- I o ,такто;х:1го импульса с вь сшда 9

3

на выход, 20 устро,йствао Старшие разряды адреса очере;дной шкрокоманды поступают па сумматор 10. 1 1лад1дий ра,зряд адреса о тередной микрокоманды через кo г Iiтaтop 6 при отсутствии сиг сигнала ОШ Лбки с выхода И-НЕ 1 поступает i,ia с,оответет,ву1оищй вход cyi-c ia- тора 10,

Лдрес очередной микрокоманды без . изменения поступает лерез комкута,тор

.5

ре лтс гра 3 па илп:орг 1адионныи вход регистра 2 адреса и т.д. При реализации Bcejr .липейньп;: микрокоманд, устройство функционирует а/ииюпично описанному ал,гор1км;;.

Во втором г)е ;име (формат обыл юй

г.икрокомандъ ветглелия

(

прлп зеден

40

,та сЪи г, 3) код прг,пзет яекого ,логиггес-

|р1,лл;1,1 а,(;1 1:;е MnK : onporpaKMv;oe уст,- ройствс уг-.раплепкк работ;:1ет в реал1-1;5а,15-п:1 .гл нейпы):участков микрог рог

р a.t--Qi J

кия; jiea.iTJiaaiiiit:; фра,Г1:ен г :о микропрограмм, in-iOKiniix :,xo;-v , Б операторной лерЯ Тгпе (У1 двух усло:впы, 7:1ер :пии,, без вед; :;: ил пусть ;,: 1 жрокопаид,; ор1 ани:;г 1 1К оитроля перехода от iiporpai-fl-inoi o к Ь Шкролрозл аим-тому уровню.

Пер(-,д ,чалом паботы з гементы схеьул 1:рг1педепы я нл-лезое со : то,м:гие, .

,м,яти т оступает н,-- вдрестк-лй вход муль- типлексопа ,. С ,т,,пфог,ч апд1он,ного входа ,мульт1птлексора 4 вь бирается значение i ;io:i3epHei: oro лог1:ческого условия,, j OTopoe п,остз пает на соответст)зугс1Г ;ие ,вхол,гл первого 12 и Бторопо 13 элементов И„ Пулевое и.1:{и единичное значз Hi-ie младшег о разряда -адреса с выхода 22 блок-а I в амятк поступает на соот- ; етству, входы первого 12 и второго 13 элементов И,

Лдрес очс редной микроко,1анды ределяется выражение , Л + 1 при (X - 1) и (if 0) ,

Все обычные микрокогшнды ветвления реализуются aiiajiorntiHo,

В третьем pexcniAse (формат peajjnsy- е,юй м,икро сомат1Д1.; яетвлени51 2 нред312

ставлен на фиг, 3) возникла необходимость реализовать фвагмент микропрог ра.ммы, имеющей схождения от двух условных вершин У) 1. Аналогично рассматриваемому примеру адрес смеше- ния равен 4. Код операционной части микрокоманды поступает на информационный вхо д регистра 3 микроопераций и на выход 20 микроопераций устройства по заднему фронту второго так- тового импульса с выхода 9у генератора 9. Код проверяемого логического условия с выхода 1 блока 1 памяти поступает на мультиплексор 4, элемент I-fflH 15 и элемент И-НЕ 14. Зна- чение проверяемого логического условия с выхода мультиплексора 4 поступает на соответствующие входы первого 1 2 и второго 13 элементов И. Сигнал с выхода элементов ИЛИ 15, И-НЕ 14 и значение младшего разряда адрес с выхода 22 блока 1 памяти поступают на соответствующие входы коммутатора 6, первого 12 и второго 13 элементов И, Единичное значение младше- го разряда адреса с выхода 22 и отсутствие сигнала ошибки с элемента И-НЕ 14 закрывают коммутатор 6. Значение младшего разряда адреса с выхода 22 закрывает первый элемент И 12. Сигнал с выхода элемента И 13 поступает на второй вход шифратора 11. С выходов а , и а 5 шифратора 11 (фиг. 2) считывается адрес смещения на сумматор 10. На первый вход сум- матора 10 поступает код адреса очередной микрокоманды с выхода 1 блока 1 памяти.

Таким образом, адрес очередной микрокоманды определяется выражением

А А + А i+i о допСформированный адрес А ;, поступает на соответствующий вход коммутатора 5 адреса, при нулевом сигнале с выхода 20, конца команды на регистр 2 адреса и позволяет нам развязать фрагмент микропрограммы, описанный ЛСА, без введения пустой микрокоманды.

Далее устройство функционирует аналогично описанному алгоритму.

В четвертом режиме организация контроля перехода от программного к микропрограммному уровню осуществляется аналогично известному устройству.

0 5 0 5 0 5

0

5

5

54

В общем случае, в поле логических условий каждой начальной микрокоманды заносится фиксированный код, который соответствует номеру неиспользуемого логического условия.

Пусть при реализации микропрограммы проверяется десять логических условий. Для их кодирования требуется четыре разряда. Шесть оставшихся кодов могут быть зафиксированы. Ими могут быть, например, коды 1011, 1100,...,1111. Предположим, что в качестве такого фиксированного кода выбран код 1100. Тогда он записывается в поле логических услов1п4 всех начальных микрокоманд. После считьша- ния каждой первой Ш1крокоманды проверяется содержимое поля кода логических условий. Если оно отлично от значения фиксированного кода 1100, то это означает, что код, поступивший на вход устройства и воспринимаемый им как начальный адрес микропрограммы, не является кодом операции вследствие его сбоя или отказа аппаратных (программньк) средств верхнего уровня.

В этом случае устройством формируется сигнал ошибки и его работа прекращается. Работа устройства прекращается также и при наличии единичного сигнала с выхода 202 конца работы регистра 3.

изобретения

MiiKponporpaMMHoe устройство управления с контролем, содержащее блок памяти микрокоманд, регистр адреса и регистр микроопераций, М5,шьтиплек- сор логических условий, комьгутатор адреса, триггер ошибки, триггер пуска, генератор тактовых импульсов, элемент И-НЕ, первьп элемент lOTI-I, причем вход пуска устройства соединен с входом установки в единичное состояние триггера пуска, выход которого соединен с входом запуска генератора тактовых импульсов, первый и второй выходы которого соединены соответственно с входами синхрониза- lyjui регистра адреса и регистра, микроопераций, вход кода команды устройства соединен с первым информационным входом коммутатора адреса, выход признака конца команды регистра микроопераций соединен с прямым и инверсным управляющи ш входами коммутатора адреса, выход которого соединен с информационным входом регистра

адреса, выход которого соединен с адресным входом блока памяти микроко.манд, выход поля шкpooпepau;ий которого соединен с информационным входом регистра микроопераций, выход которого соединен с выходом микроопераций устройства, выход поля логических условий блока памяти микрокоманд, и вход логических условий устройства соединены соответственно с управляю- Ещм и информационным входами мультиплексора, выход поля логических условий блока памяти микрокоманд соединен с входами элемента И-НЕ/ выход которого соединен с информационным входом триггера ошибки, выход признака йонца команды регистра микроопераций соединен с входом синхронизации: триггера ошибки, выход признака конца работы регистра микроопераций и выход триггера ошибки соединены соответственно с первым и вторьтм входами первого элемента ШШ, выход которого соединен с входом установки в О триггера пуска,- выход триггера ошибки соединен с выходом ошибки устройства, отличающееся тем, что, с целью повьш1ения быстродействия, в него введены второй элемент ИЛИ, коммутатор младшего разряда ад.раса, первый и второй элементы И,

5

0

5

ашфратор, сумматор, причем поля логических условий блока памяти микрокоманд соединен с входами второго элемента ИЛИ,, выход которого соединен с. первым-инверсным управляющим входом коммутатора младшего разряда адреса и с первыми входами первого и второго элементов И, выход старших разрядов поля адреса блока памяти микрокоманд соединен с первым входом сумматора, выход младшего разряда поля адреса блока памяти ьшкрокоманд соединен с первым и вторым информационными входами кoм iyтaтopa младшего разряда сщреса, с инверсньм входом первого элемента И и с вторьп- входом второго элемента И, выход мультиплексора логических условз-ш соединен с третьим входом первого элемента И и с четвертым входом второго элемента И, выход элемента И-ЫЕ соединен с вторь м инверсным управляющим входом кo мyтaтopa младшего разряда адреса, с вторым входом первого элемента И и с третьим входом второго элемента И, выходы первого и второго элементов И соединены соответственно с первым и вторым входами ишфратора,, выход которого соединен с вторым входом сумматора, выход коммутатора младшего

разряда адреса соединен с первым входом су 1матора, выход которого соединен с вторым )нформационньм входом ког-1мутатора адреса.

- й-г.;

0we.2

Фиг.З .

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Устройство для программного управления и контроля | 1985 |

|

SU1280574A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство с контролем | 1984 |

|

SU1208556A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1476465A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1649539A1 |

Изобретение относится к области автоматики и вычислип ельной техники и может быть использовано в ЭВМ и вычислительных системах .с микропрограммным управлением. Цель изобретения - повышение быстродействия устройства. Микропрограммное устройство управления с контролем содержит блок памяти микрокоманд, регистр адреса, регистр микроопераций, мультиплексор логических условий, коммутатор адреса, коммутатор младшего разряда адреса, триггер ошибки, .триггер пуска, генератор тактовых импульсов, сумматор, шифратор, второй и первый элементы И, элемент И-НЕ, второй и первый элементы ИЛИ. Указанная цель достигается с помощью указанной совокупности признаков. 3 ил. I (О

| Майоров С.А., Новиков Г.И | |||

| Структура электронных вычислительных машин | |||

| Л.: Машиностроение, 1979 | |||

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-23—Публикация

1985-06-03—Подача