(54) УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНО-ПАРАМЕТРИЧЕСКОГО КОНТРОЛЯ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционально-параметрического контроля электронных блоков | 1982 |

|

SU1104520A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1983 |

|

SU1157544A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1985 |

|

SU1302220A2 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1987 |

|

SU1562864A1 |

| Устройство для функционального контроля логических элементов | 1983 |

|

SU1327108A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1067453A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для обнаружения ошибок в блоке постоянной памяти | 1984 |

|

SU1246141A1 |

| Устройство для функционального контроля логических элементов | 1984 |

|

SU1226468A1 |

1

Изобретение относится к вычислительной и управляющей технике и автоматике и может быть использовано для входного контроля логических элементов, в том числе интегральных микросхем и потребителей, для функционально-параметрического контроля печатных плат с логическими элементами изготовителями логических устройств автоматики и вычислительной техники-, а также для функционально-параметрического контроля интегральных микросхем, включая контроль при разбраковке пластин, при ресурсных и прочих испытаниях, в особенности, когда необходима непрерывная фиксация функционирования микросхем.

Известны устройства с программным управлением, в том числе цифровые вычислительные машины, которые применяются в совместной цифровой вычислительной и управляющей технике для контроля правильности функционирования логических элементов, для входного (у потребителя) и выходного (у изготовителя) контроля интегральных логических микросхем. Работа этих устройств основана на использовании .традиционных способов контроля функционирования и измерения электрических параметров (параметрического контроля) путем формирования программой последовательностей стимулирующих воздействий и анализа каждого отклика на каждом выходе контролируемого логического элемента или микросхемы I.

Однако такой подлод к рещению проблемы контроля логических элементов требует использования запоминающих устройств больщой емкости для хранения программ стимуляции и реакций выходов или размещения этих данных на бумажных носителях, что делает эти устройства дорогостоящими, ненадежными в эксплуатации и плохо приспосабливаемыми для контроля новых логических элементов и микросхем. Кроме того, высокая стоимость такого оборудования для

5 функционально-параметрического контроля микросхем, т.е. его сложность, высокая трудоемкость и материалоемкость, не позволяет оснастить им большое количество организаций и предприятий, изготавливающих разнообразную электронную аппаратуру автоматики и вычислительной техники на основе логических элементов и микросхем.В результате отсутствия массовой,простой и дещевой аппаратуры входного контроля логических элементов и микросхем при изготовлении цифровых устройств имеют место большие непроизводительные затраты, связанные с поиском, локализацией и заменой неработоспособных элементов в изделии. Именно поэтому предприняты попытки создания достаточно простых, дешевых, легко производимых в массовых количествах и легко обслуживаемых устройств для функционального контроля логических элементов, в том числе интегральных микросхем. При этом в качестве тестируюш,их стимуляторов стремились использовать простые аппаратные средства в виде счетчиков, а в качестве регистраторов выходных двоичных векторов или сравнение с эталонным, заведомо годным логическим элементом, или счетчики числа переключений в выходном векторе, или сумматоры их составляюш,их. Наиболее близким по техническому решению к изобретению является устройство функционального контроля логических элементов, в том числе интегральных логических микросхем, отличительной особенностью которого является использование в качестве стимулятора входных воздействий генератора кодов, построенныго на основе двоичного счетчика, который последовательно во времени перебирает все возможные комбинации входнь1х векторов для контролируемого элемента. Регистрация выходного двоичного вектора производится с помощью двоичного сумматора с циклическим переносом. Контрольная сумма сравнивается с результатом, полученным при контроле заведомо годных аналогичных элементов 2. Однако данное устройство не может быть использовано для функционального контроля большого класса схем, в том числе логических интегральных микросхем (как правило, средней и высокой стегюни интеграции), отличительной особенностью которых является полифункциональность и, как следствие этого, наличие специальных управляющих входов, являющихся несовместимыми, т.е. таких входов, на которые внутренней структурой схемы не допускается одновременная подача действуюш.их значений сигналов (например, вход1з1 прибавления и вычитания в реверсивных счетчиках, входы aciiiixpoHiioio гашения и синхронизированной установки в триггерах, входы гашения и :к грузки р регистрах и т.п.). Если в кач;ч И.. С1 ;мулятора входных воздействий .1я гмкмх схем используется только счет iiiv,(. в некоторые моменты времени в реv.iui.ne цпклического перебора всех возм(/к;1ых состояний счетчика состояния раз.iiiiHbix выходов счетчика обязательно совпадут между собой, т.е. сформируются несовместимые входные воздействия, которые влекут за собой недетерминированное поведепне испытуемого логического элемента и, KTiK следствие, невозможность его объектив1()() коитро.1Я. Кроме того, данный прибор не реализует функций параметрического контроля логических элементов и интегральных микросхем в «наихудших электрических режимах входов и выходов контролируемых логических элементов. Цель изобретения - повышение достоверности результатов контроля и увеличение быстродействия устройства. Поставленная цель достигается тем, что в известное устройство, содержащее сигнатурный анализатор и последовательно соединенные тактовый генератор, первый счетчик и коммутатор-преобразователь, введены мультиплексор, второй счетчик и дешифратор, входами и выходами подключенный через коммутатор-преобразователь к соответствующим выходам первого счетчика и входам контролируемого логического элемента соответственно, информационный вход сигнатурного анализатора подключен к выходам контролируемого логического элемента через последовательно соединенные коммутатор-преобразователь и мультиплексор, адресные входы которого через коммутаторпреобразователь соединены с выходами второго счетчика, счетный вход которого через коммутатор-преобразователь подключен к выходу старшего разряда первого счетчика. Устранение непосредственного соединения выходов первого счетчика с несовмести: мыми входами контролируемого логического элемента и подача на эти входы тестовых сигналов от дешифратора разделенных во времени и принципиально несовпадающих стимулов обеспечивает возможность проведения полного функционального контроля логических элементов с несовместимыми входами, а подача всех стимулирующих сигналов через коммутатор-преобразователь уровней входов (выходов), который коммутирует все цепи и формирует «наихудшие условия входных сигналов и «IMKH и условия максимальных нагрузок выходов для этих состояний, обеспечивает возможность проведения одновременно с функциональны.м и параметрического контроля, так как сколько-нибудь значительные изменения электрических параметров входов (повышенные токи) и выходов (повышенный «Одог- и пониженная «IAOT ) контролируемого логического элемента приведут соответственно к выходу на пределы «WH выходных или входных сигналов, т.е. к изменению выходного двоичного вектора, что и фиксируется регистратором, в качестве которого применен сигнатурный анализатор. Устранение необходимости регистрации выходного двоичного вектора на каждом выходе контролируемого многовыходного логического элемента с помощью мультиплексора, адресные входы которого «перебираются вторым счетчиком, запускаемым от старшего разряда первого счетчика, а мультиплексируемые входь соединены (через коммутатор-преобразователь) соответственно со всеми выходами контролируемого многовыходного логического элемента, поз воляет значительно повысить быстродействие системы контроля, поскольку последовательно образованный всеми выходами выходной двоичный вектор при циклической работе первого счетчика через единственный выход мультиплексора подается на сигнатурный анализатор.

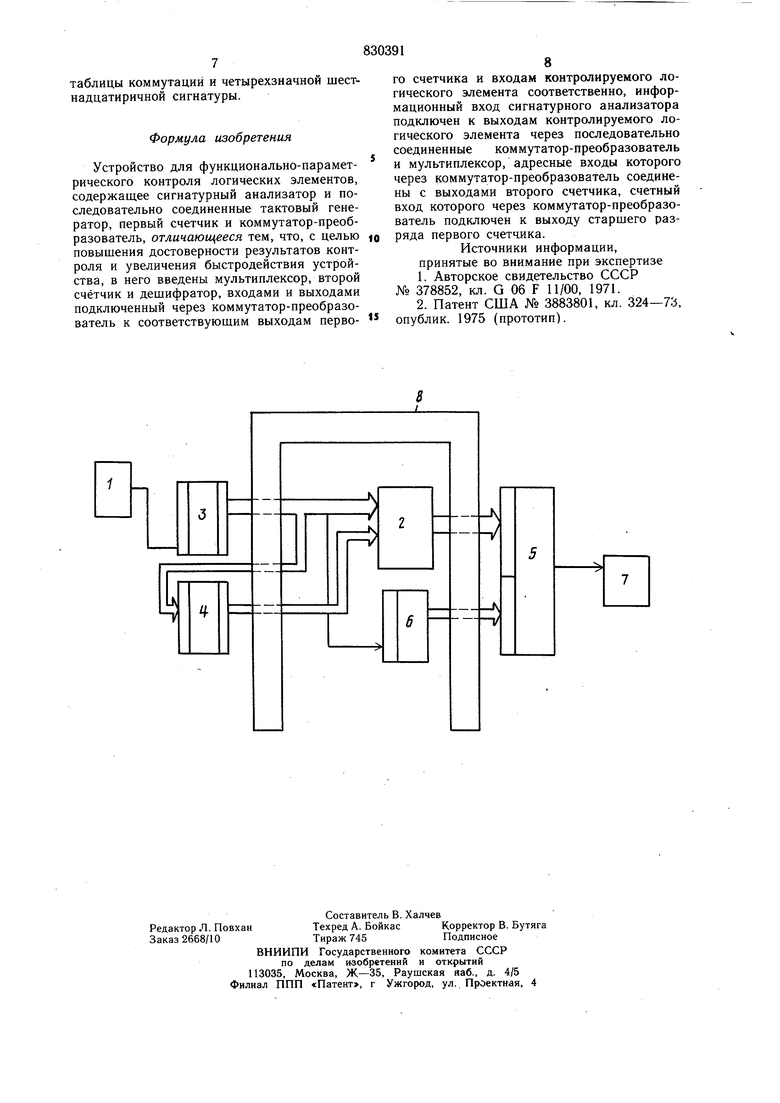

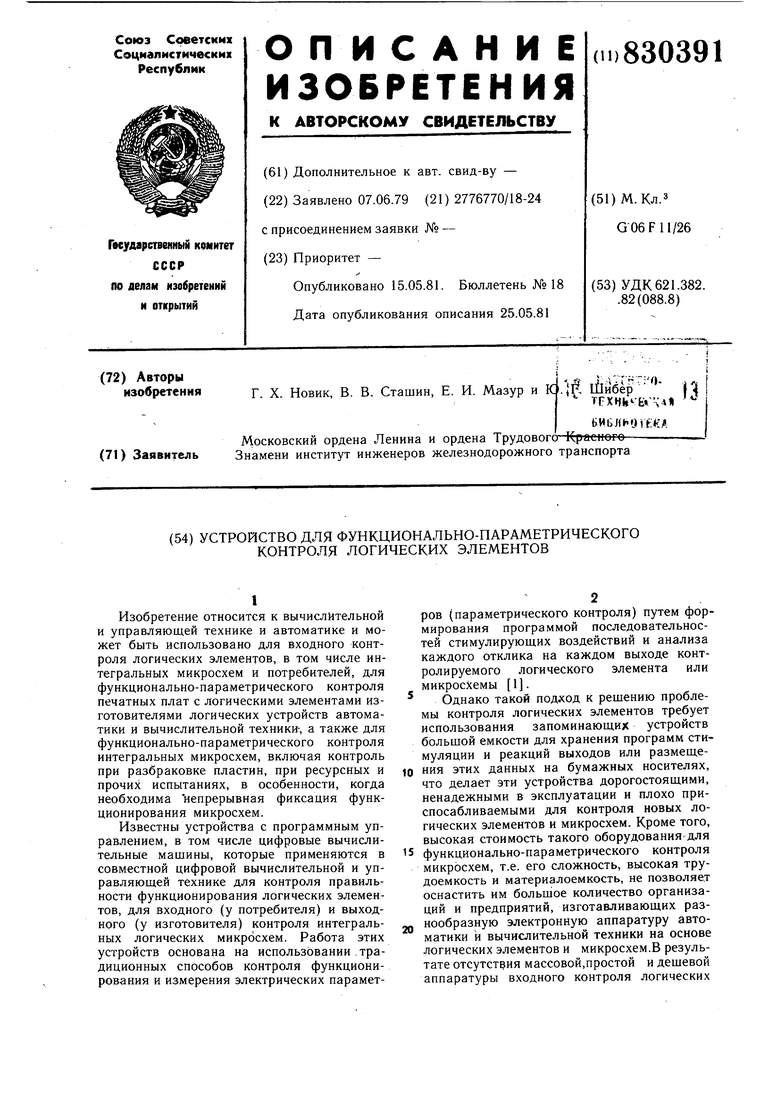

На чертеже поедставлена структурная схема устройства (с разнесенным изображением коммутатора-преобразователя для лучшего показа работы схемы).

Устройство содержит тактовый генератор 1, который обеспечивает тактовые синхросигналы максимальной рабочей частоты, необходимой для работы контроля прямого логического элемента 2, первый счетчик 3, предназначенный для обеспечения перебора входных тестовых последовательностей, дешифратор 4, необходимый для формирования тестовых сигналов для несовместимых входов контролируемого логического элемента 2, мультиплексор 5, необходимый для мультиплексирования выходов контролируемого многовыходного логического элемента 2, второй счетчик б, осуществляющий перебор адресных входов мультиплексора 5, сигнатурный анализатор 7, являющийся регистратором выходных двоичных векторов контролируемого логического элемента 2, коммутатор-преобразователь 8, который обеспечивает проводную коммутацию выходов счетчика-стимулятора 3 на совместимые входы контролируемого логического элемента 2 и на соответствующие входы дещифратора 4, выходы которого также е помощью коммутатора-преобразователя 8 коммутируются на несовместимые входы контролируемого логического элемента 2. Кроме того, коммутатор-преобразователь 8 обеспечивает проводную коммутацию выходов элемента 2, выходов счетчика 6 на входы мультиплексора 5, а также коммутацию уровней питания на соответствующие выводы контролируемого элемента 2. Коммутатор-преобразователь 8 помимо этого содержит схемы преобразователей уровней входов-выходов, т.е. цепи, имитирующие входные сигналы ОМАКС «IMMH максимальные нагрузки выходов крнкретного контролируемого логического элемента 2. Коммутатор-преобразователь 8 в общем случае является индивидуальным для каждого конкретного логического элемента 2, хотя в случае общей цоколевки корпуса (платы) и общей элементной базы для нескольких логических элементов может быть использован один коммутатор-преобразователь.

Устройство работает следующим образом.

При контроле с помощью предлагаемого устройства конкретного элемента 2 его подключают через коммутатор-преобразователь

8 к счетчику 3, дешифратору 4 (при необходимости) и генератору 1 (входы), и к мультиплексору 5 (выходы). Одновременно коммутатор-преобразователь 8 (реализуемый в виде разъемной колодки с пассивными

проводными перемычками и при необходимости с отдельными активными элементами типа, например транзисторов, для контроля схе.м ТТЛ, расширяемых по ИЛИ клапанов интегральных схем, инверторов и т.п.), подключенный к устройству, обеспечивает необходимую для контроля конкретного логического эле.мента коммутацию соответствующих разрядов счетчика 2 к входам дешифратора 4, счетчика 6 к входам мультиплексора 5. Таким образом, два разъемных соединения обеспечивают все операции подготовки к работе, после чего включается генератор 1, запускается на максимальной частоте счет чик 3 и соответственно дешифратор 4 и счетчик 6, благодаря чему осуществляется полный перебор всех необходимых стимулирующих воздействий для элемента 2, выходной двоичный вектор которого, образованный последовательным совмещением выходных векторов каждого из выходов элемента 2 на тактовую последовательность через мультиплексор а, регистрируется анализатором 7 и полученная сигнатура сравнивается с расчетной (или эталонной). При этом сравнение может производиться «вручную оператором всех эле.ментов сигнатуры или последняя может быть «распаяна на

коммутаторе-преобразователе 8, и тогдь результатом сравнения является единственный сигнал «Годен/Не годен. При этом jx ализ-уются все известные возможности я преимущества сигнатурного анализатора и is частности, контроль нестабильных сигнатур. Использование предлагаемого устройства функционально-параметрического контроля логических элементов и инте1ральных логических микросхем обеспечивает по сравнению с известными возможность полного функционально-параметрического контроля логических элементов и интегральных .микросхем, в том числе полифункциональных СИС и БИС с системой несовместимых управляющих входов, без необходимости использования цифровых вычислительных машин и перфорированных или магнитных носителей программ стимуляции и анализа реакций проверяемых элементов, а на основе простых аппаратных средств в составе генератора стимулов, коммутатора и сигнатурного

анализатора; возможность функционально-параметрического контроля интегральных микросхем любых серий с минимальной перенастройкой, а также возможность функционально-параметрического контроля логических элементов и узлов на интегральных микросхемах.

Кроме того, хранение с.хемы стимуляции и реакций (сигнатур) контролируемых элементов выполняется документально в виде

таблицы коммутации и четырехзначной шестнадцатиричной сигнатуры.

Формула изобретения

Устройство для функционально-параметрического контроля логических элементов, содержащее сигнатурный анализатор и последовательно соединенные тактовый генератор, первый счетчик и коммутатор-преобразователь, отличающееся тем, что, с целью повышения достоверности результатов контроля и увеличения быстродействия устройства, в него введены мультиплексор, второй счётчик и дешифратор, входами и выходами подключенный через коммутатор-преобразователь к соответствуюшим выходам первоГО счетчика и входам контролируемого логического элемента соответственно, информационный вход сигнатурного анализатора подключен к выходам контролируемого логического элемента через последовательно соединенные коммутатор-преобразователь и мультиплексор, адресные входы которого через коммутатор-преобразователь соединены с выходами второго счетчика, счетный вход которого через коммутатор-преобразователь подключен к выходу старшего разряда первого счетчика.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-05-15—Публикация

1979-06-07—Подача