со

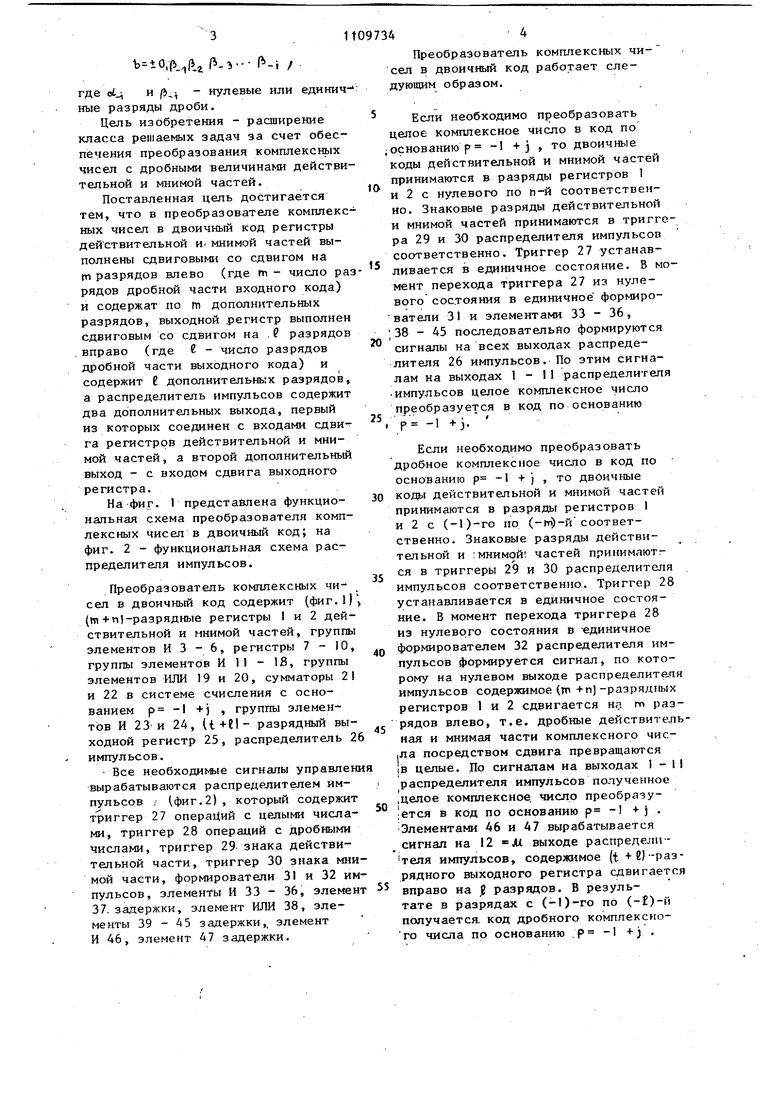

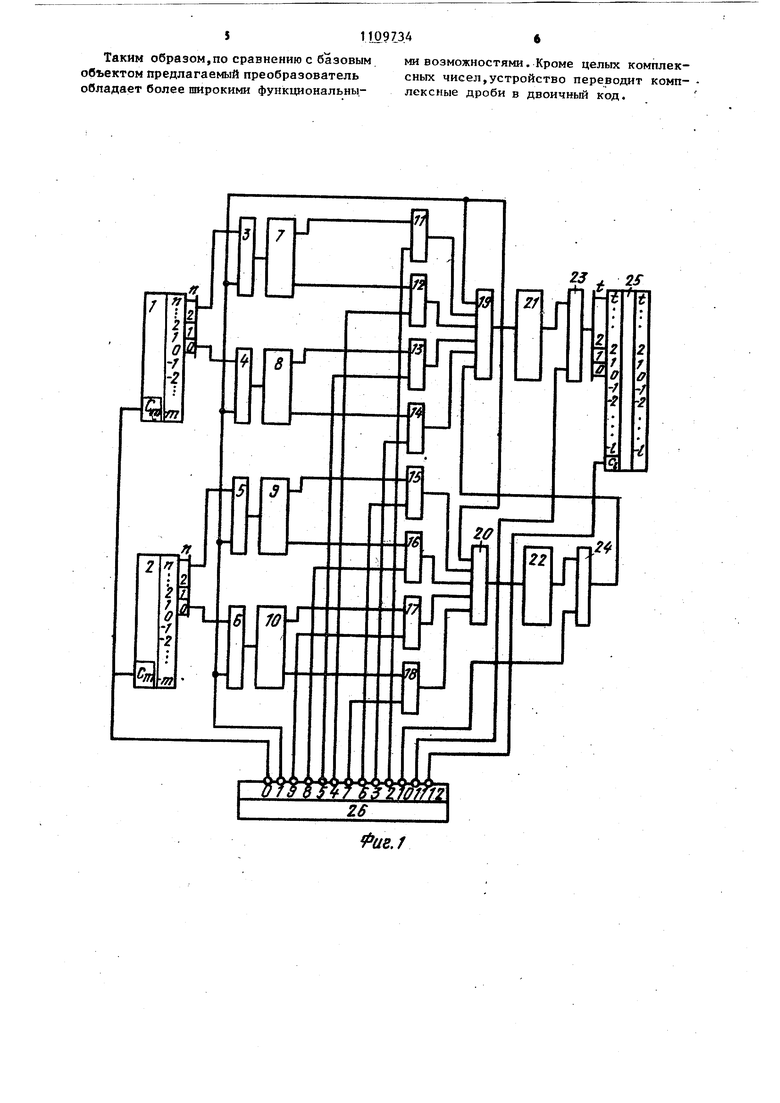

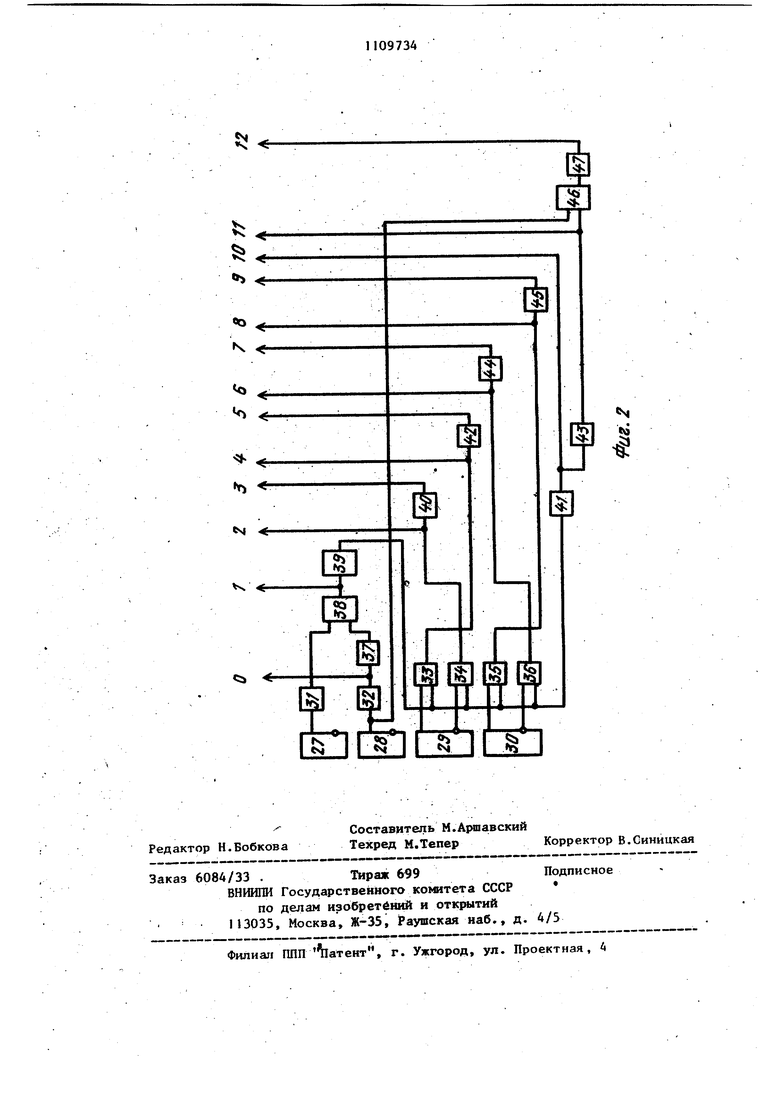

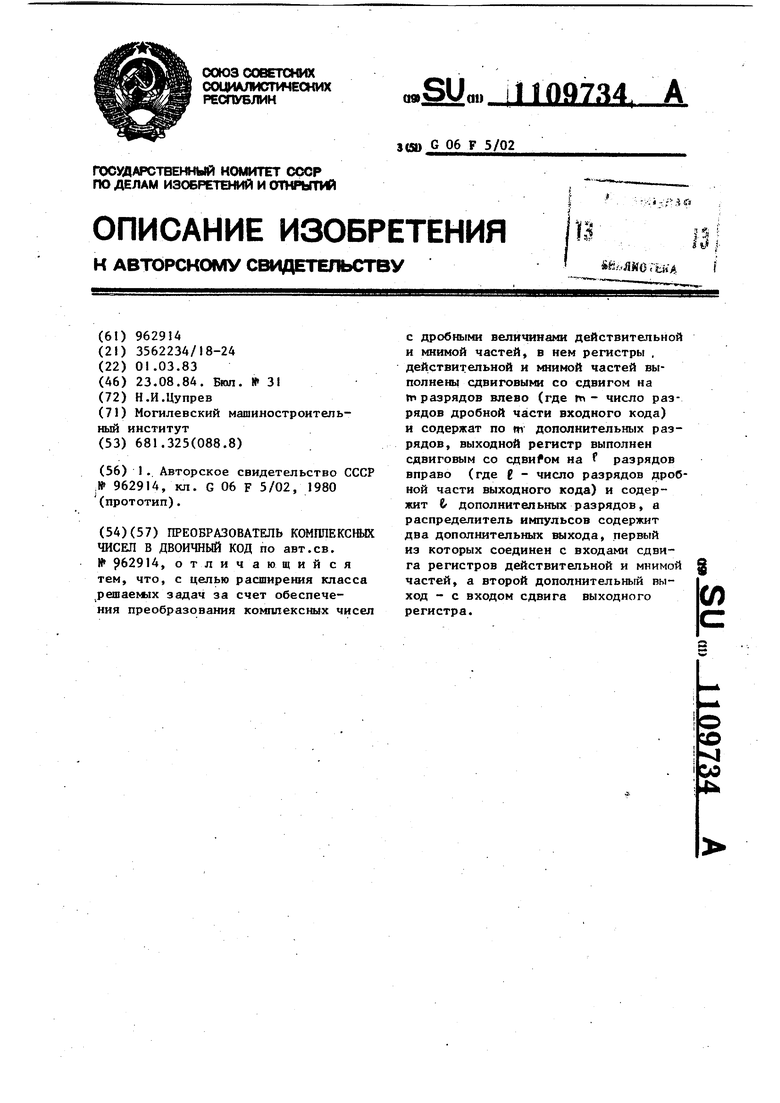

4 1 Изобретение относится к цифрово вычислительной технике и может быт использовано в вычислительных маши иах и системах для выполнения операций над комплексными числами. По основному авт.св. № 962914 известен преобразователь комплексных чисел в двоичный код, содержащий регистры мнимой и действительной частей, выходной регистр и рас пределитель импульсов, четыре регистра, четырнадцать групп элементов И, первую и вторую группы элементов ИЛИ, первый и второй сумматоры с основанием , причем прямые выходы i-x разрядов регистр действительной части ( i 41, 1 1 т J где П - число разрядов входного кода ) соединены с первыми входами 2 1-х элементов И первой группы, прямые вь1ходы (i+l)-x разрядов регистра действительной части подключены к первым входам 2(i+l)-x и 2(l+l)+J-x элементов И первой группы, прямые выходы (i+2)-x разрядов регистра действительной части соединены .с первыми входами (2i+4)-x элемент И второй группы, прякые выходы (i+3)-x разрядов регистра действительной части соединены с входами ()-х и ()-х элементов И второй группы, прямые выходы i-x разрядов регистра мнимой части сое динены с первыми входами 21-х и ()-х элементов И третьей группы, прямые выходы (i+3)-x разрядов регистра мнимой части соединены с первыми входами (2i+6)-x элементов третьей группы, прямые выходы (i+l) разрядов регистра мнимой части сое нены с входами (2i+2)-x элементов четвертой группы, .прямые выходы (+2)-х разрядов регистра мнимой части соединены с первыми входами ()-х и (2i+5)-x элементов И четвертой группы, первые входы ост ных элементов И первой, второй, третьей и четвертой групп соединен с входом логического нуля преобразователя, первый выход распределителя импульсов - с вторыми входами всех элементов И первой, второй, третьей .и четвертой групп, выходы котЬрых соединены с соответствующи входами первого, второго, третьего и четвертого регистров соответстве но, прямые и инверсные выходы разр 4 дов первого регистра соединены с первыми входами элементов И пятой и шестой групп соответственно, прямые и инверсные выходы разрядов второго регистра соединены с первыми входами элементов И седьмой и восьмой групп соответственно,прямые и инверсные выходы разрядов третьего регистра соедине й.1 с первыми входами элементов И девятой и десятой групп соответственно, прямые и инверсные выходы четпертого регистра соединены с первыми входами элементрв И один- ладдатой и двенадцатой групп соответственно, вторые входы элементов И пятой, шестой, седьмой, восьмой, девятой, десятой, одиннадцатой и двенадцатой групп соединены соответственно с вторым, .третьим, четвертым, пятым, шестым, седьмым, восьмым и девятым выходами распределителя импульсов, первый выход которого соединен с первыми входами g-x (1 зт, т 1 и ( элементов ИЛИ первой и второй групп, первые входы остальных элементов ИЛИ пербой .и второй групп соединены, с входом логического нуля преобразователя, вторые, третьи, четвертые и пятые входы элементов ИЛИ второй группы - соответственно с выходами элементов И девятой, десятой, один- надцатой и двенадцатой групп, isbfходы элементов ИЛИ первой и второй групп соединены со счетными входами первого и второго сумматоров с основанием () соответственно, выходы которых соединены соответственно с первыми входами элемен- .тов И тринадцатой и четырнадцатой групп, вторые входы которых соединены соответственно с десятым и одиннадцатым выходами распределителя импульсов, выходы элементов И тринадцатой группы соединены с входами выходного регистра, вторые, третьи, четвертые, пятые и шестые входы элементов ИЛИ первой группы соединены соответственно с выходами элементов И пятой, шестой, седьмой, восьвосьмой и четырнадцатой групп 1. Недостатком известного преобразователя является невозможность обработки комплексных чисел, действительная и мнимая части которых представляют соответственно дроби вида ,oL..,ot-2° -3--- b-iO,(5.(.V-- / где oi и /5, - нулевые или единич ныв разряды дроби. Цель изобретения - расширение класса решаемых задач за счет обеспечения преобразования комш1екснь1Х чисел с дробными величинами действи тельной и мнимой частей. Поставленная цель достигается тем, что в преобразователе комплекс ных чисел в двоичный код регистры действительной и мнимой частей выполнены сдвиговыми со сдвигом на m разрядов влево (где rti - число ра рядов дробной части входного кода) и содержат по m дополнительных разрядов, выходной регистр выполнен сдвиговым со сдвигом на , Р разрядов вправо (где К - число разрядов дробной части выходного кода) и содержит i допелнительнь:х разрядов, а распределитель импульсов содержит два дополнительных выхода, первый из которых соединен с входами сдвига регистров действительной и мнимой частей, а второй дополнительный выход - с входом сдвига выходного регистра. На-фиг. I представлена функциональная схема преобразователя комплексных чисел в двоичный код; на фиг. 2 - функциональная схема распределителя импульсов. Преобразователь комплексных чисел в двоичный код содержит (фиг.и (т+п}-разрядные регистры 1 и 2 действительной и мнимой частей, группы элементов И 3 - 6, регистры 7 - 10, группы элементов И 11 - IS, группы элементов ИЛИ 19 и 20, сумматоры 2 к 22 в системе счисления с основанием р -I +) , группы элементов И 23 и 24, (t+М - разрядный выходной регистр 25, распределитель 2 импульсов. - Все нeoбxoди ыe сигналы управлен вырабатываются распределителем импульсов ; (фиг,2, который содержит триггер 27 операций с целыми числами, триггер 28 операций с дробными числами, триггер 29 знака действительной части, триггер 30 знака мни мой части, формирователи 31 и 32 им пульсов, элементы И 33 - 36, элемен 37. за,цержки, элемент ИЛИ 38, элементы 39-45 задержки,, элемент И 46, элемент 47 задержки. 44 Преобразователь комплексных чисел в двоичный код работает следующим образом. Если необходимо преобразовать целое комплексное число в код по основаниюр -1 +J , то двоичные коды действительной и мнимой частей принимаются в разряды регистров 1 и 2 с нулевого по п-й соответственно. Знаковые разряды действительной и мнимой частей принимаются в триггера 29 и 30 распределителя импульсов соответственно. Триггер 27 устанавливается в единичное состояние. В момент перехода триггера 27 из нулевого состояния в единичное формирователи 31 и элементами 33 - 36, 38 - 45 последовательно формируются сигналы на всех выходах распределителя 26 импульсов. По этим сигналам на выходах 1-11 распределителя импульсов целое комплексное число преобразуется в код по основанию р -1 + J. Если необходимо преобразовать дробное комплексное число в код по основанию р -I + j , то двоичные коды действительной и мнимой частей принимаются в разряды регистров I и 2 с (-1)-го по (-hn)-и соответственно. Знаковые разряды действительной и : мнимой, частей принимаются в триггеры 29 и 30 распределителя импульсов соответственно. Триггер 28 устанавливается в единичное состояние. В момент перехода триггера 28 из нулевого состояния в -единичное формирователем 32 распределителя импульсов формируется сигнал, по которому на нулевом выходе распределителя импульсов содержимое (гп +п)-разрядных регистров 1 и 2 сдвигается на m разрядов влево, т.е. дробные действительная и мнимая части комплексного чис,ла посредством сдвига превращаются iB целые. По сигналам на выходах 1-11 распределителя импульсов полученное .целое комгшексное. число преобразуется в кол по основанию р -1 - ) . Элементами 46 и 47 вырабатывается сигнал на 12 JU выходе распределителя импульсов, содержимое (t +)-разрядного выходного регистра сдвигается вправо на разрядов. В результате в разрядах с (-1)-го по (-)-й получается, код дробного комплексного числа по основанию .р -1 .

Таким образом,по сравнению с базовым объектом предлагаемый преобразователь обладает более широкими функциональными возможностями. Кроме целых комплексных чисел,устройство переводит комплексные дроби в двоичный код.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| Устройство для вычисления квадратного корня | 1986 |

|

SU1359778A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1315999A1 |

| Устройство для возведения в квадрат комплексных чисел | 1980 |

|

SU879584A1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| Преобразователь комплексных сигналов | 1983 |

|

SU1104525A1 |

| ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2029362C1 |

| Устройство для деления чисел | 1990 |

|

SU1795456A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЧИСЛА В КВАДРАТИЧЕСКИЕ ОСТАТКИ | 1992 |

|

RU2029436C1 |

ПРЕОБРАЗОВАТЕЛЬ КОМПЛЕКСНЫХ ЧИСЕЛ В ДВОИЧНЫЙ КОД по авт.св. № 962914, отличающийся тем, что, с целью расширения класса решаемых задач за счет обеспечения преобразования комплексных чисел с дробными величинами действительной и мнимой частей, в нем регистры , действительной и мнимой частей выполнены сдвиговыми со сдвигом на т разрядов влево (где п - число разрядов дробной части входного кода) и содержат по m дополнительных разрядов, выходной регистр выполнен сдвиговым со сдвигом на С разрядов вправо (где - число разрядов дробной части выходного кода) и содержит & дополнительных разрядов, а распределитель импульсов содержит два дополнительных выхода, первый из которых соединен с входами сдвиg га регистров действительной и мнимой частей, а второй дополнительный вы(Л ход - с входом сдвига выходного регистра.

ие.1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-23—Публикация

1983-03-01—Подача