О

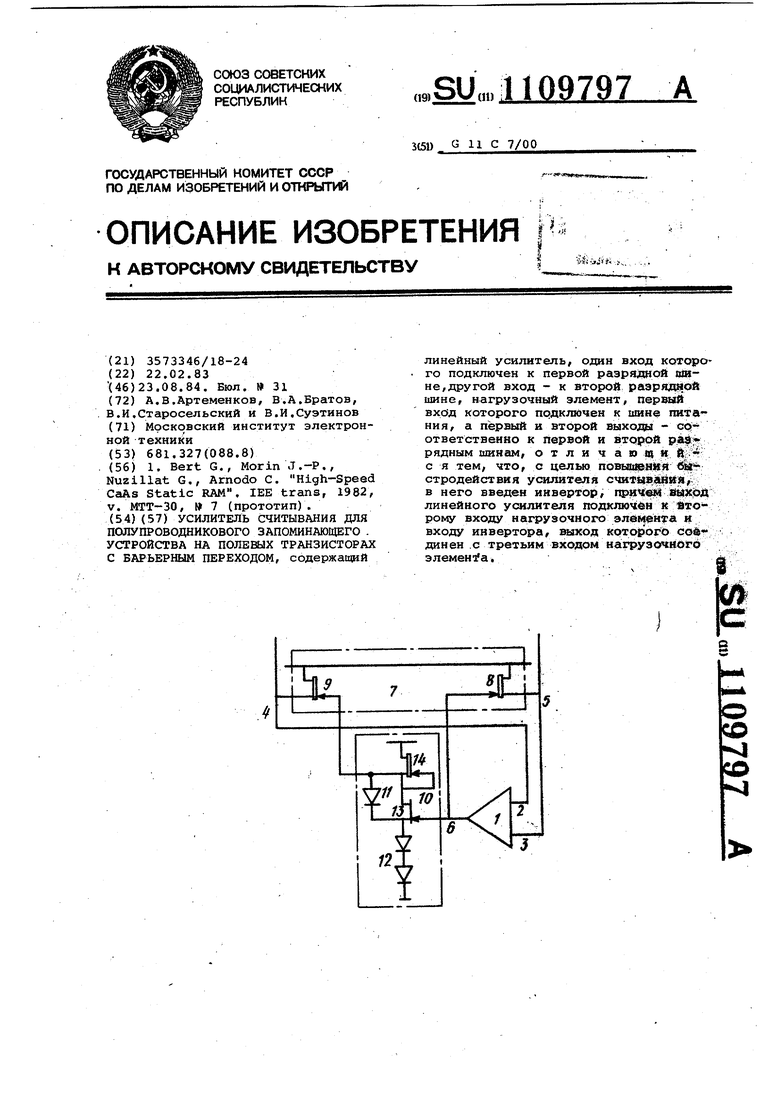

со - со ИэоОретение относится к микроэле ронике и может быть использовано в интегральных схемах запоминающих ус ройств . Наиболее близким к изобретению является усилитель считывания для п лупроводникового запоминающего устройства на полевых транзисторах с барьерным переходом, содержащий лин ный усилитель с неинвертирующим и и вертирующим входами, подключенными одной и другой- разрядным шинам, к которым подключен нагрузочный элемент tl J. Недостатком известного усилителя считывания является непрерывная работа нагрузочного элемента, ток кот рого препятствует изменению потенциалов разрядных шин и, следователь но, уменьшает скорость считывания. Цель изобретения - повышение быст родействия усилителя. Поставленная цель достигается тем что в усилитель считывания для полупроводникового запоминающего устройства на полевйх транзисторах с барье рным переходом, содержащий линейный усилитель, один вход которого подключен к первой разрядной шине, другой вход - к второй разрядной шине, нагрузочный элемент, пер.вый вход которого поякл&чен к шине питания, а первый U второй выхода - соответственно к первой и ззторой раэр:Я;а«кв4ти нам, введен инвертор, причем выход Ли нейного усилителя подключен к второму входу нагрузочного лемента и входу инвертора, выход которого соединен с третьим входом нагрузочного элемента. На чертеже приведена принципиальная электрическая схема усилителя считывания. Устройство содержит линейный усилитель 1 с неинвертирующим 2 и инвертирующим 3 входами, подключенными к первой 4 и второй 5 разрядным шинам соответственно, выход б линейного усилителя, а также нагрузочный элемент 7, выполненный в виде первого 8 и второго 9 нормально открытых транзисторов, стоки которых подключены к источнику положительного питания, истоки - к соответствующим разрядным шинам, а затворы - соответственно к выходу 6. линейного усилителя и выходу инвертора 10, который содержит ограничительный диод 11 с барьерным-переходом, диоды 12 смещения, нормально закрытый 13 и нормально открытый 14 транзисторы. Усилитель считывания работает следующим образом. Пусть в исходный момент времени на разрядной шине 4 сохраняется высокий потенциал (около ЗОд), а на разрядной шине 5 - низкий потенциал (2U). При этом на выходе б усилительной схемы поддерживается высокий потенциал, который фиксируется на урОвне ЗОр цепочкой из двух смещающих диодов 12 и переходом затвор-исток нормально закрытого транзистора 13 инвертора 10, В этом случав инвертор 10 открыт, на его выходе поддерживается низкий потенциал (2Ujj) , нагрузочный транзистор 8 включен, а нагрузочный транзистор 9 выключен. При понижении потенциала на разрядной шине 4 до величины 2U одновременно нарастает потенциал разрядной шины 5 до величины 3tJjj и падает потенциал на выходе 6 до величины 2Uj), При этрм зак{%1ва}отся нагрузочный транзистор 8 и инвертор 10, потенциал на щаходе которого возрастает и огранйчиааеФсА на уровне зи цепочкой из ограничительного диода 11 и смещающих диодов 12, В результате этого нагрузочный транзистор 9 открывается. Таким образом, понижение потенциала разрядной шины 4 происходит при выключенном нагрузочном транзисторе 9 , При понижении потенциала разрядной шины 5 (нагрузочный транзистор 8 выключен) усилитель возвращается в исходное состояние. Технико-экономический эффект изобретения по сравнению с известным устройством проявляется в увеличении быстродействия в 1,5 раза, . .

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания на полевых транзисторах с барьерным переходом | 1983 |

|

SU1201874A1 |

| Усилитель считывания | 1981 |

|

SU970461A1 |

| Элемент памяти (его варианты) | 1983 |

|

SU1164787A1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

| Усилитель считывания на полевых транзисторах | 1987 |

|

SU1464210A1 |

| Элемент памяти | 1986 |

|

SU1361626A1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Усилитель считывания на КМДП-транзисторах | 1986 |

|

SU1345258A1 |

| Усилитель считывания | 1978 |

|

SU834764A1 |

УСИЛИТЕЛЬ СЧИТЫВАНИЯ ДЛЯ ПОЛУПРОВОДНИКОВОГО ЗАПОМИНАЮЩЕГО . УСТРОЙСТВА НА ПОЛЕИЛХ ТРАНЗИСТОРАХ С БАРЬЕРНЫМ ПЕРЕХОДОМ, содержащий линейный усилитель, один вход которо го подключен к первой разрядной аШне,другой вход - к второй разрядной шине, нагрузочный элемент, первый вход которого подключен к шине питания, а первый и второй выходы - соответственно к первой и второй рад рядным шинам, отличающий с я тем, что, с целью повы&юнИя вагстродействия усилителя считывания,, в него введен инвертор, приче1и( 8ЫХОД линейного усилителя подключён к «торому входу нагрузочного элемента и входу инвертора, выход которого сой динен .с третьим входом нагрузочного элемента.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Bert G., Morin J.-P., Nuzillat G., Arnodo G | |||

| High-Speed CaAs Static RAM | |||

| lEE trans, 1982, V | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

Авторы

Даты

1984-08-23—Публикация

1983-02-22—Подача