Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах, выполненных из КМДП-транзисторов, для усиления сигнала считываемой информации.

Цель изобретения - повышение надежности усилителя.

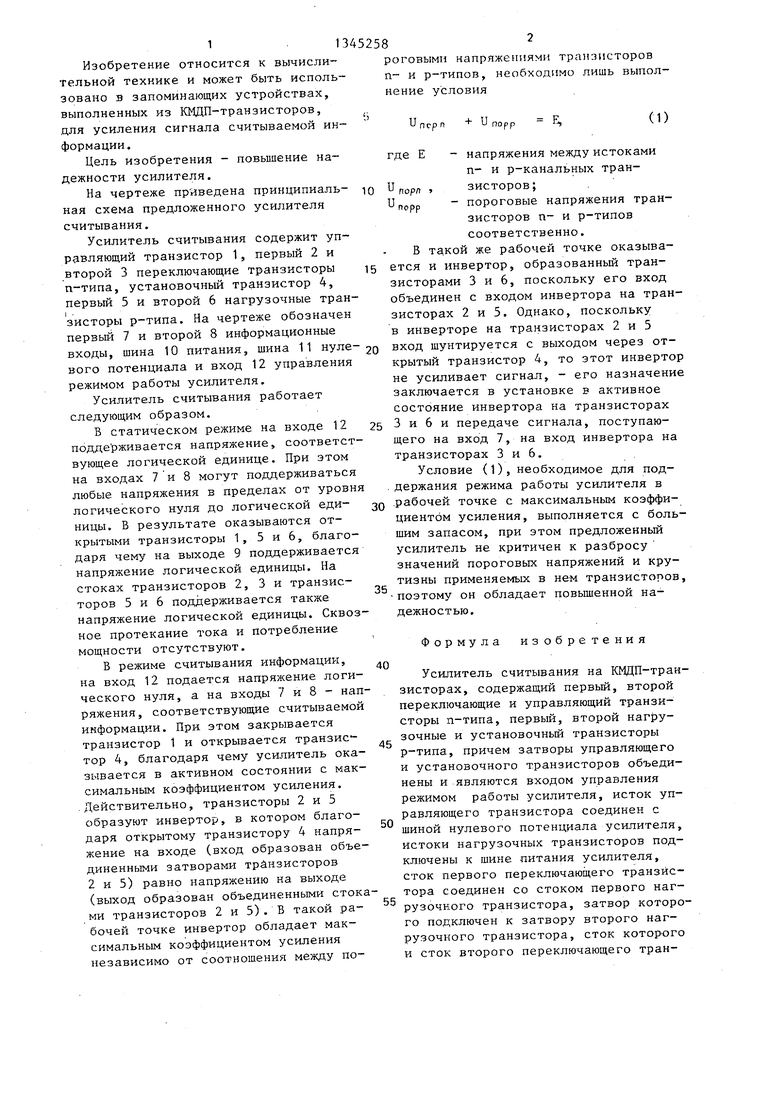

На чертеже пр иведена принципиальная схема предложенного усилителя считывания.

Усилитель считывания содержит управляющий транзистор 1, первый 2 и второй 3 переключающие транзисторы п-типа, установочный транзистор 4, первый 5 и второй 6 нагрузочные транзисторы р-типа. На чертеже обозначен первый 7 и второй 8 информационные

25

входы, шина 10 питания, шина 11 нуле- 2о вход шунтируется с выходом через открытый транзистор 4, то этот инвертор не усиливает сигнал, - его назначение заключается в установке в активное состояние инвертора на транзисторах 3 и 6 и передаче сигнала, поступающего на вход 7, на вход инвертора на транзисторах 3 и 6.

Условие (1), необходимое для поддержания режима работы усилителя в .рабочей, точке с максимальным коэффи- цнентом усиления, выполняется с большим запасом, при этом предложенный усилитель не критичен к разбросу значений пороговых напряжений и крутизны применяемых в нем транзисторов, поэтому он обладает повьшенной надежностью.

вого потенциала и вход 12 управления режимом работы усилителя.

Усилитель считывания работает следующим образом.

В статическом режиме на входе 12 поддерживается напряжение, соответствующее логической единице. При этом на входах 7 и 8 могут поддерживаться любые напряжения в пределах от уровня логического нуля до логической единицы. В результате оказываются открытыми транзисторы 1, 5 и 6, благодаря чему на выходе 9 поддерживается напряжение логической единицы. На стоках транзисторов 2, 3 и транзисторов 5 и 6 поддерживается также напряжение логической единицы. Сквозное протекание тока и потребление мощности отсутствуют.

в режиме считывания информации, на вход 12 подается напряжение логического нуля, а на входы 7 и В - напряжения, соответствующие считываемой информации. При этом закрывается транзистор 1 и открывается транзистор 4, благодаря чему усилитель оказывается в активном состоянии с мак- симальньш коэффициентом усиления. .Действительно, транзисторы 2 и 5 образуют инвертор, в котором благодаря открытому транзистору 4 напряжение на входе (вход образован объединенными затворами транзисторов 2 и 5) равно напряжению на выходе (выход образован объединенными стоками транзисторов 2 и 5). В такой рабочей точке инвертор обладает максимальным коэффициентом усиления независимо от соотношения между по30

35

40

45

50

55

Формула изобретения

Усилитель считывания на КМДП-тран- зисторах, содержащий первый, второй переключающие и управляющий транзисторы п-типа, первый, второй нагрузочные и установочный транзисторы р-типа, причем затворы управляющего и установочного транзисторов объединены и являются входом управления режимом работы усилителя, исток управляющего транзистора соединен с шиной нулевого потенциала усилителя, истоки нагрузочных транзисторов подключены к шине питания усилителя, сток первого переключающего транзистора соединен со стоком первого нагрузочного транзистора, затвор которого подключен к затвору второго нагрузочного транзистора, сток которого и сток второго переключающего транроговымт напряжениями транзисторов п- и р-типов, необходимо лишь выполнение условия

и Пер п где Е

+ и

ПОрр

F

(1)

порп

ПОрр

5

-напряжения между истоками п- и р-канальных транзисторов;

-пороговые напряжения транзисторов п- и р-типов соответственно.

В та.кой же рабочей точке оказывается и инвертор, образованный транзисторами 3 и 6, поскольку его вход объединен с входом инвертора на транзисторах 2 и 5. Однако, поскольку в инверторе на транзисторах 2 и 5

Формула изобретения

Усилитель считывания на КМДП-тран- зисторах, содержащий первый, второй переключающие и управляющий транзисторы п-типа, первый, второй нагрузочные и установочный транзисторы р-типа, причем затворы управляющего и установочного транзисторов объединены и являются входом управления режимом работы усилителя, исток управляющего транзистора соединен с шиной нулевого потенциала усилителя, истоки нагрузочных транзисторов подключены к шине питания усилителя, сток первого переключающего транзистора соединен со стоком первого нагрузочного транзистора, затвор которого подключен к затвору второго нагрузочного транзистора, сток которого и сток второго переключающего тран3 1345258

зистора объединены и является выхо-ком управляющего транзистора и истоком дом усилителя, отличающий-установочного транзистора, сток кото- с я тем, что, с целью повышениярого подключен к стоку первого перенадежности усилителя, затворы нагру- ключающего транзистора, истоки пере- зочных транзисторов соединены с затво-ключающих транзисторов являются ин- рами переключающих транзисторов, сто-формадионными входами усилителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания на КМДП - транзисторах | 1986 |

|

SU1348904A1 |

| Усилитель считывания на КМДП-транзисторах | 1986 |

|

SU1377910A1 |

| Усилитель считывания на КМДП-транзисторах для статических запоминающих устройств | 1987 |

|

SU1513513A1 |

| Усилитель считывания на КМДП транзисторах | 1984 |

|

SU1241285A1 |

| Усилитель считывания на кмдп-транзисторах | 1978 |

|

SU771716A1 |

| Входной усилитель-формирователь с запоминанием информации | 1980 |

|

SU903970A1 |

| Усилитель считывания на КМДП транзисторах | 1986 |

|

SU1376117A1 |

| Усилитель считывания на МДП-транзисторах | 1989 |

|

SU1679547A1 |

| Усилитель считывания на КМДП-транзисторах | 1983 |

|

SU1088065A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

Изобретение относится к вычислительной технике и может быть применено в запоминающих устройствах, выполненных из КМДП-транзисторов, ДЛИ усиления сигналов считываемой информации. Целью изобретения является повышение надежности усилителя. Усилитель считывания содержит управляющий транзистор 1, переключающие транзисторы 2 и 3 п-типа, установочный транзистор 4 и нагрузочные тран- . зисторы 5, 6 р-типа, шину 10 питания и шину 11 нулевого потенциала. В режиме считывания на вход 12 управления режимом работы усилителя подается напряжение логического нуля, а на входы 7 и 8 - напряжения, соответствующие считываемой информации. При этом закрывается транзистор 1 и открывается транзистор 4, в результате чего, усилитель работает с максимальным коэффициентой усиления. Надежность повьшаётся также за счет того, что усилитель некритичен к разбросу значений пороговых напряжений и крутизны применяемых в нем транзисторов. 1 ил. 10 4 flirt д 1г -о 00 СП to 01 00 1 i

| IEEE Journal of Solid-State Circuits | |||

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| IEEE Journal of Solid-State Circuits, 1984, vol. | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Ветряный двигатель | 1922 |

|

SU554A1 |

Авторы

Даты

1987-10-15—Публикация

1986-06-13—Подача