13

75

Z1

75

22

17 и

19

16

(Л

20

1

15

21

tc

18

12 TJ

10 11

22

00

1Б

|

4

6 1 3

Изобретение относится к микроэлектронике и может быть использовано в интегральных схемах запоминающих устройств.

Цель изобретения - повышение быстродействия усилителя.

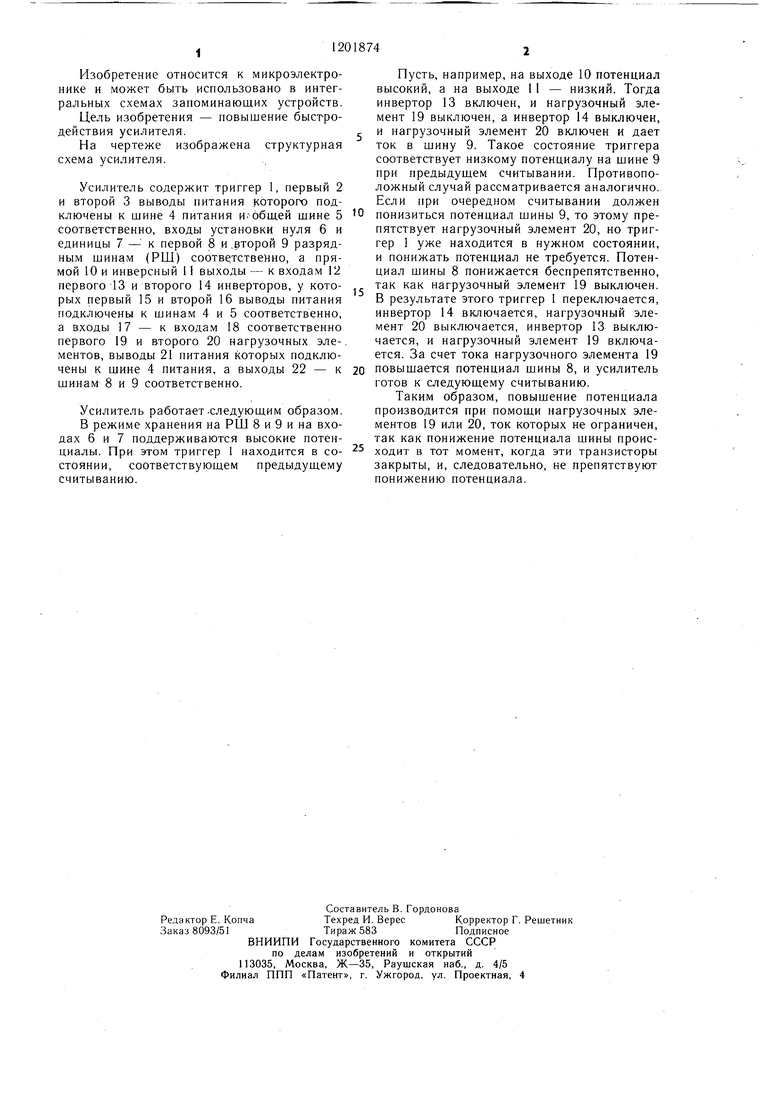

На чертеже изображена структурная схема усилителя.

Усилитель содержит триггер 1, первый 2 и второй 3 выводы питания которого подключены к шине 4 питания и.ббшей шине 5 соответственно, входы установки нуля 6 и единицы 7 - к первой 8 и второй 9 разрядным шинам (РШ) соответственно, а прямой 10 и инверсный 1 выходы - к входам 12 первого 13 и второго 14 инверторов, у которых первый 15 и второй 16 выводы питания подключены к шинам 4 и 5 соответственно, а входы 17 - к входам 18 соответственно первого 19 и второго 20 нагрузочных эле-, ментов, выводы 21 питания которых подключены к шине 4 питания, а выходы 22 - к шинам 8 и 9 соответственно.

Усилитель работает .следующим образом.

В режиме хранения на РШ 8 и 9 и на входах 6 и 7 поддерживаются высокие потенциалы. При этом триггер 1 находится в состоянии, соответствующем предыдущему считыванию.

Пусть, например, на выходе 10 потенциал высокий, а на выходе 11 - низкий. Тогда инвертор 13 включен, и нагрузочный элемент 19 выключен, а инвертор 14 выключек,

и нагрузочный элемент 20 включен и дает ток в шипу 9. Такое состояние триггера соответствует низкому потенциалу на шине 9 при предыдущем считывании. Противоположный случай рассматривается аналогично. Если при очередном считывании должен

понизиться потенциал щины 9, то этому препятствует нагрузочный элемент 20, но триггер 1 уже находится в нужном состоянии, и понижать потенциал не требуется. Потенциал шины 8 понижается беспрепятственно, так как нагрузочный элемент 19 выключен. В результате этого триггер 1 переключается, инвертор 14 включается, нагрузочный элемент 20 выключается, инвертор 13 выключается, и нагрузочный элемент 19 включается. За счет тока нагрузочного элемента 19

0 повышается потенциал щины 8, и усилитель готов к следующему считыванию.

Таким образом, повышение потенциала производится при помощи нагрузочных элементов 19 или 20, ток которых не ограничен, так как понижение потенциала шины происходит в тот момент, когда эти транзисторы закрыты, и, следовательно, не препятствуют понижению потенциала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Усилитель считывания для полупроводникового запоминающего устройства на полевых транзисторах с барьерным переходом | 1983 |

|

SU1109797A1 |

| Элемент памяти (его варианты) | 1983 |

|

SU1164787A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Оперативное запоминающее устройство | 1990 |

|

SU1809466A1 |

| Усилитель считывания на КМОП-транзисторах | 1983 |

|

SU1149310A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

УСИЛИТЕЛЬ СЧИТЫВАНИЯ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ С БАРЬЕРНЫМ ПЕРЕХОДОМ, содержащий триггер, первый и второй выводы питания которого подключены к шине питания и общей шине соответственно, отличающийся тем, что, с целью повышения быстродействия усилителя, в него введены первый и второй инверторы, первый и второй выводы питания которых подключены к шине питания и обшей шине соответственно, а входы - к прямому и инверсному выходам триггера соответственно, а также первый и второй нагрузочные элементы, выводы питания которых .подключены к шине питания, входы - к выходам соответствующих инверторов, а выходы - соответственно к первой и второй разрядны.м шинам, которые подключены соответственно к входам установки нуля и единицы триггера.

| IEEE trans, v | |||

| МТТ, ED-26, № 6 | |||

| IEEE trans, v | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

Авторы

Даты

1985-12-30—Публикация

1983-02-22—Подача