1

Изобретение относится к радиотехнике, а именно к устройствам цифрового фазового детектирования на неравных частотах, и может быть использо

вано для детектирования сигналов с угловой модуляцией, для получения сигналов рассогласования в системах АПЧ для формирования сетки стабильных частот в приемопередающей и изме- рительной аппаратуре.

Целью изобретения является повышение динамической точности, цифрового фазового детектирования.

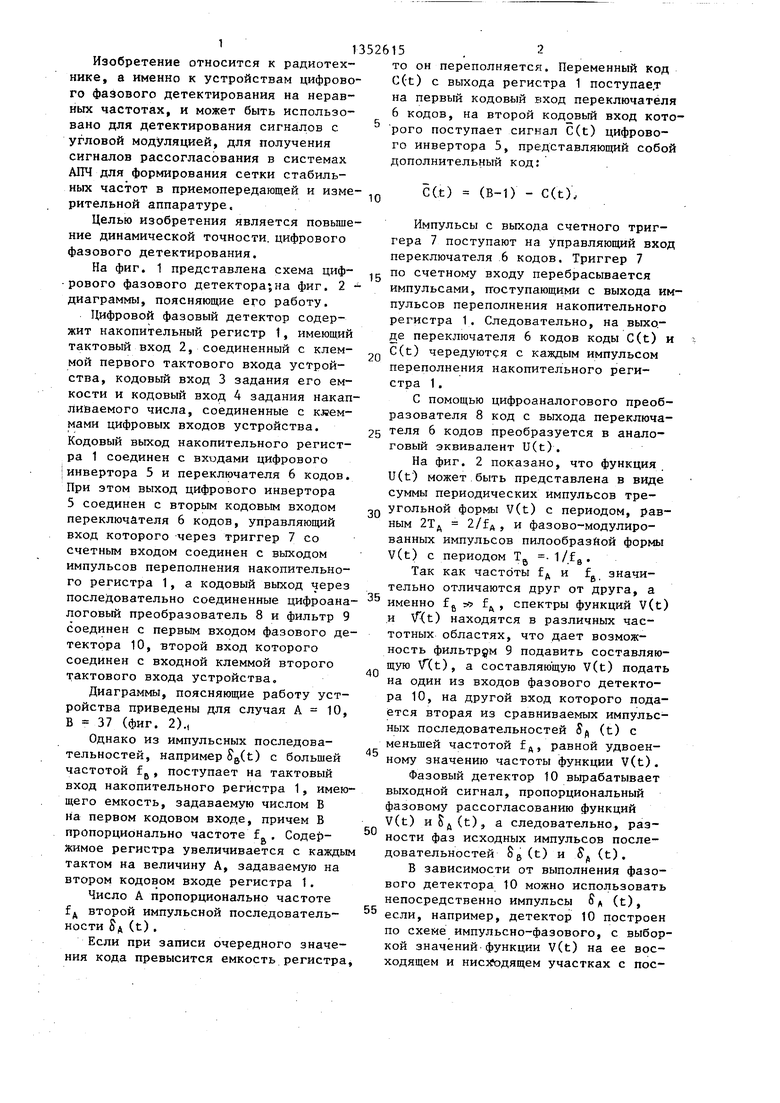

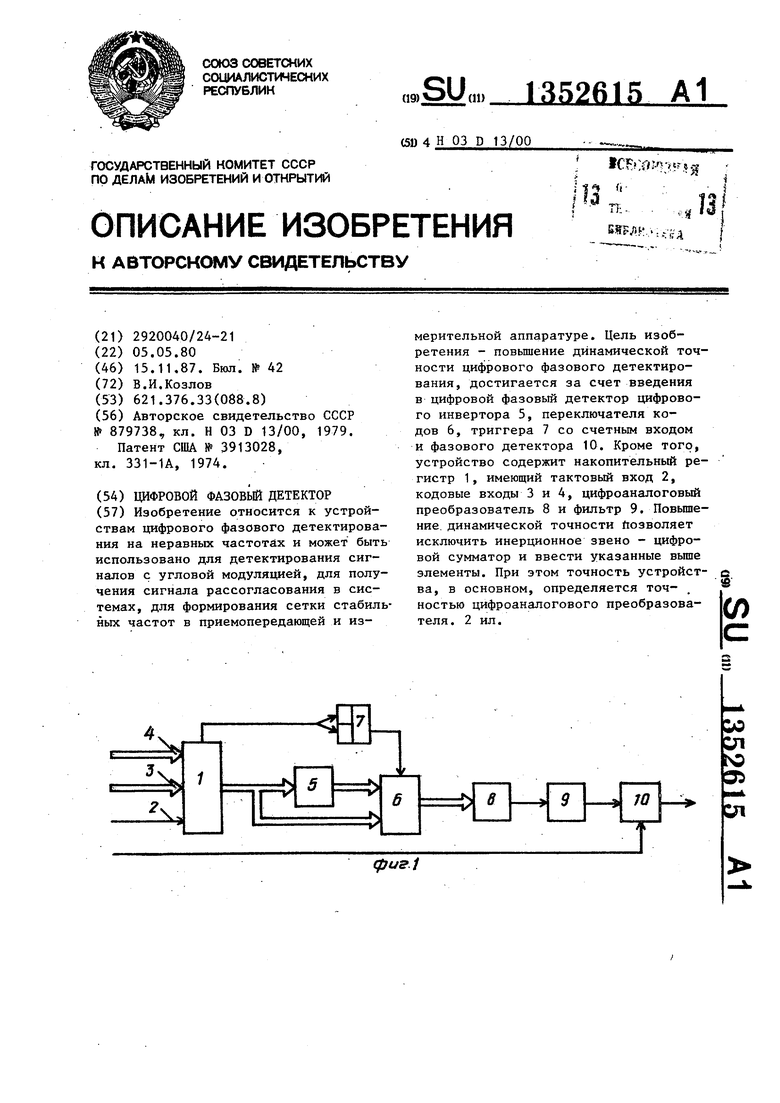

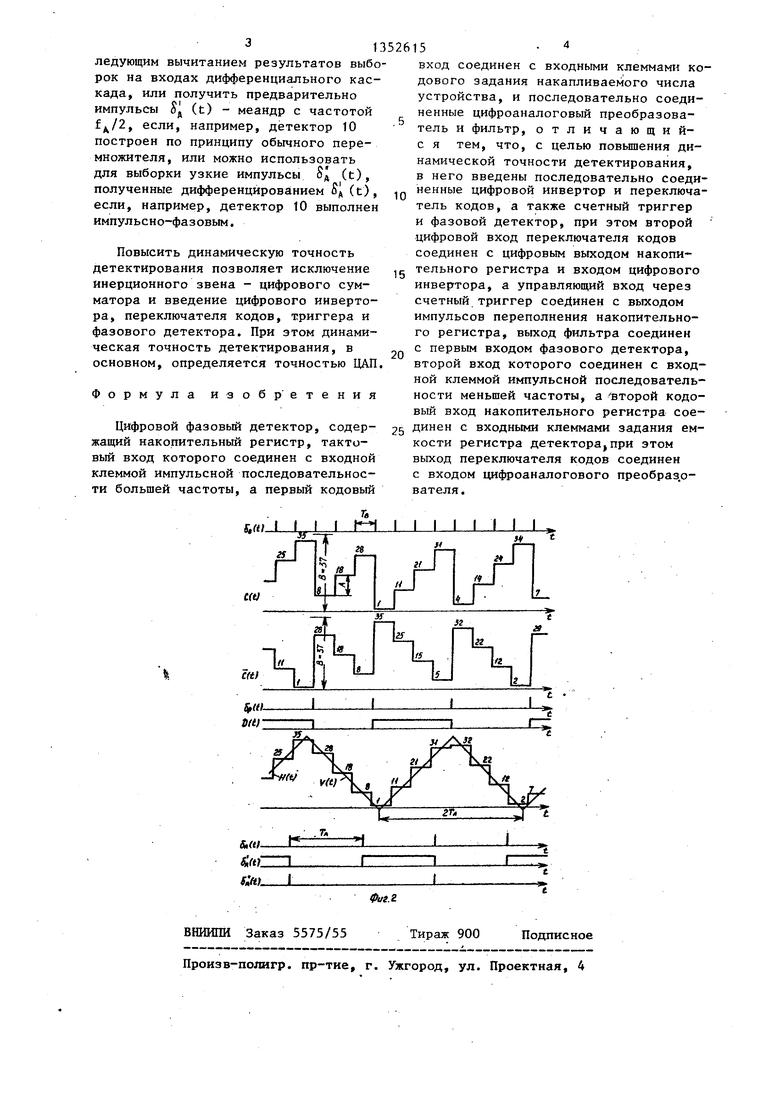

На фиг. 1 представлена схема циф-

рового фазового детектора на фиг. 2 диаграммы, поясняющие его работу.

Цифровой фазовый детектор содержит накопительный регистр 1, имеющий тактовый вход 2, соединенный с клеммой первого тактового входа устройства, кодовый вход 3 задания его емкости и кодовый вход 4 задания накапливаемого числа, соединенные с ккеммами цифровых входов устройства.

Кодовый выход накопительного регистра 1 соединен с входами цифрового I инвертора 5 и переключателя 6 кодов. При этом выход цифрового инвертора 5 соединен с вторым кодовым входом переключателя 6 кодов, управляющий вход которого через триггер 7 со счетным входом соединен с выходом импульсов переполнения накопительного регистра 1, а кодовый выход через последовательно соединенные цифроана логовый преобразователь 8 и фильтр 9 соединен с первым входом фазового детектора 10, второй вход которого соединен с входной клеммой второго тактового входа устройства.

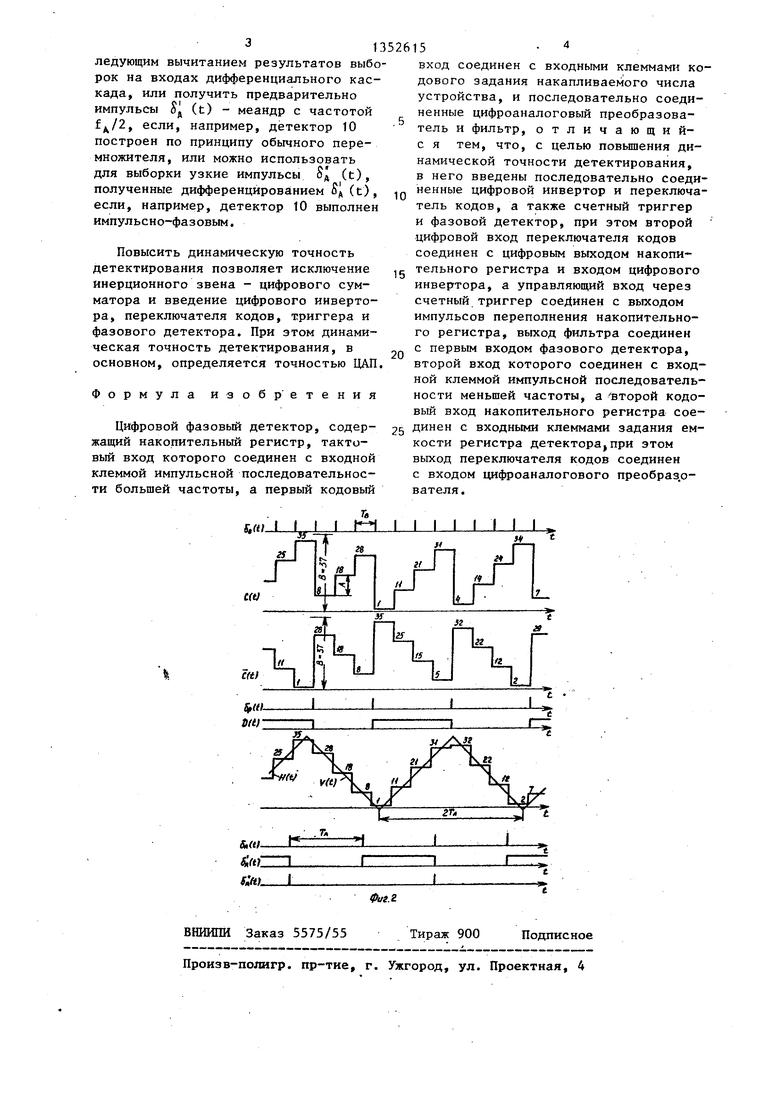

Диаграммы, поясняющие работу устройства приведены для случая А 10, В 37 (фиг. 2).,

Однако из импульсных последовательностей, например ) с большей частотой fц, поступает на тактовый вход накопительного регистра 1, имеющего емкость, задаваемую числом В на первом кодовом входе, причем В пропорционально частоте f . Содержимое регистра увеличивается с кажды тактом на величину А, задаваемую на втором кодовом входе регистра 1.

Число А пропорционально частоте д второй импульсной последователь- ности §д (t) .

Если при записи очередного значения кода превысится емкость регистра

.

5

0

„

15 . то он переполняется. Переменный код (X t) с выхода регистра 1 поступае.т на первый кодовый вход переключателя 6 кодов, на второй кодовый вход которого поступает сигнал C(t) цифрового инвертора 5, представляющий собой дополнительный код:

C(.t) (В-1) - C(t).

Импульсы с выхода счетного триггера 7 поступают на управляющий вход переключателя 6 кодов. Триггер 7 по счетному входу перебрасывается импульсами, поступающими с выхода импульсов переполнения накопительного регистра 1. Следовательно, на выходе переключателя 6 кодов коды C(t) и C(t) чередуются с каждым импульсом переполнения накопительного регистра 1.

С помощью цифроаналогового преобразователя 8 код с выхода переключателя 6 кодов преобразуется в аналоговый эквивалент U(t).

На фиг. 2 показано, что функция U(t) может быть представлена в виде суммы периодических импульсов треугольной формы V(t) с периодом, равным 2Тд , и фазово-модулиро- ванных импульсов пилообразйой формы V(t) с периодом Тц l/fg.

Так как частоты f и f значительно отличаются друг от друга, а именно f g f , спектры функций V(t) и r(t) находятся в различных частотных областях, что дает возможность фильтрам 9 подавить составляющую V(t), а составляющую V(t) подать на один из входов фазового детектора 10, на другой вход которого подается вторая из сравниваемых импульсных последовательностей S (t) с меньшей частотой д, равной удвоенному значению частоты функции V(t).

Фазовый детектор 10 вьфабатывает выходной сигнал, пропорциональный фазовому рассогласованию функций V(t) иSд(t), а следовательно, разности фаз исходных импульсов последовательностей SB (t) и S/ (t).

В зависимости от выполнения фазового детектора 10 можно использовать непосредственно импульсы SA (t), если, например, детектор 10 построен по схеме импульсно-фазового, с выборкой значений функции V(t) на ее восходящем и нисзйэдящем участках с пос 13526

ледующим вычитанием результатов выборок на входах дифференциального каскада, или получить предварительно импульсы д (t) - меандр с частотой д/2, если, например, детектор 10 - построен по принципу обычного перемножителя, или можно использовать для выборки узкие импульсы 5д (t), полученные дифференцированием 5, (t), если, например, детектор 10 выполнен импульсно-фазовым.

10

Повысить динамическую точность детектирования позволяет исключение инерционного звена - цифрового сумматора и введение цифрового инвертора, переключателя кодов, триггера и фазового детектора. При этом динамическая точность детектирования, в основном, определяется точностью ЦАП

Формула изобретения

Цифровой фазовый детектор, содержащий накопительный регистр, тактовый вход которого соединен с входной клеммой импульсной последовательности большей частоты, а первый кодовый

0

5

0

5

15-4

вход соединен с входными клеммами кодового задания накапливаемого числа устройства, и последовательно соединенные цифроаналоговый преобразователь и фильтр, отличающий- с я тем, что, с целью повышения динамической точности детектирования, Б него введены последовательно соединенные цифровой инвертор и переключатель кодов, а также счетный триггер и фазовой детектор, при этом второй цифровой вход переключателя кодов соединен с цифровым выходом накопительного регистра и входом цифрового инвертора, а управляющий вход через счетный триггер соединен с выходом импульсов переполнения накопительного регистра, выход фильтра соединен с первым входом фазового детектора, второй вход которого соединен с входной клеммой импульсной последовательности меньшей частоты, а второй кодовый вход накопительного регистра соединен с входными клеммами задания емкости регистра детектора,при этом выход переключателя кодов соединен с входом цифроаналогового преобраз.о- вателя.

K,(t) I I I I I I I I I t I I

w «

t(t)

I I

w «

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазовый детектор | 1980 |

|

SU898588A1 |

| Цифровой фазовый детектор | 1980 |

|

SU892654A1 |

| Цифровой фазовый детектор | 1980 |

|

SU875303A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1064421A1 |

| Способ цифрового фазового детектирования импульсных последовательностей на неравных частотах и устройство для его осуществления | 1979 |

|

SU879738A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1981 |

|

SU1109872A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1068838A1 |

| Цифровой фазовый детектор | 1980 |

|

SU894854A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1990 |

|

SU1755360A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1149394A1 |

Изобретение относится к устройствам цифрового фазового детектирования на неравных частотах и может быть использовано для детектирования сигналов с угловой модуляцией, для получения сигнала рассогласования в системах, для формирования сетки стабильных частот в приемопередающей и измерительной аппаратуре. Цель изобретения - повьшение динамической точности цифрового фазового детектирования, достигается за счет введения в цифровой фазовый детектор цифрового инвертора 5, переключателя кодов 6, триггера 7 со счетным входом и фазового детектора 10. Кроме того, устройство содержит накопительный регистр 1, имеющий тактовый вход 2, кодовые входы 3 и 4, цифроанапоговый преобразователь 8 и фильтр 9. Повьшение. динамической точности позволяет исключить инерционное звено - цифровой сумматор и ввести указанные вьше элементы. При этом точность устройства, в основном, определяется точностью цифроанапогового преобразователя. 2 ил. :л9 :л ю 35 Л фиг.1

| Способ цифрового фазового детектирования импульсных последовательностей на неравных частотах и устройство для его осуществления | 1979 |

|

SU879738A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 3913028, кл | |||

| Накладной висячий замок | 1922 |

|

SU331A1 |

Авторы

Даты

1987-11-15—Публикация

1980-05-05—Подача