Устройство относится к вычислительной технике и может быть использовано в блоках дискретной обработки информации.

Цель изобретения - повышение скорости контроля.

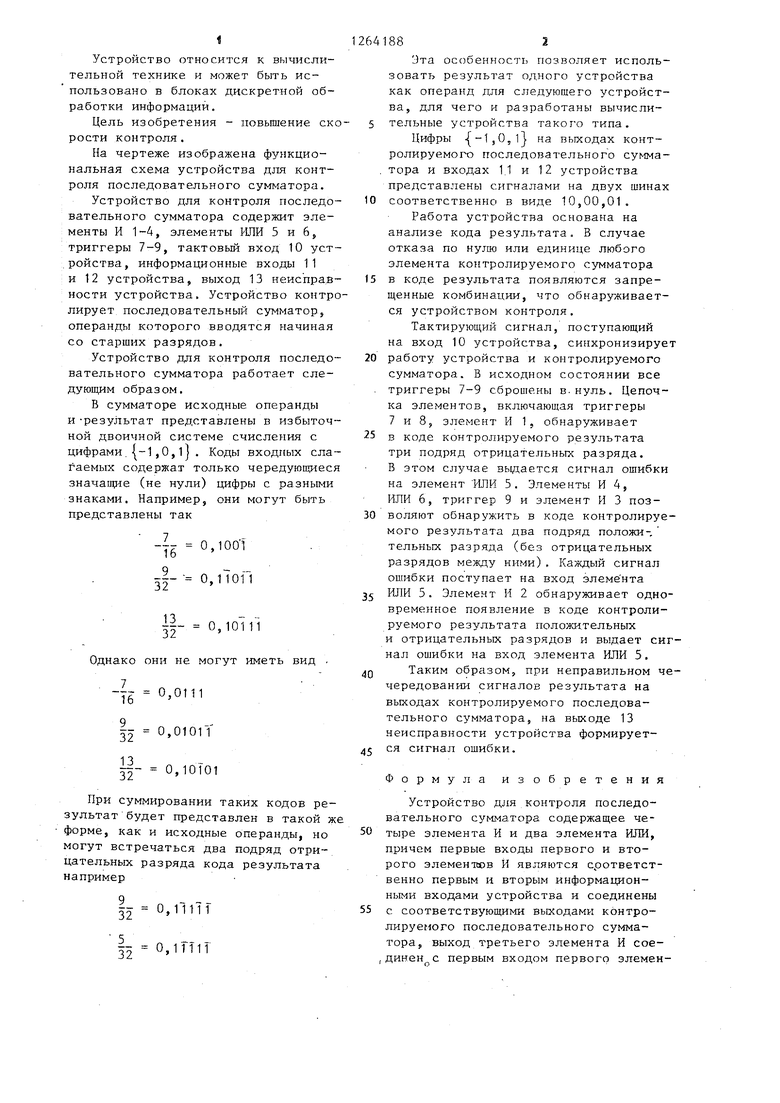

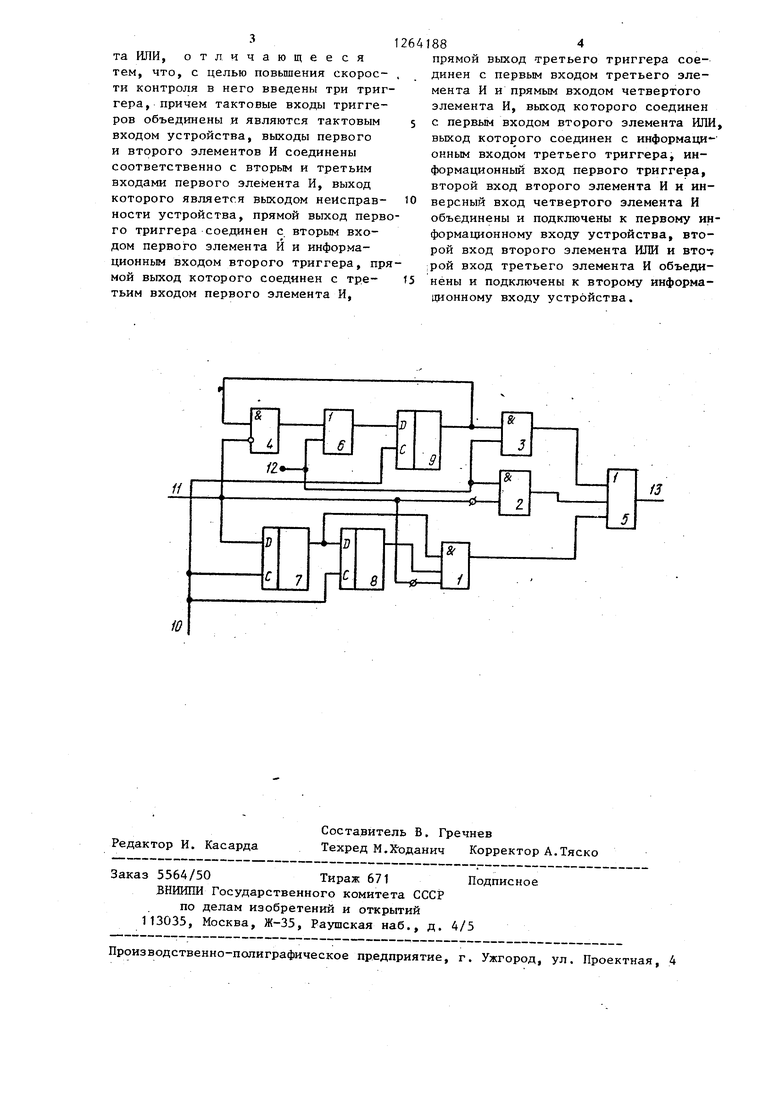

На чертеже изображена функциональная схема устройства д:1я контроля последовательного сумматора.

Устройство для контроля последовательного сумматора содержит элементы И 1-4, элементы ИЛИ 5 и 6, триггеры 7-9, тактовый вход 10 уст.ройства, информационные входы 11 и 12 устройства, выход 13 неисправности устройства. Устройство контролирует последовательный сумматор, операнды которого вводятся начиная со старших разрядов.

Устройство для контроля последовательного сумматора работает следующим образом.

В сумматоре исходные операнды и -результат представлены в избыточной двоичной системе счисления с цифрами.{-1,0,l. Коды входных слагаемых содержат только чередуюгдиеся значаище (не нули) цифры с разными знаками. Например, они могут быть представлены так

--g 0,1001

-|- о,поГ1

||- о, ioi ii

Однако они не могут иметь вид

-Тб

22 0,0101Т

- 0,10Т01

При суммировании таких кодов результат будет представлен в такой ж форме, как и исходные операнды, но могут встречаться два подряд отрицательных разряда кода результата например

l 0,lllTf 2 0,1TT1T

641882

Эта особенность позволяет использовать результат одного устройства как операнд для следующего устройства, для чего и разработаны вычисли5 тельные устройства такого типа.

Цифры - -tjOjIj на выходах контролируемого последовательного сумма. тора и входах 1.1 и 12 устройства

представлены сигналами на двух шинах 10 соответственно в виде 10,00,01.

Работа устройства основана на анализе кода результата. В случае отказа по нулю или единице любого элемента контролируемого сумматора 5 в коде результата появляются запрещенные комбинации, что обнаруживается устройством контроля.

Тактирующий сигнал, поступающий на вход 10 устройства, синхронизирует 20 работу устройства и контролируемого сумматора. В исходном состоянии все . триггеры 7-9 сброшены в.нуль. Цепочка элементов, включающая триггеры

7и 8, элемент И 1, обнаруживает 25 в коде контролируемого результата

три подряд отрицательных разряда.

8этом случае выдается сигнал ошибки на элемент ИЛИ 5. Элементы И 4,

ИЛИ 6, триггер 9 и элемент И 3 поз30 воляют обнаружить в коде контролируемого результата два подряд положительных разряда (без отрицательных разрядов между ними) . Каждый сигнал ошибки поступает на вход элемента 35 ИЛИ 5. Элемент И 2 обнаруживает одновременное появление в коде контролируемого результата положи.тельных и отрицательных разрядов и выдает сигнал ошибки на вход элемента ИЛИ 5. 4Q Таким образом, при неправильном чечередовании сигналов результата на выходах контролируемого последовательного сумматора, на выходе 13 неисправности устройства формируется сигнал ошибки.

Формула изобретения

Устройство для контроля последовательного сумматора содержащее четыре элемента И и два элемента ИЛИ, причем первые входы первого и второго элементаэв И являются срответственно первым и вторым информационными входами устройства и соединены

с соответствующими выходами контролируемого последовательного сумматора, выход третьего элемента И соединен с первым входом первого элемен3та ИЛИ, отличающееся тем, что, с целью повышения скороети контроля в него введены три триг гера, причем тактовые входы триггеров объединены и являются тактовым входом устройства, выходы первого и второго элементов И соединены соответственно с вторым и третьим входами первого элемента И, выход которого является выходом неисправности устройства, прямой выход перв го триггера соединен с. вторым входом первого элемента И и информационным входом второго триггера, пр мой выход которого соединен с третьим входом первого элемента И, 884 прямой выход третьего триггера соединен с первым входом третьего элемента И и прямым входом четвертого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с информадионным входом третьего триггера, информационный вход первого триггера, второй вход второго элемента И и инверсный вход четвертого элемента И объединены и подключены к первому информационному входу устройства, второй вход второго элемента ИЛИ и вто- :рой вход третьего элемента И объединёны и подключены к второму информа1ЩОННОМУ входу устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство для выполнения операций над несколькими числами | 1986 |

|

SU1348822A2 |

| Устройство для контроля сумматора | 1983 |

|

SU1111167A1 |

| Устройство для контроля делителя по модулю | 1988 |

|

SU1566352A1 |

| Устройство для деления | 1988 |

|

SU1513444A1 |

| Устройство для умножения | 1986 |

|

SU1427361A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1259270A1 |

| Устройство для определения числа единиц в двоичном коде с контролем | 1990 |

|

SU1795460A1 |

| Устройство для контроля регистров сдвига | 1987 |

|

SU1449997A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

Устройство относится к илчислительной технике и может быть ис пользовано в блоках дискретной об- работки информации. Целью изобретения является повьвение скорости контроля. Устрсйство содержит четыре элемента И, два элемента ИЛИ, три триггера, тактовый вход, два информационных входа и выход неисправности. При неправильнее чередовании сигналов результата на выходах контролируемого сумматора на выходе неисщ авности устройства формируется § сигнал ошибки. 1 ил.; (Л

| Накапливающий сумматор с фиксацией ошибок | 1976 |

|

SU603990A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля последовательного сумматора-вычитателя | 1981 |

|

SU968818A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-15—Публикация

1985-02-21—Подача