11

Изобретение относится к вычислительной технике и предназначено для применения в цифровых интегрирующих машинах.

Целью изобретения является повышение достоверности функционирования устройства.

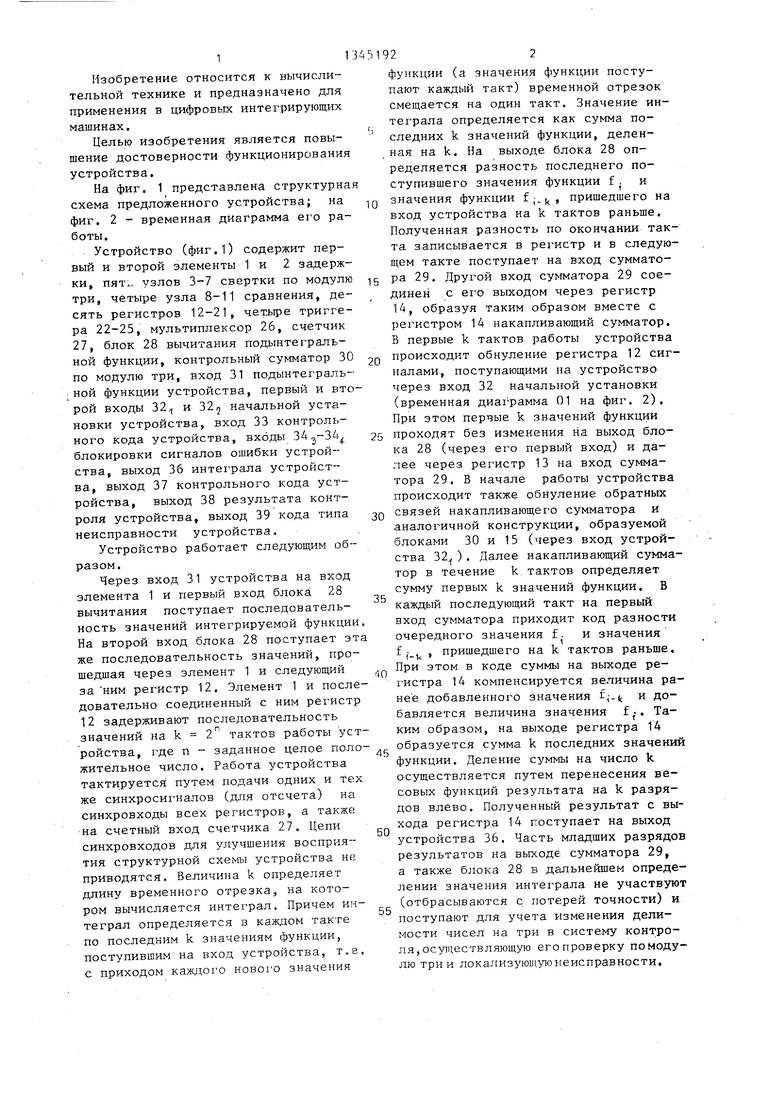

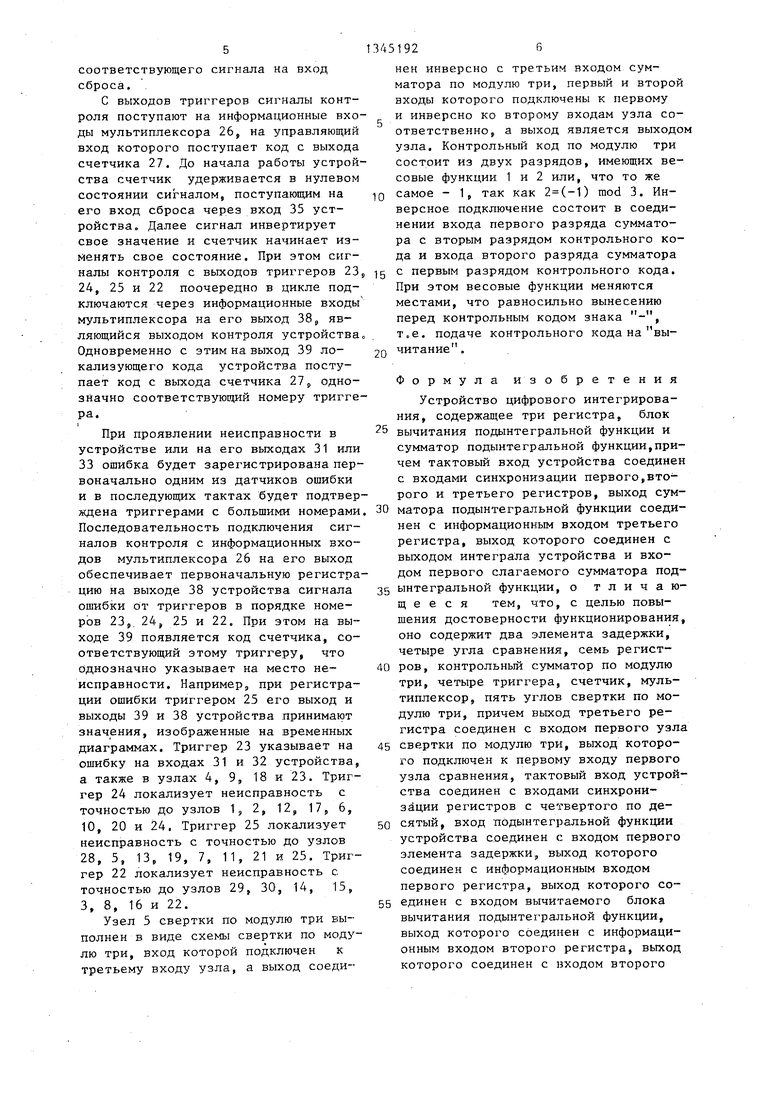

На фиг. 1 представлена структурна схема предложенного устройства; на фиг. 2 - временная диаграмма его работы.

Устройство (фиг.1) содержит первый и второй элементы 1 и 2 задержки, пят узлов 3-7 свертки по модулю три, четыре узла 8-11 сравнения, десять регистров 12-21, чет.ьфе триггера 22-25, мультиплексор 26, счетчик 27, блок 28 вычитания подынтегральной функции, контрольный сумматор 30 по модулю три, вход 31 подынтегральной функции устройства, первый и второй входы 32 и 322 начальной установки устройства, вход 33 контрольного кода устройства, входы блокировки сигналов ошибки устройства, выход 36 интеграла устройства, выход 37 контрольного кода устройства, выход 38 результата контроля устройства, выход 39 кода типа неисправности устройства.

Устройство работает следующим образом.

Через вход 31 устройства на вход элемента 1 и первый вход блока. 28 вычитания поступает последовательность значений интегрируемой функции На второй вход блока 28 поступает эт же последовательность значений, прошедшая через элемент 1 и следующий за ним регистр 12. Элемент 1 и последовательно соединенный с ним регистр 12 задерживают последовательность значений на k - 2 тактов работы устройства, где п - заданное целое положительное число. Работа устройства тактируется путем подачи одних и тех же синхросигналов (для отсчета) на синхровходы всех регистров, а также на счетный вход счетчика 27, Цепи синхровходов для улучшения восприятия структурной схемы устройства не приводятся. Величина k определяет длину временного отрезка, на котором вычисляется интеграл. Причем интеграл определяется в каждом такте по последним k значениям функции, поступившим на вход устройства, т.е. с приходом каждого нового значения

0

5

0

5

31

0

5

0

5

0

55

922

функции (а значения функции поступают каждый такт) временной отрезок смещается на один такт. Значение интеграла определяется как сумма последних k значений функции, делен,ная на k. На выходе блока 28 определяется разность последнего поступившего значения функции f . и значения функции f-,t пришедшего на вход устройства на k тактов раньше. Полученная разность по окончании такта записывается в регистр и в следую- П1;ем такте поступает на вход сумматора 29. Другой вход сумматора 29 соединен с его выходом через регистр 14, образуя таким образом вместе с регистром 14 накапливающий сумматор. В первые k тактов работы устройства происходит обнуление регистра 12 сигналами, поступающими на устройство через вход 32 начальной установки (временная диаграмма 01 на фиг. 2). При этом первые k значений функции проходят без изменения на выход блока 28 (через его первый вход) и далее через регистр 13 на вход сумматора 29. В начале работы устройства происходит также обнуление обратных связей накапливающего сумматора и аналогичной конструкции, образуемой блоками 30 и 15 (через вход устройства 32). Далее накапливаюш;ий сумматор в течение k тактов определяет сумму первых k значений функции. В каждый последующий такт на первый вход сумматора приходит код разности очередного значения f. и значения f 1-1 пришедшего на k тактов раньше. При этом в коде суммы на выходе регистра 14 компенсируется величина ранее добавленного значения . и добавляется величина значения . Таким образом, на выходе регистра 14 образуется сумма k последних значений функции. Деление суммы на число k осуществляется путем перенесения весовых функций результата на k разрядов влево. Полученный результат с выхода регистра 14 поступает на выход устройства 36. Часть младших разрядов результатов на выходе сумматора 29, а также блока 28 в дальнейшем определении значения интеграла не участвуют (отбрасываются с. потерей точности) и поступают для учета изменения делимости чисел на три в систему контроля, осуществляющую его проверку помодулю три и локализующуюыеисправности.

31

Одновременно с поступлением на вход устройства 32 значений функции на вход контрольного кода устройства 33 подаются соответствующие этим значениям контрольные коды, являющиеся остатком по модулю три значений функции. Последовательность контрольных кодов поступает на вход элемента 2 и пер- вьш вход узла 5. Элемент 2 и следую- щий за ним регистр 7 задерживают последовательность контрольных кодов на k тактов. С выхода регистра 7 задержанная последовательность контрольных кодов поступает на второй вход узла 5. На его третий вход подаются отбрасываемьш разряды с выхода блока 28.

Узел 5 сворачивает отбрасываемые разряды с выхода блока 28, определя- ет разность о- по модулю три контрольных кодов значений функции f. и f . и далее учитывает в полученном результате отбрасываемые разряды, формируя на выходе контрольный код ( у - в mod 3) rood 3. Этот код равен остатку от деления на три кода, записываемого в регистр 13, Полученный контрольный код в конце такта записывается в регистр 19. В следующем такте контрольный код поступает с выхода регистра 19 на первый вход сумматора 30. Выход сумматора 30 через регистр 15 соединен со своим вторым входом. Таким образом, после- довательно соединенные сумматор 30 и регистр 15 составляют накапливающий сумматор по модулю три. На третий вход сумматора 30 поступает об- брасываемые разряды б с выхода сум- матора 29. Сумматор 30 выполняет свертку по модулю три отбрасываемых разрядов 0 и складывает по модулю три полученный результат с контрольными кодами, пришедшими через его первый и второй входы. Полученный при этом контрольный код является остатком по модулю три кода, записываемого в регистр 3. Этот контрольный код заносится в регистр 15, с вы- хода которого поступает на вход контрольного кода устройства 37,

Поступающие через входы 31 и 33 устройства значения функции и их контрольные коды подаются также на вход узла 4 свертки и первый вход узла 9 сравнения соответственно.Узел 4 определяет код остатка от деления значения функции на три и подает его

5 О 0 5 Q

5

924

на второй вход узла 9 сравнения.Узел 9 сравнивает его с контрольным кодом и в случае их неравенства (по модулю три) вырабатывает сигнал ошибки.Этот сигнал в конце такта (по завершению переходного процесса) записывается в регистр 18 и в следующем такте поступает с выхода регистра 18 на вход триггера 23.

Аналогично описанному на вход узла 6 свертки по модулю три и первьй вход узла 10 сравнения поступают значения функции и определенные для них контрольные коды с вьгходов регистров 12 и 17 соответственно. На вход узла 7 свертки по модулю три и первый вход узла 11 сравнения поступают значения разности и вычисленные для них контрольные коды с выходов регистров 13 и 19 соответственно. На вход узла.13 свертки по модулю три и первый вход узла 8 сравнения поступают значения интеграла и вычисленные для них контрольные коды с выходов регистров 15 и 21 соответственно. Узлы 6, 7 и 3 определяют для поступивших на их входы значений коды остатков этих значений по модулю три и подают полученные коды на входы узлов 10, 11, 8 сравнения. Узлы 10, 11 и 3 сравнивают эти коды с контрольными кодами и в случае их неравенства (по модулю три) вырабатывают сигналы ошибки.Эти сигналы в конце такта записываются в регистры 19 и 15, а также в регистр 18 соответственно, и в следующем такте поступают с выходов указанных регистров на установочные входы триггеров 24, 25, 22 датчиков ошибки. На входы сброса этих триггеров приходят сигналы, поступающие через группу входов 34 блокировки сигналов ошибки устройства. Эти сигналы удерживают триггеры в состоянии Нет ошибки до прихода на их установочные входы результатов анализа полезной информации. На фиг. 2 показаны временные диаграммы этих сигналов R, Rj, Rj и R. Триггеры 22-25 представляют собой R-триггер, т.е. триггер с доминированием входа сброса над входом установки. Поэтому триггеры не реагируют на сигналы ошибки, полученные при анализе информации, предшествующей полезной. При поступлении на установочный вход триггера сигнала он переходит в состояние ошибки и удерживает его до прихода

соответствующего сигнала на вход сброса.

С выходов триггеров сигналы контроля поступают на информационные входы мультиплексора 26, на управляющий вход которого поступает код с выхода счетчика 27. До начала работы устройства счетчик удерживается в нулевом состоянии сигналом, поступающим на его вход сброса через вход 35 устройства. Далее сигнал инвертирует свое значение и счетчик начинает изменять свое состояние. При этом сигналы контроля с выходов триггеров 23 24, 25 и 22 поочередно в цикле подключаются через информационные входы мультиплексора на его выход 38 являющийся выходом контроля устройства Одновременно с этим на выход 39 локализующего кода устройства поступает код с выхода счетчика 27 однозначно соответствующий номеру триггера.

При проявлении неисправности в устройстве или на его выходах 31 или 33 ошибка будет зарегистрирована первоначально одним из датчиков ошибки и в последующих тактах будет подтверждена триггерами с большими номерами Последовательность подключения сигналов контроля с информационных входов мультиплексора 26 на его выход обеспечивает первоначальную регистрацию на выходе 38 устройства сигнала ошибки от триггеров в порядке номеров 23,. 24, 25 и 22. При этом на выходе 39 появляется код счетчика, соответствующий этому триггеру, что Однозначно указывает на место неисправности. Например, при регистрации ошибки триггером 25 его выход и выходы 39 и 38 устройства принимают значения, изображенные на временных диаграммах. Триггер 23 указывает на ошибку на входах 31 и 32 устройства, а также в узлах 4, 9, 18 и 23. Триггер 24 локализует неисправность с точностью до узлов 1, 2, 12, 17, 6, 10, 20 и 24. Триггер 25 локализует неисправность с точностью до узлов 28, 5, 13, 19, 7, 11, 21 и 25. Триггер 22 локализует неисправность с точностью до узлов 29f 30, 14, 15, 3, 8, 16 и 22.

Узел 5 свертки по модулю три выполнен в виде схемы свертки по модулю три, вход которой подключен к третьему входу узла, а выход соединен инверсно с третьим входом сумматора по модулю три, первый и второй входы которого подключены к первому и инверсно ко второму входам узла соответственно, а выход является выходом узла. Контрольный код по модулю три состоит из двух разрядов, имеющих весовые функции 1 и 2 или, что то же

самое - 1, так как 2(-1) mod 3. Инверсное подключение состоит в соединении входа первого разряда сумматора с вторым разрядом контрольного кода и входа второго разряда сумматора

с первым разрядом контрольного кода. При этом весовые функции меняются

местами, что равносильно вынесению

перед контрольным кодом знака - , т.е. подаче контрольного кода на вычитание .

Формула изобретения

Устройство цифрового интегрирования, содержащее три регистра, блок

вычитания подынтегральной функции и сумматор подынтегральной функции,причем тактовый вход устройства соединен с входами синхронизации первого,второго и третьего регистров, выход сумматора подынтегральной функции соединен с информационным входом третьего регистра, выход которого соединен с выходом интеграла устройства и входом первого слагаемого сумматора подынтегральной функции, о т л и ч а ю- щ е е с я тем, что, с целью повышения достоверности функционирования, оно содержит два элемента задержки, четыре угла сравнения, семь регистров, контрольный сумматор по модулю три, четыре триггера, счетчик, мультиплексор, пять углов свертки по модулю три, причем выход третьего регистра соединен с входом первого узла

свертки по модулю три, выход которого подключен к первому входу первого узла сравнения, тактовый вход устройства соединен с входами синхронизации регистров с четвертого по десятый, вход подынтегральной функции устройства соединен с входом первого элемента задержки, выход которого соединен с информационным входом первого регистра, выход которого соединен с входом вычитаемого блока вычитания подынтегральной функции, выход которого соединен с информационным входом второго регистра, выход которого соединен с входом второго

слагаемого сумматора подынтегральной функции, выход которого соединен с входом первого слагаемого контрольного сумматора по модулю три, выход которого соединен с информационным входом четвертого регистра, выход которого соединен с вторым входом слагаемого контрольного сумматора по модулю три, выходом контрольного кода устройства и вторым входом первого узла сравнения, выход которого соединен с информационным входом пятого регистра, выход которого соединен с входом установки в 1 первого триггера, выход которого соединен с первым информационным входом мультиплексора, выход которого соединен с выходом результата контроля устройства, первый вход начальной установки устройства соединен с входами начальной установки первого и шестого регистров, второй вход начальной установки устройства соединен с входами начальной установки третьего и четвертого регистров, вход подынтегральной функции устройства соединен с входом уменьшаемого блока вычитания подынтегральной функции и входом второго узла свертки по модулю три, выход которого соединен с первым входом второго узла сравнения, выход которого соединен с информационным входом седьмого регистра, выход которого соединен с входом установки в 1 второго триггера, выход которого соединен с вторым информационным входом мультиплексора, с первого по четвертый входы блокировки сигналов ошибки устройства соединены с входами установки в О триггеров с первого по четвертый, вход контрольного кода устройства соединен с первым входом третьего узла свертки по модулю три, вторым входом второго узла сравнения

и входом второго элемента задержки, выход которого соединен с информационным входом шестого регистра, выход которого соединен с вторым входом третьего узла свертки по модулю три, третий вход которого соединен с выходом блока вычитания подынтегральной функции, а выход подключен к

информационному входу восьмого регистра, выход которого соединен с входом третьего слагаемого контрольного сумматора по модулю три, выход первого регистра соединен с входом

четвертого узла свертки по модулю три, выход которого подключен к первому входу третьего узла сравнения, выход которого соединен с информационным входом девятого регистра, выход которого соединен с входом установки в 1 третьего триггера, выход которого соединен с третьим информационным входом мультиплексора, выход шестого регистра соединен с вторым

входом третьего узла сравнения, выход второго регистра соединен с входом пятого узла свертки по модулю три, выход которого соединен с первым входом четвертого узла сравнения, выход

которого соединен с информационным входом десятого регистра, выход которого соединен с входом установки в 1 четвертого триггера, выход которого соединен с четвертым информационным входом мультиплексора, выход восьмого регистра соединен с вторым входом четвертого узла сравнения, третий вход начальной установки устройства соединен с входом сброса

счетчика, счетный вход которого соединен с тактовым входом устройства, а выход - с управляющим входом мультиплексора и выходом кода типа неисправности устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цифрового интегрирования | 1988 |

|

SU1532922A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1348836A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Микропрограммное устройство управления с самоконтролем | 1985 |

|

SU1247871A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Устройство для сдвига информации с контролем | 1983 |

|

SU1095184A1 |

| Цифровой интегратор | 1977 |

|

SU732920A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

Изобретение относится к вычислительной технике и предназначено для применения в цифровых интегрирующих машинах. Целью изобретения является повышение достоверности функционирования устройства. Устройство содержит элементы 1, 2 задержки, узлы 3-7 свертки по модулю три, узлы 8-11 сравнения, регистры 12-21, триггеры 22-25, мультиплексор 26, счетчик 27, блок 28 вычитания подынтегральной функции, сумматор 29 подынтегральной функции, контрольный сумматор 30 по модулю три. Повышение достоверности достигнуто за счет контроля по модулю три и локализации неисправности с точностью до четырех групп блоков. 2 ил. § (/ С Я 9S 37 00 4 сл ссз го tpue.f

| Неслуховский К.С | |||

| Цифровые дифференциальные анализаторы | |||

| М.: Машиностроение, 1968, с | |||

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Микропроцессорные системы с программируемой архитектурой | |||

| М.: Радио и связь, 1984, с | |||

| Светоэлектрический измеритель длин и площадей | 1919 |

|

SU106A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-10-15—Публикация

1986-01-31—Подача