Изобретение относится к вычислительной технике и электронике и может быть использовано при построении арифметико- логических устройств обработки цифровой информации, в частности при построении многоразрядных сумматоров в качестве формирователя ускоренного переноса.

Цель изобретения - повышение быстродействия формирователя переноса.

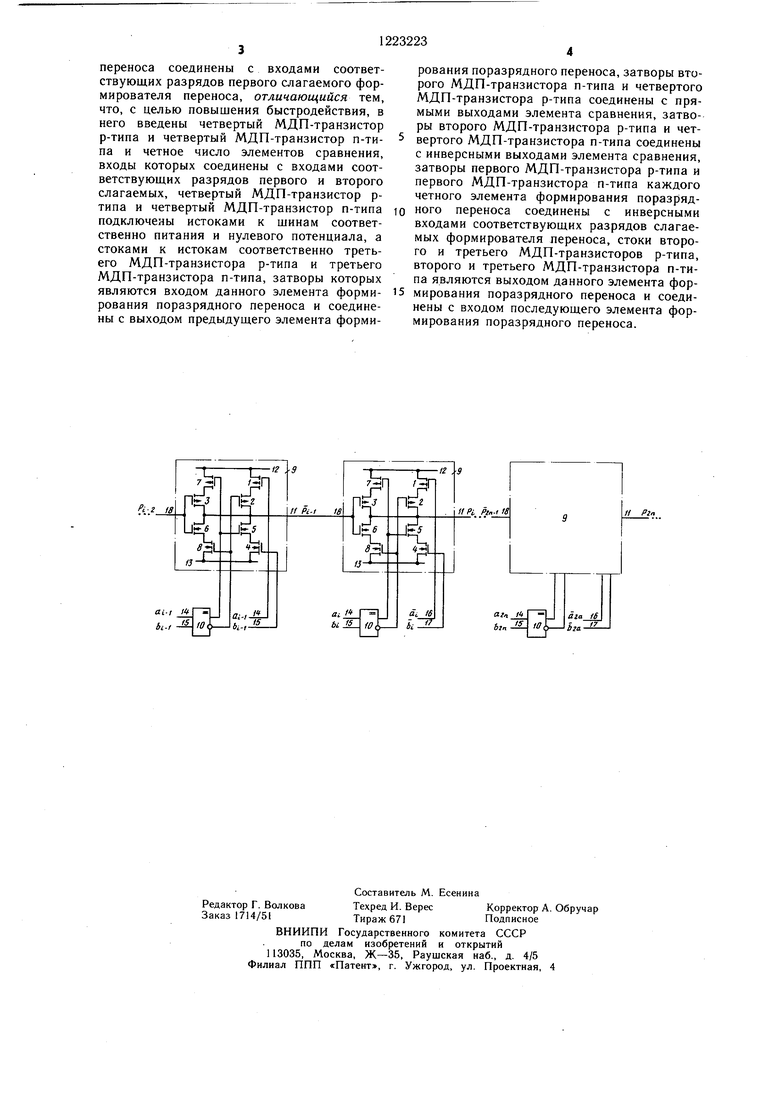

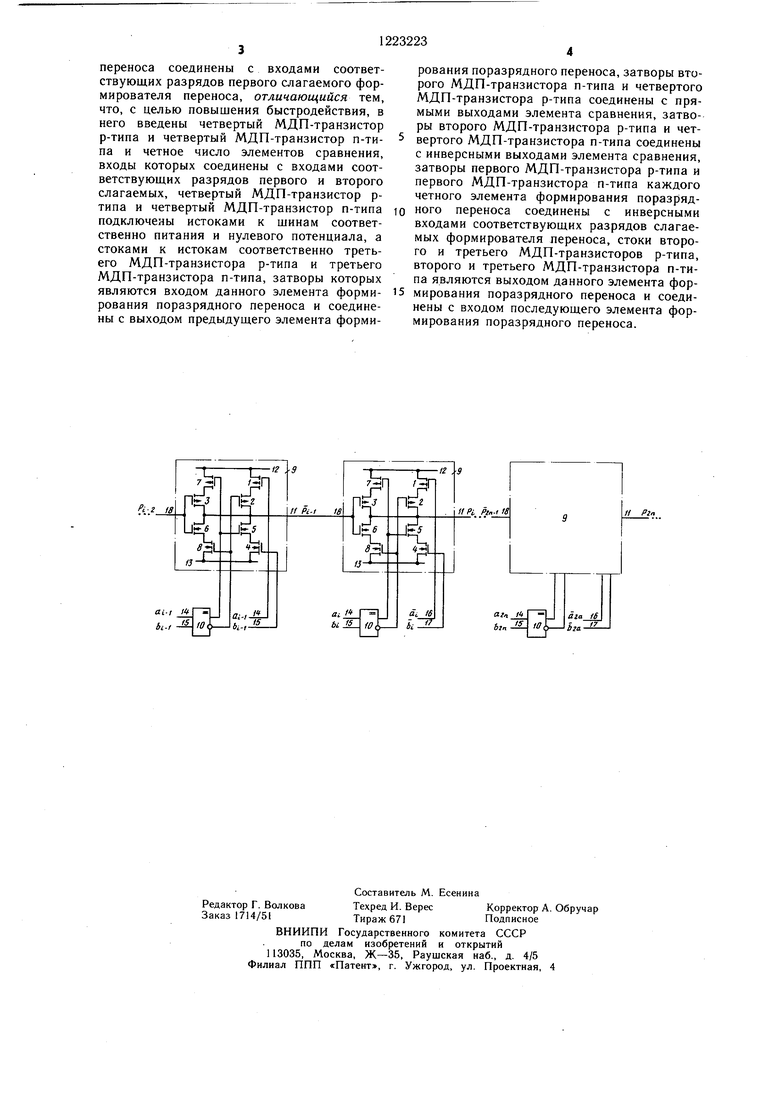

На чертеже представлена функциональная схема формирователя переноса.

Формирователь переноса содержит в каждом разряде первый, второй и третий МДП- транзисторы 1-3 р-типа, первый, второй, третий МДП-транзисторы 4-6 п-типа, четвертый МДП-транзистор 7 р-типа, четвертый МДП-транзистор 8 п-типа, образующие элемент 9 формирования поразрядного переноса, элементы 10 сравнения, выходы И элементов 9 формирования поразрядного переноса, шину 12 питания, шину 13 нулевого потенциала, входы 14 соответствующих разрядов первого слагаемого, входы 15 соответствующих разрядов второго слагаемого, инверсные входы 16 соответствующих разрядов первого слагаемого, инверсные входы 17 соответствующих разрядов второго слагаемого, входы 18 переноса элементов 9 формирования поразрядного переноса.

Формирователь переноса работает следующим образом.

Каждый элемент формирования поразрядного переноса 9 может находиться в двух режимах: в режиме формирования собственного переноса и в режиме формирования сквозного переноса. Соответствующий режим обуславливается комбинацией сигналов на прямых входах 14 и 15 слагаемых. При совпадении сигналов на указанных входах 14 и 15 (собственный перенос) элемент 10 сравнения вырабатывает на своих прямом и инверсном выходах; соответственно, высокий и низкий уровни, открывающие второй МДП- транзистор 5 п-типа, второй МДП-транзистор 2 р-типа и запирающие четвертый 7 и четвертый 8 МДП-транзисторы, соответственно, р-типа и п-типа элемента 9 формирования поразрядного переноса. Если на входах 14 и 15 слагаемых установлены низкие уровни, открывается первый МДП-транзистор 1 р-типа и закрывается первый МДП-транзистор 4 п-типа, при этом образуется канал протекания тока между шиной 12 питания и выходом 11, обеспечивающий формиров ание на выходе 11 высокого уровня. Установка на входах 14 и 15 высоких уровней приводит к формированию противоположного (низкого) уровня на выходе 11 через открытые первый МДП-транзистор 4 п-типа и второй МДП-транзистор 5 п-типа.

При несовпадении сигналов на входах 14 и 15 (сквозной перенос) схема 10 сравнения вырабатывает на своих прямом и инверсном выходах, соответственно, низкий и высокий уровни, открывающие четвертый МДП-транзистор 7 р-типа и четве:ртый МДП- транзистор 8 п-типа и запирающие второй МДП-транзистор 2 р-типа, и второй МДП- транзистор 5 п-типа, что обеспечивает формирование на выходе 11 элемента 9 формирования поразрядного переноса сигнала, инверсного по отношению к сигналу на входе 18 элемента 9. Таким образом, каждый 0 нечетный элемент формирования поразрядного переноса 9 реализует логическую формулу

,5УХ,4ЛХ,8УХ,5ЛХ,8,

5 гдеХм, Х|5 - логические значения прямых сигналов на входах слагаемых; Xi8 - логическое значение прямого сигнала переноса из предыдущего разряда.

Аналогично, каждый четный элемент 9 формирования поразрядного переноса реализует логическую формулу

Fn (X,4AX,5VX,4AX,5)V(X,4AX,5V хУХ|4ЛХ,5)АХ|бАХ,7,

где Х|б, Xi7 - логические значения инверсных сигналов на входах слагаемых

Учитывая, что , , получаем

°Ри Х,4АХ,5УХмАХ,8УХ,5АХ,8.

Таким образом, на выходах нечетных элементов 9 формирования поразрядного переноса формируются инверсные поразрядные переносы, а на выходах четных элементов 9 формирования поразрядного переноса - прямые поразрядные переносы, причем, поскольку формирователь содержит четное число элементов 9 формирования поразрядного переноса, на выходе формирователя - прямой перенос.

Формула изобретения

Формирователь переноса, содержащий четное число элементов формирования поразрядного переноса, каждый из которых содержит первый, второй и третий МДП- транзисторы р-типа и первый, второй и третий МДП-транзисторы п-типа, причем сток первого МДП-транзистора р-типа и сток первого МДП-транзистора п-типа соединены соответственно с истоком второго МДП-транзистора р-типа и истоком второго МДП-транзистора п-типа, исток первого МДП-транзистора р-типа соединен с шиной питания, ис- ток первого МДП-транзистора п-типа - с щи- ной нулевого потенциала, затворы первых МДП-транзисторов р-типа каждого нечетного элемента формирования поразрядного

переноса соединены с входами соответствующих разрядов первого слагаемого формирователя переноса, отличающийся тем, что, с целью повышения быстродействия, в него введены четвертый МДП-транзистор р-типа и четвертый МДП-транзистор п-ти- па и четное число элементов сравнения, входы которых соединены с входами соответствующих разрядов первого и второго слагаемых, четвертый МДП-транзистор р- типа и четвертый МДП-транзистор п-типа подключены истоками к шинам соответственно питания и нулевого потенциала, а стоками к истокам соответственно третьего МДП-транзистора р-типа и третьего МДП-транзистора п-типа, затворы которых являются входом данного элемента формирования поразрядного переноса и соединены с выходом предыдушего элемента формирования поразрядного переноса, затворы второго МДП-транзистора п-типа и четвертого МДП-транзистора р-типа соединены с прямыми выходами элемента сравнения, затворы второго МДП-транзистора р-типа и четвертого МДП-транзистора п-типа соединены с инверсными выходами элемента сравнения, затворы первого МДП-транзистора р-типа и первого МДП-транзистора п-типа каждого четного элемента формирования поразрядного переноса соединены с инверсными входами соответствующих разрядов слагаемых формирователя переноса, стоки второго и третьего МДП-транзисторов р-типа, второго и третьего МДП-транзистора п-типа являются выходом данного элемента формирования поразрядного переноса и соединены с входом последующего элемента формирования поразрядного переноса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Узел формирования переноса в сумматоре | 1985 |

|

SU1291969A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1287147A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1312567A1 |

| Формирователь переноса | 1991 |

|

SU1798778A1 |

| Узел формирования переноса | 1986 |

|

SU1363189A1 |

| Узел формирования переноса | 1987 |

|

SU1434426A1 |

| Формирователь переноса | 1990 |

|

SU1702361A1 |

| СУММАТОР | 1994 |

|

RU2049346C1 |

| Одноразрядный двоичный сумматор | 1987 |

|

SU1575170A1 |

| УСТРОЙСТВО СЛОЖЕНИЯ С УСКОРЕННЫМ ПЕРЕНОСОМ | 2000 |

|

RU2198421C2 |

Изобретение относится к вычислительной технике и может быть использовано при построении многоразрядных сумматоров на МДП-транзисторах в качестве схемы ускоренного переноса. Целью изобретения является повышение быстродействия за счет уменьшения емкостей, перезаряжаемых в процессе переключения. В формирователь, содер- жаший четное число эл.ементов формирования поразрядного переноса, каждый из которых содержит первый, второй и третий МДП-транзисторы р-типа, первый, второй и третий МДП-транзисторы п-типа, введены четвертый МДП-транзистор р-типа, четвертый МДП-транзистор п-типа и четное число элементов сравнения. Каждый элемент формирования поразрядного переноса может работать в двух режимах; режиме формирования поразрядного переноса и в режиме формирования сквозного переноса. Соот- ветствуюший режим обусловливается комбинацией сигналов на входах соответствующих разрядов слагаемых. I ил. ю ю со ю ГчЭ со

tii-f

. I 1 Pi Р1„- 18

tl Ля

ff

-LJ ага ff tak-Jb

| Патент США № 4357625, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-07—Публикация

1984-10-29—Подача