2. Преобразователь по п. , -о т л и чающийся тем, что запоминающее устройство содержит первый и второй суйматоры по модулю два, блок постоянной памяти и инвертор, одни входы второго сумматора по модулю два и вход инвертора являются входом запоминающего устройства, соответствующим старшему разряду кода i а выход инвертора является выходом первого разряда запоминающего устройства, одни входы первого сумматора по модулю два являются входом запоминающего устройства.

соответствующим предпоследнему старшему разряду кода, другие входы первого сумматора по модулю два являются входами запокинающего устройства , соответствующими остальным разрядам кода, а выходы первого сумматора по модулю два подключены к блоку постоянной памяти, выходы которого подключены к другим входам второго сумматора по модулю два, выходы второго сумматора по модулю два являются выходами младших разрядов устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь балансно-модулированных сигналов переменного тока в код | 1983 |

|

SU1123043A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ УГЛА ПОВОРОТА ВАЛА В КОД | 1993 |

|

RU2108663C1 |

| Преобразователь кода | 1981 |

|

SU1014144A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU1001079A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU983701A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| Двухотсчетный преобразователь синусно-косинусно-модулированных сигналов переменного тока в код | 1985 |

|

SU1283969A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1807560A1 |

| Преобразователь двоичного кода в код с произвольным весом младшего разряда | 1985 |

|

SU1325708A1 |

| Преобразователь угол-код | 1982 |

|

SU1016807A1 |

1. ПРЕОБРАЗОВАТЕЛЬ КОДА В КОДЫ ФУНКЦИЙ, содержащий первый сумматор, одни входы которого соединены с выxoдa ш источника кода смещения фаз, первое запоминающее устройство , отличающийся тем, что, с целью повышения быстродействия, в него введены дополнительные сумматоры и дополнительные запоминающие устройства, входы первого запоминающего устройства и другие входы первого сумматора являются входами преобразователя кода в коды функщгй, одни входы дополнительных сумматоров соединены с выходами источника кода смещения фаз, выходы каждого дополнительного сумматора подключены к входам соответствующего зaпo инaющeгo устройства и к другим входам последующего сумматора , а выходы первого сумматора подключены к входам первого дополнительного запоминающего устройства и к другим входам первого дополнительного сумматора.

Изобретение относится к автоматике и вычислительной технике и может быть использовано в преобразователях перемещения в код следящего уравновешивания. Известен преобразователь кода, содержащий генератор импульсов, счетчик, элементы И, одновибраторы накопитель, дешифратор и запоминающее устройство Л , Недостатком такого преобразователя кодов является низкое быстродействие. Наиболее близким к предлагаемому по техническому решению является преобразователь кода в коды функций содержаш 1й один сумматор, одни входы которого соединены с выходами источника кода смещения фаз, одно запоминающее устройство, входной ре гистр, выходные регистры, последовательно соединенные генератор импульсов , счетчик и дешифратор, выходы которого Подключены к управляю щим входам выходных регистров, входы преобразователя подключены к пер вым информационным входам входного регистра, первый управляюпщй вход которого соединен с первым выходом дешифратора, вторые информационные входы соединены с выходом одного сумматора, второй управляющий вход соединен с выходом генератора импульсов , выходы входного регистра подключены к другим входам сумматора и к входам запоминающего устройства, выходы которого подключены к информа1щонным входам выходных регистров 2j . В известном устройстве преобразование кода в коды функций каждой фазы происходит последовательно. Недостатком известного устройства является малое, быстродействие. Цель изобретения - п0вьш1ение быстродействия преобразователя. Поставленная цель достигается тем, что в преобразователь кода в коды функции, содержащий первый сумматор, одни входы которого соединены с выхрдами источника кода смещения фаз, первое запоминающее устройство, введены дополнительные сумматоры и дополнительные запоминающие устройства, входы первого запоминающего устройства и другие входы первого сумматора являются входами преобразователя кода в коды функций J одни входы дополнительных сумматоров соединены с выходами источника кода смещения фаз, выходы каждого дополнительного сумматора подключены к входам соответст ующего запоминающего устройства и k другим входам последующего сумматора, а выходы первого сумматора подключены к входам первого дополнительного запоминающего устройства и к другим входам первого дополнительного сумматора. Запоминающее устройство содержит первый и второй сумматоры по модулю

3

два, блок постоянной памяти и инвертор , одни входы второго сумматора по модулю два и вход инвертора являются входом запоминающего устройства, соответствующим старшему раз.ряду кода, а выход инвертора является выходом первого разряда запоминающего устройства, одни входы первого сумматора по модулю дваявляютс входом запоминающего устройства, соответствующим предпоследнему старшему разряду кода, другие входы первого сумматора по модулю два являются входами запоминающего устройства, соответствующими остальным разрядам кода, а выходы первого сумматора по модулю два подключены к блоку постоянной памяти, выходы которого подключены к другим входам второго сумматора по модулю два, выходы второго сумматора по модулю два являются выходами младших разрядов устройства .

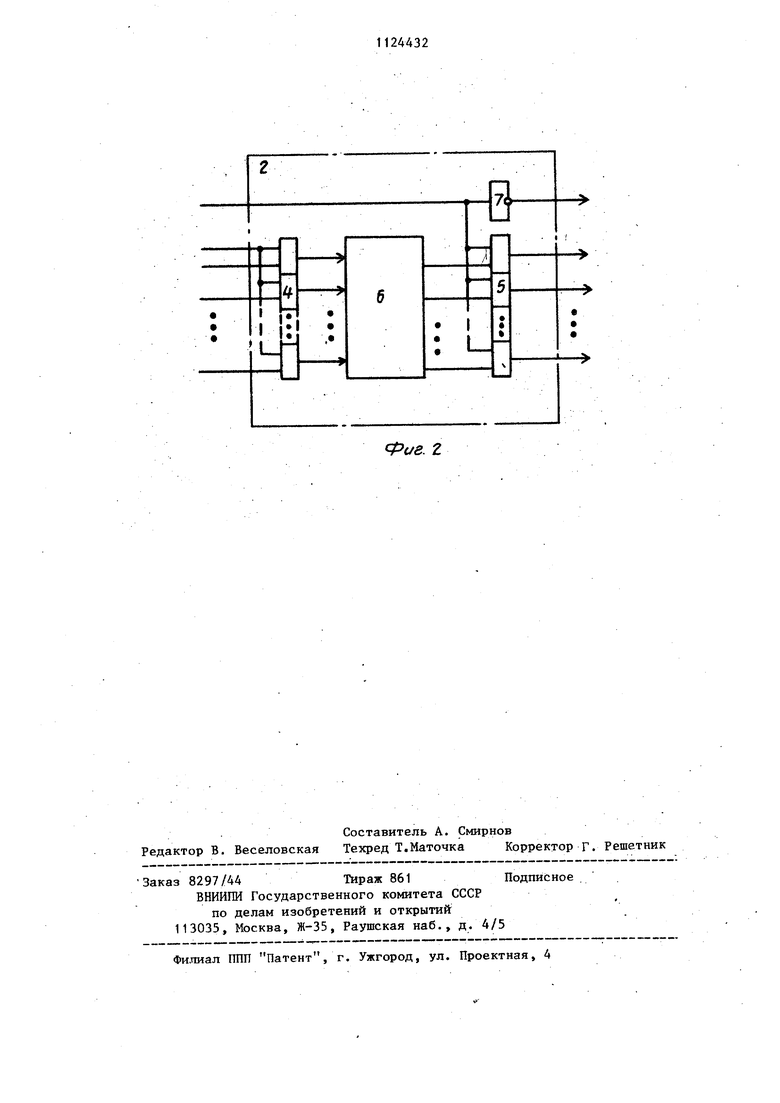

На фиг. 1 представлена структурная схема преобразователя; на фиг. 2 - структурная схема запоминанядего устройства.

Преобразователь содержит сумматоры 1, выходы которых подключены к входам запоминающих устройств 2, одни входы сумматоров 1 соединены с выходами источника 3 кода смещения фаз, входы преобразователя подключены к входам одного из сумматоров и одного, из запоминанмцих устройств 2, выходы каждого сумматора подключены к другим входам соседнего сумматора.

Запоминающее устройство 2 содержит первый 4 и второй .5 сумматоры по модулю два, блок 6 постоянной памяти и инвертор 7, вход устройства 2, соответствуняций старшему разряду кода, подключен к одним входам сумматора 5 по модулю два и через инвертор 7 - к выходу первого разря24432Л

да устройства 2, вход устройства 2, соответствующий предпоследнему старшему разряду кода, подключен к одним входам первого сумматора 4 по 5 модулю два, другие входы которого соединены с входами устройства 2, соответствуияцими остальным младшим разрядам кода, а выходы сумматора 4 по модулю два подключены к

О блоку 6 постоянной памяти, ..выходы которого подключены к другим входам второго сумматора 5 по v мoдyлю два, выходы сумматора 5 подключены к выходам младших разрядов устрой5 ства..

Преобразователь работает следующим образом.

В первом сумматоре 1 производится сложение входного кода с кодом

0 источника 3. В каждом последующем сумматоре 1 производится сложение выходного кода предьщущего сумматора 1 с кодом источника 3. Величина кода источника 3 соответствует

5 смещению по фазе между выходными кодами преобразователя. Выходные коды каждого из сумматоров 1 представляют собой адрес числа, хранящегося в запоминающих устройствах

0 2. При наличии единицы в старшем разряде входного кода запоминаняцего устройства 2 выходной код блока 6 инвертируется в сумматоре 5, а при наличии единицы в предпослед5 нем старшем разряде инвертируются остальные младшие разряды входного кода запоминающего устройства 2 в сумматоре 4..Это позволяет выполнить блок 6 для углов от О до 90 .

В предлагаемом преобразователе происходит одновременное формирование кодов функций на всех выходах, что увеличивает быстродействие по сравнению с известными преобразователями..

I

м

U

I

L.

а&. г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство преобразования кодов | 1977 |

|

SU622202A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3619805-24-24, кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1984-11-15—Публикация

1983-07-28—Подача