(54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В КОД СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU1001079A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1984 |

|

SU1156058A1 |

| Устройство для преобразования двоичного кода в код по модулю К | 1990 |

|

SU1793548A1 |

| Устройство для вычисления остатка по модулю 2 @ +1 | 1990 |

|

SU1734212A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1985 |

|

SU1269271A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1985 |

|

SU1322483A1 |

| Преобразователь непозиционного кода в двоичный код | 1988 |

|

SU1578810A1 |

| Устройство для преобразования двоично-десятичного кода в двоичный | 1985 |

|

SU1300641A1 |

| Преобразователь кодов | 1978 |

|

SU744548A1 |

1

Изобретение относится к вычислительной технике и может быть использовано для сопряжения с вычислительными устройствами, функционирующими в системе остаточных классов (СОК), а также в технике связи для передачи информации кодами СОК.

Известно устройство для преобразования кодов позиционной системы счисления в коды СОК, содержащее входные регист- Q pbi, разрядные преобразователи, вьшолненные на цифровых элементах распределения тока, с числом сердечников, равным значению соответствующего модуля состемы, обмотки записи каждого сердечника соеди-is нены с соответствующими выходами соот ветствующего входного регистра, а обмотки считьгоания соединены с входами арифметического устройства по соответствую- щему модулю системы 1

Данное устройство обладает большим объемом оборудования. Его использование затруднительно из-за необходимости иметь

преобразуемые числа представленными в десятичном коде, что приводит к необходимости иметь lOpi входных шин, где р-разрядность преобразуемого числа в десятичном коде.

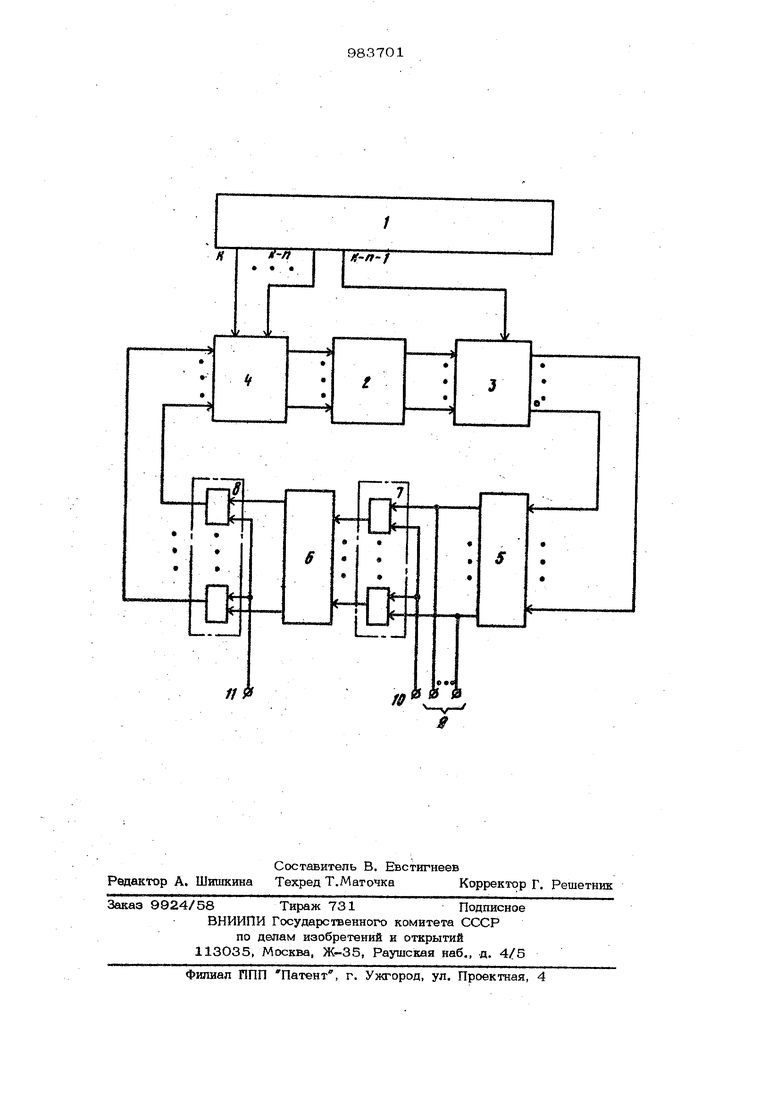

Наиболее близким к изобретению техническим решением является преобразователь двоичного кода в код системы остаточных классов, содержащий входной регистр, матричный блок умножения старшего разряда на основание двоичной системы, корректирующий матричный сумматор по соответствующему модулю, матричный блок умножения промежуточного результата по соответствующему модулю, выходной сумматор, причем выход предпоследнего старешго разряда входного регистра соединен через корректирующий матричный сумматор с матричным блоком умножен1ш промежуточного результата, выходы которого соединены с входами выходного сумматора и корректирующего матричного сумматора, вход которого соедин(н через матричный блок умножения старшего разряда с выходом последнего старшего разряда входного регистра, выход младшего разряда которого соединен с входом выходного сумматора 2 . Известный преобразователь имеет низ кое быстродействие, так как для перевода К-разрядного двоичввго числа в код СОК требуется ) тактов работы преобразователя. Цель изобретения - повьпиение быстродействия. . Поставленная цель достигается тем, что преобразователь двоичного кода в код системы остаточных классов, содержащий входной К-разрядный регистр, входы которого являются информационными входами преобразователя, блок умножения на два по модулю R,- группа из K-vt выходов которого подключена соответственно к группе из K.-V1 входов сумматора по модулю (где + 1 ), (К-Н -1)выход входного регистра подключен к (К - И - 1)-му входу сумматора по модулю Р, содержит коммутатор, первую и вторую группы элементов И, промежуточный регистр и выходной регистр, выходы которого :являются ВЫХОДОМ преобразователя и подключены к первым входам соот ветствующих элементов И первой группы, вторые входы которых объединены и являются первым управляющим входом преобразователя, входы выходного регистра подключены к соответствующим ъыаоцам сумматора по модулю , выходы элементов И первой группы подключены к соответствующим входам промежуточного регистра, выходы которого подключены к первым входам соответствующих элементов И второй группы, вторые входы которых объединены и являются вторым управ ляющим входом преобраозвателя, выходы элементов И второй группы подключены соответственно к входам первой группы входов коммутатора, вторая группа входов которого подключена соответственно к старшимк-у1 разрядам выходного регистра, вьЬсоды коммутатора подключены к соответствующим входам блока умножения на два по модулю Р,- . На чертеже представлена блок-схема преобразователя,Преобразователь включает входной регистр 1, блок 2 умножения на два по модулю Р, сумматор 3 по модулю Р, коммутатор 4, выходной регистр 5, промежуточный регистр 6, первую и вторую группы элементов И 7 и 8, выход 9 преобразователя, первый и второй управляющие входы 10 и 11. Известное устройство использует следующий алгоритм перевода двоичного числа X в код СОК по модулю X XvrtodP - (...( V wioaP )2niodPi + + Ак-г)2 + ... +-А)- 2кж7а P,{ + AQ)niod ... (1), т. е. устройство, реа лизующее известный алгоритм, потребует 2(К-1) тактов преобразования, где К - разрядность преобразуемого числа X. Если выбранный модуль Р| имеет разрядность .VI, то значение выбранного модуля лежит в пределах + 1 2 . Рассмотрим первые (К- и + 1)2 тактов преобразования известного алгорит ма (1). В ( ... (A -2rrtoaPi .-л ) 2r,oaPi + + ... + .) 2п10еЯР ,odP ... V 3 j, так как преобразуется vi старших разрядов числа X. В виду того, что значение Y старших разрядов преобразуемого числа X всегда меньше выбранного модуля , то операции коррекции по модулю не потребуется. Таким образом, значение В И-аА равно-в--А а -+А г K. ,у,, (4) т. е. И старших разрядов преобразуемого числа X. Алгоритм функционирования преобразователя может быть представлен как 1 Чтоа РГ-(.--СЪ 2.С)й K-H -VMoa ...-4A))V oaPx- ( Предлагаемое устройство работает следующим образом. В исходном состоянии регистры 5 и 6 очищены, элементы И 7 и 8 закрыты, выходы коммутатора 4 подключены к выходам группы элементов И 8, преобразуемое числоX находится во входном регистре 1. В первом такте коммутатор 4 подключает старших разрядов входного регист ра 1 к входам блока 2 умножения по выбранному модулю , на выходе которого образуется произведение значения старших разрядов преобразуемого числа X на 2 скорректированное по выбранному модулю . Этот результат суммируется по модулю Р со значением ( |i- и - 1)-го разряда Бходиого регистра 1 в сумматоре 3 по модулю P-f. Результат этой суммы в первом такте записывается в выходной регистр 5 разрядностью .И . Таким образом, в первом такте произ.водится операция V-((A r-4A.,2.-%...A,.,. « О.-+А ц,у,4. 2)2.f)iodР + , )niodP. Во втором такте на вход 10 подаегся управляющий сигнал, который открыв ае группу элементов И 7 и переписьгоает содержимое выходного регистра 5 в промежуточный регистр 6. В этом же такте коммутатор 4 подключает свои входы к выходам; группы элементов И 8 , и в этом состоянии коммутатор 4 остается до конца преобразования. Осуществляется сдвиг содержимого входного регистра 1 .на один разряд влево. В третьем такте открывается группа элементов И 8 и содержимое Промежуточного регистра; 6 через коммутатор 4 поступает на входы блока 2 умножения по модулю P;j, на выходе которого образуется результат умножения на 2 по модулю Р; содержимого промежуточного регистра б, т, е. результат первого такта и результат умножения блока 2 умножения суммируются в сумматоре 3 по модулю Р со значением А., у, разряда, и этот результат запоминается в выходном регистре 5.... Таким образом, в данном такте выполняется опер1адия X,j;(K,a.v«odP-,-+At vi-i-)wod Pf Последующие такты преобразования повторяют вышеизложенные, для пребразования потребуется ( |Сг И ) 2 - 1 тактов работы предлагаемого устройства. Таким образом; введение в состав преобразователя коммутатора, двух групп элементов И, промежуточного и выходно- го регистров и соответсвующих связей поз воляет повысить быстродействие преобразователя. «Формула изобретения Преобразователь двоичного кода в код системы остаточных класссхв, содержащий входной К,-разрядный регистр, входы которого являются информационными входами преобразователя, блок умножения на два по модулю P.J-, группа из и.-и выходов которого подключена соответственно к группе из K-VI входов сумматора по модулю Р,-,(где +1 ). (к-и-1)-й выход входного регистра подключен к (К-- и - 1)-му входу сумматора по модулю , отличающийся тем, что с целью повышения быстродействия, он содержит коммутатор, первую и вторую группы элементов И, промежуточный регистр и выходной регистр, выходы которого являются выходом преобразователя и подключены к первым входам соответх: вующих элементов И первой группы, вторые входы которых объединены и являются первым управляющим входом преобразователя, входы выходного регистра подключены к соответствующим выходам сумматора по модулю ,выходы элементов И первой группы подключены к соответс- вующим входам промежуточного регистра, выходы которого подключены к первым входам соответствующих элементов И второй группы, вторые входы которых, объединены и являются вторым управляющим входом преобразователя, выходы элементов И второй группы подключены соответственно к входам первой группы входов коммутатора, вторая группа входов которого подключена соответственно к старшим К.-И разрядам выходного регистра, выходы коммутатора подключены к оответствукдцим входам блока умножеия на два по модулю Р . Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N«-374595, кл. G06 Р 5/О2, 1973. 2.Авторское свидетельство СССР 374596, кл. GO6 Р 5/02, 1973 (прототип).

Авторы

Даты

1982-12-23—Публикация

1981-07-14—Подача