Изобретение относится к вычислительной технике, в частности к запоминающим устройствам. Известно запоминающее устройство с самоконтролем, содержащее группу накопителей, дешифратор, блок контроля и блок управления, причем выходы накопителей подключены к входа блока контроля ГЛ . Недостатками этого устройства являются ограниченная возможность его применения и отсутствие возможности исправления ошибочной информа ции. Наиболее близким к изобретению является запоминающее устройство, содержащее накопитель, блок управления , арифметический блок, блок обнаружения и коррекции ошибок, пер вьй, второй.и третий регистры, причем вход блока обнарз ения и коррек ции ошибок соединен с входом устрой ства, первый выход - с первым входо третьего регистра, второй выход с входом блока управления и первым входом арифметического блока, второй вход которого подключен к перво му выходу блока уиравления, третий вход - к выходу третьего регистра, первьй выход - к входу первого регистра, выход которого соединен и первьй выходом устройства 2. Недостатком известного устройств является низкая надежность связи с необходимостью проведения корр1екции одной и той же ошибки при каждом об ращении по адребу, содержащему ошиб ку. . , - ; Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что в заповданающее устройство с исправлением ошибок, содержащее регистр адреса, мультиплексор, бйок сравнения, накопитель, perHctp числ логический блок, бяЬк контроля и блок управления, ррйчем выход регистра адреса подключен к первым вх дам блока сравнения и мультиплексор а вход является адресным входом устройства, выход мультиплексора со динен с первым входом накопителя, .первый выход которого под:5клкмен к первому входу регистра числа, второй вход которого соединен с первым выходо м логического блока, первый вход логического блока, вход блока контроля и выход регистра чис ла являются информационным выходом устройства, информационным входом которого является второй вход логического блока, первьй выход блока управления подключен к третьим входам регистра числа и логического блока и второму входу накопителя, второй выход и первый вход блока управления являются соответственно управляющими выходом и входом устройства второй и третий .входы подключены к выходам блока контроля соответственно, введены дополнительные накопители, регистр контрольной информации, буферный регистр и регистр модифицированного адреса, вход которого подключен к первому выходу блока управления, а выход соединен с вторыми входами блока сравнения и мультиплексора, выход которого подкл бчен к первым .входам дополнительных накопителей, одни из входов регистра контрольной информации подключены соответственно к вы ходам дополнительных накопителей и второму выходу логического блока; а выходы - к вторым входам дополнительных накопителей и третьему входу Логического блока пер ВЕДИ выход ;блока .ёния подключен к третьим входам дополнительных накопителей и мультиплексора, другому входу регистра контрольной информации и ой ному из входов буферного регистра, другие входы которого соединены соответственно do вторым входом регист ра числа и информационным входом устройства, :а выход подключен к третьему входу накопителя. На фиг.1 Изображена структурная схема предложенного устройства/ на , фиг.2 - временные диаграммы его работы... , . . - .J .,/ Запомйиахщее устройство с исправЛением,ошибок содержит регистр t адреса, имеющий вход 2, блок 3 сравнения, мультиплексор 4, накопитель 5, ре- ; гистр 6 числа. Логический блок 7, при этом оно имеет информационные выход 8 и вход 9, а также блок 10 управления, имеющий вход 11 и выход 12, блок 13 контроля, регистр 14 модифицированного адреса, дополнительные накопители 15 и 16, служащие соответственно для хранения горизональиых и вертикальных контрольных сзгмм, буферный регистр 17.и регистр 18 контрольной информации

Блок 10 управления может быть выполнен из последовательно соединенных блока формирования адреса накопителя, микрокоманд, регистра микрокоманд и дешифратора.

Устройство работает следующим образом.

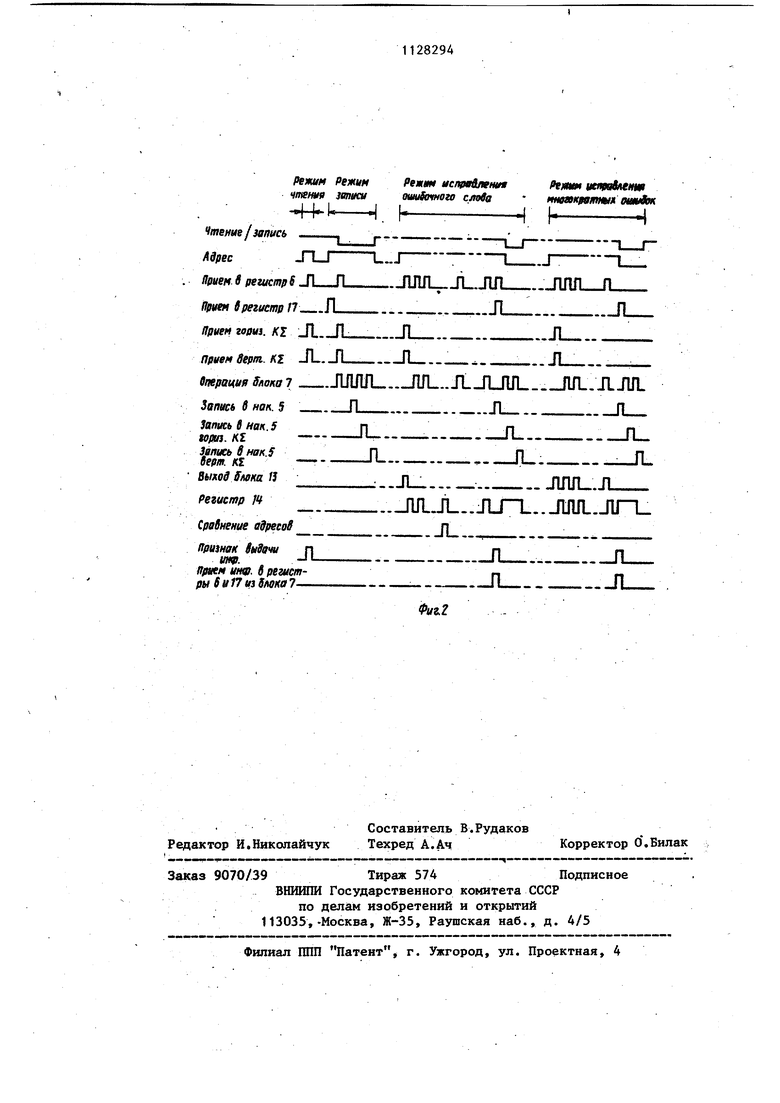

Адрес, поступающий по входу 2 регистра 1, запоминается в нем и далее через мультийлексор 4, управляемый блоком 10 управления, поступает на вход накопителя 5. Одновременно по входу 11 блока 10 сигналы Запись или Чтение поступают в блок 10 управления, которьй организовъшает работу устройства соответственно в режиме Запись или Чтение (фиг.2).

В режиме Чтение накопитель 5 вьщает на вход регистра 6 слово, считанное по поступившему адресу. С выхода регистра 6 ийформация поступает на вход блока 13. Последний анализирует исправность информации и через блок -10 управления разрешает, в случае исправной информации, вьздачу-из устройства признака выдачи информаци по его вькоду 12.

Таким образом, при исправной информации быстродействие запомина ющего устройства не снижается и равно номинальному быстродействию накопителя 5 (фиг.2, режим.Чтение).

В режиме записи устройство прини мает информацию в регистр .17 и в дальнейшем работает автономно. Блок 10 управления по поступившему сигналу Запись организовьгаает первоначально считывание информации из накопителя 5. Одновременно с накопителей 15 и 16 считываются контрольные суммы той области памяти, к которой произошло обращение, и через регистр 18 пЬступают на вход блока 7. Под управлением блока 10 бло 7 KoppekTHpyeT значение контрольных сумм, вычитая значение считанной информации (содержимое регистра 6) и сз ммируя значение содержимого реTHCTpia 17. Откорректированные контрольйые суммы помещаются обратно в регистр 18. После этого под управлением блока 10 информация с регистра 17 и контрольные суммы с регистра 1 записываются соответственно в накопителе 5 и накопителях 15 и 16.

Таким образом,контрольные модифицируются при записи каждого

нового знa leния информации и всегда отражают реально содержание накопителя 5 (фиг.2, режим Запись).

В случае обнаружения ошибки блоком 13 запрещается вьщача из устройства признака вьщачи информации. При одном ошибочном слове блок 10 управления организовывает считыва- . ние горизонтальной контрольной суммы той области памяти, в которой обнаружена ошибка, производит последовательное считывание слов всей, области памяти и вычитания их значения контрольной суммы посредством блока 7. Заведомо ошибочное слово, которое определяется сравнением адресов блоком 3 сравнения, при этом не считывается. На последнем шаге вычисления в регистре 18 определя-, ется истинное значение информации, ранее считанной ошибочной. Через регистр 17 эта информация под управлением блока 10 записывается в новую область памяти с дальнейшим обращением за ней в эту область (фиг.2, режим исправления ошибочного слова).

В случае возникновения ошибки при считывании каждого слова блок 13 определяет ее как ошибку одного разряда всех слов (случай отказа выходного усилителя), блок 10 организовывает считьюание вертикальной контрольной суммы той области памяти, которая содержит ошибки. В дальнейшем организовывается считывание всех слов данной области памяти и их прразрядное суммирование внутри одного слова с последующим вычитанием каждой поразрядной суммы из значения контрольной суммы.

Таким образом, на последнем шаге в регистре 18 определено истинное : значение всех вертикальных разрядов, считываемых ранее отказавшим выходным усилителем накопителя 5. Через регистр 17 эта информация запи- ; сывается в новую область памяти с дальнейшим обращением к этой области (фиг.2, режим исправления многократтной опшбки)..

Технико-экономическое преимущест-t во предлагаемого устройства -заключа- ется в том, что оно обеспечивает эфп фективное исправление ошибочной ин- j формации за счет наделения его функция ми самоисправления как одного ошибочно;го слова,так и многократных ошибок

Ретин записи

П JUlflTL

П.

Реяин испрвЛаенув

Реяиощеярввлетч auiuSomoto слове ннвлкрвтныя оинЛ

нч

JUUU.. .ЛЯП..ЛП

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией ошибок | 1980 |

|

SU942160A2 |

| Запоминающее устройство с коррекцией ошибок | 1978 |

|

SU744740A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Логическое запоминающее устройство | 1981 |

|

SU972589A1 |

| Запоминающее устройство с исправлением ошибок | 1984 |

|

SU1236559A1 |

| Устройство для исправления ошибок в блоках памяти | 1983 |

|

SU1100639A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU970475A1 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1432613A1 |

| Запоминающее устройство | 1981 |

|

SU972590A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ИСПРАВЛЕНИЕМ ОШИБОК, содержащее регистр адреса, мультиплексор, блок сравнения, накопитель, регистр числа, логический блок, блок контроля и блок управления, причем выход регистра адреса подключен к первым входам блока сравнения и мультиплексора, а вход является адресным входом устройства, выход мультиплексоpta соединен .с первым входом накопителя, первый выход которого подключен к первому входу регистра числа, второй вход которого соединен с первым выходом логического блока, первый вход логического блока, вход, блока контроля и выход регистра числа являются информационньм выходом устройства, информационным входом которого является второй вход логического блока, первый . .выход блока управления подключен к третьим входам регистра: числа и логического блока и второму входу накопителя , второй выход и первый вход блока управления являются соответственно управляю1цими выходом и входом устройства, второй и третий ВХОДЫ подключены к выходам блока сравнения и блока контроля соот ветственно, отличающееся тем, что, с цепью повышения надежности устройства, в него введены дополнительные накопители, регистр контрольной информации, буферный регистр и регистр модифицированного адреса, вход которого подключен к первому выходу блока управления, а 5 выход соединен с вторыми входами блока сравнения и мультиплексора, выход которого подключен к первьн входам дополнительных накопителей, одни из входов регистра контрольной информации подключены соответственно к выходам дополнительных накопителей и второму .выходу логического блока, а выходы - к вторым входам дополни Э X тельных накопителей и третьему входу логического блока, первый выход блока 1C управления подключен к третьим входам дополнительных накопителей и мультиплексора, другому входу peiPHCTра контрольной информации и одному из входов буферного регистра, другие входы которого соединены соот, ветственно с вторым входом.регистра числа и информационным входом устройства, а выход подключен к третьему входу накопителя.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с само-КОНТРОлЕМ | 1979 |

|

SU834771A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля памяти | 1979 |

|

SU769641A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-12-07—Публикация

1982-06-18—Подача