второму выходу блока обнаружений и коррекции ошибок, четвертый выход которого соединен со входом шестого регистра, выход которого подключен ко второму входу второй схемы сравнения, выходы нервой и второй схем сравнения соединены соответственно со вторым и третьим входами третьего регистра.

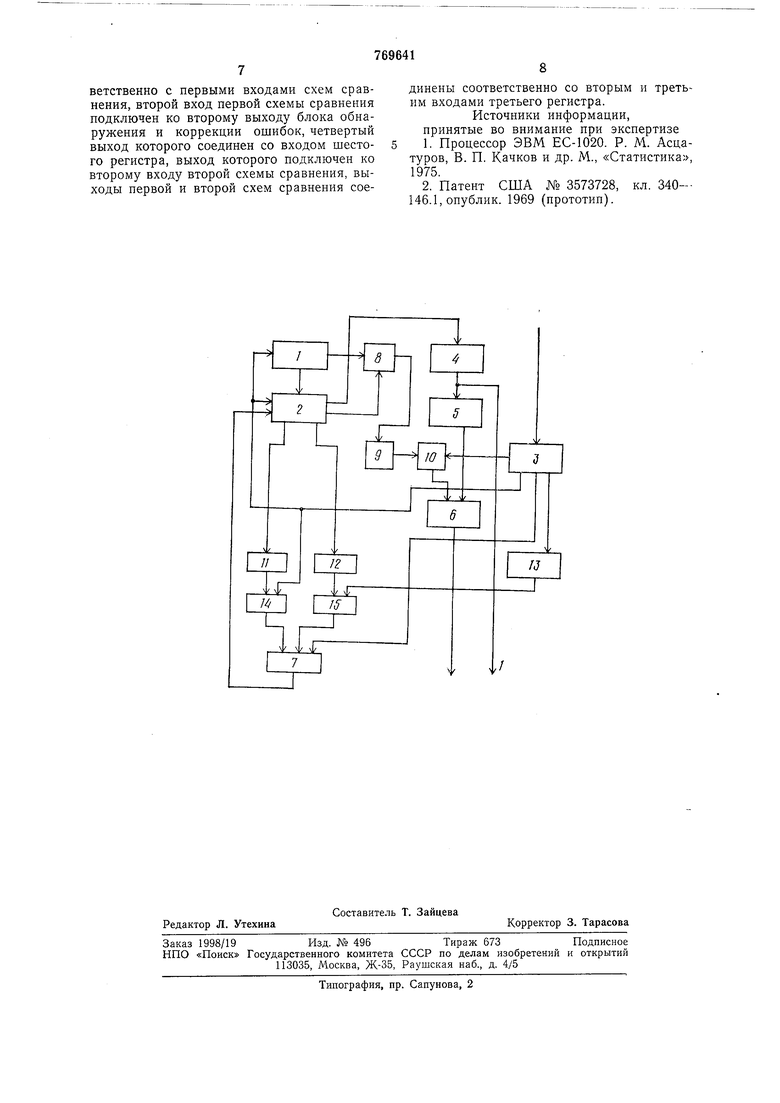

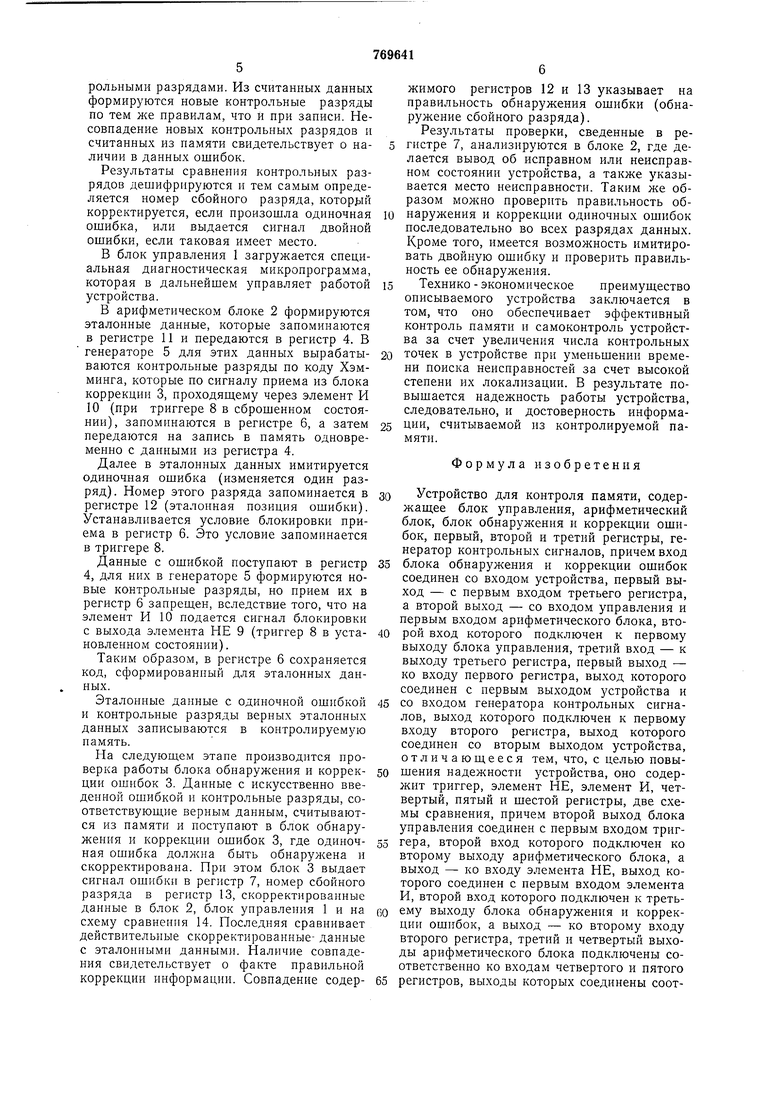

На чертел ;е изображена структурная схема предложенного устройства.

Устройство содержит блок управления 1, арифметический блок 2, блок обнаружения и коррекции ошибок 3, первый регистр 4, генератор контрольных сигналов 5, второй 6 и третий 7 регистры, триггер 8, элемент НЕ 9, элемент И 10, четвертый 11, нятый 12 и шестой 13 регистры, первую 14 и вторую 15 схемы сравнения.

Вход блока обнаружения и коррекции ошибок 3 соединен со входом устройства, первый выход - с первым входом регистра 7, а второй выход - со входом блока управления 1 и первым входом арифметического блока 2. Второй вход арифметического блока 2 подключен к первому выходу блока управления 1, третий вход - к выходу регистра 7, первый выход - ко входу регистра 4. Выход регистра 4 соединен с первым выходом устройства и со входом генератора 5, выход которого подключен к первому входу регистра 6, выход которого соединен со вторым выходом устройства. Второй выход блока управления 1 соединен с первым входом триггера 8, второй вход которого подключен ко второму выходу арифметического блока 2, а выход - ко входу элемента НЕ 9. Выход элемента НЕ 9 соединен с первым входом элемента И 10, второй вход которого подключен к третьему выходу блока обнаружения и коррекции ошибок 3, а выход - ко второму входу регистра 6. Третий и четвертый выходы арифметического блока 2 подключены соответственно ко входам четвертого 11 и пятого 12 регистров, выходы которых соедииены соответственно с первыми входами первой 14 и второй 15 схем сравиепия. Второй вход схемы сравпения 14 подключен ко второму выходу блока обнарзжения и коррекции ошибок 3, четвертый выход которого соединен со входом регистра 13, выход которого подключен ко второму входу схемы сравнения 15. Выходы схем сравнения 14 и 15 соединены соответственно со вторым и третьим входами регистра 7.

Устройство работает следуюш,им образом.

Блок управления 1 предназначен для приема и дешифрации кодов микрокоманд, поступаюш,их из контролируемой памяти через блок обнаружения и коррекции ошибок 3.

Арифметический блок 2 служит для приема, хранения и выполнения различных операций (арифметических, логических и т. д.)

над данными, поступаюшими из памяти через блок обнаружения и коррекции ошибок 3. Работа блока производится под управлением сигналов, поступающих из блока управления 1.

Блок обнаружения и коррекции ошибок 3 предназначен для непосредственного контроля считываемой из контролируемой памяти информации.

Регистр 4 предназначен для приема и хранения информации, передаваемой из арифметического блока 2 на запись в память.

Геператор 5 формирует контрольные разряды по корректируюш,ему коду для информации, принимаемой в регистр 4. Наиболее целесообразным является применение в предлагаемом устройстве корректирующего кода Хемминга, позволяющего исправлять одиночные и обнаруживать двойные ошибки.

Регистр 6 служит для приема, хранения и выдачи в память контрольных разрядов, сформированных в генераторе 5.

Регистр 7 предназначен для фиксирования ошибок в работе устройства.

Триггер 8 служит для запоминания условия блокировки приема коптрольных разрядов в регистр 6. Это условие вырабатывается в арифметическом блоке 2 с помощью управляющих сигналов из блока управления 1.

Выход триггера 8 соединен через элемент НЕ 9 со входом элемента И 10, который предназначен для клапанирования сигнала приема контрольных разрядов в регистр 6.

Регистр И хранит эталонные данные, записываемые в память в диагностическом режиме. Регистр 12 предназначен для запоминания номера разряда в данных, в который внесена ошибка.

Регистр 13 запоминает действительный номер сбойного разряда. Схема сравнения 14 сравнивает эталонные данные, хранимые в регистре 11, с действительными данными, скорректированными в блоке обиарул еиия и коррекции ошибок 3.

Схема сравнения 15 сравнивает содерл имое регистров 12 и 13 (эталонную и действительную позиции ошибки).

В случае отрицательных результатов сравнения схемы сравнения 14 и 15 выдают сигналы, свидетельствующие о наличии неисправности в устройстве, что фиксируется в регистре 7. Общий принцип контроля памяти заключается в следующем. Из информации, поступающей пз арифметического блока 2 иа запись в контролируемую память, формируются контрольные разряды в соответствии с правилами выбранного корректирующего кода и записываются в память одновременно с данными.

При каждой очередной выборке данных из контролируемой памяти носледние считываются вместе с соответствующими коптрольными разрядами. Из считанных данных формируются новые контрольные разряды по тем же нравилам, что и при записи. Несовпадение новых контрольных разрядов и считанных из памяти свидетельствует о наличии в данных ошибок.

Результаты сравнения контрольных разрядов дешифрируются и тем самым определяется номер сбойного разряда, KOTOpj3ift корректируется, если произошла одиночная ошибка, или выдается сигнал двойной ошибки, если таковая имеет место.

В блок управления 1 загружается специальная диагностическая микропрограмма, которая в дальнейшем управляет работой устройства.

В арифметическом блоке 2 формируются эталонные данные, которые запоминаются в регистре 11 и передаются в регистр 4. В генераторе 5 для этих данных вырабатываются контрольные разряды по коду Хэмминга, которые по сигналу приема из блока коррекции 3, проходящему через элемент И 10 (при триггере 8 в сброшенном состоянии), запоминаются в регистре 6, а затем передаются на запись в намять одновременно с данными из регистра 4.

Далее в эталонных данных имитируется одиночная ошибка (изменяется один разряд). Номер этого разряда запоминается в регистре 12 (эталонная позиция ошибки). Устанавливается условие блокировки приема в регистр 6. Это условие запоминается в триггере 8.

Данные с ошибкой поступают в регистр 4, для них в генераторе 5 формируются новые контрольные разряды, но прием их в регистр 6 запрещен, вследствие того, что на элемент И 10 подается сигнал блокировки с выхода элемента НЕ 9 (триггер 8 в установленном состоянии).

Таким образом, в регистре 6 сохраняется код, сформированный для эталонных данных.

Эталонные данные с одиночной ошибкой и контрольные разряды верных эталонных данных записываются в контролируемую память.

На следующем этапе производится проверка работы блока обнаружения и коррекции ошибок 3. Данные с искусственно введенной ошибкой и контрольные разряды, соответствующие верным данным, считываются из памяти и поступают в блок обнаружения и коррекции ошибок 3, где одиночная ошибка должна быть обнаружена и скорректирована. Нри этом блок 3 выдает сигнал ошибки в регистр 7, номер сбойного разряда в регистр 13, скорректированные данные в блок 2, блок управления 1 и на схему сравнения 14. Последняя сравнивает действительные скорректированные- данные с эталонными данными. Наличие совпадения свидетельствует о факте правильной коррекции информации. Совпадение содержимого регистров 12 и 13 указывает на правильность обнаружения ошибки (обнаружение сбойного разряда).

Результаты проверки, сведенные в регистре 7, анализируются в блоке 2, где делается вывод об исправном или неисправ ном состоянии устройства, а также указывается место неисправности. Таким же образом можно проверить правильность обнаружения и коррекции одиночных ошибок последовательно во всех разрядах данных. Кроме того, имеется возможность имитировать двойную ошибку и проверить правильность ее обнаружения.

Технико - экономическое преимущество описываемого устройства заключается в том, что оно обеспечивает эффективный контроль памяти и самоконтроль устройства за счет увеличения числа контрольных

точек в устройстве при уменьшении времени поиска неисправностей за счет высокой степени их локализации. В результате повышается надежность работы устройства, следовательно, и достоверность информацин, считываемой из контролируемой памяти.

Формула изобретения

Устройство для контроля памяти, содержащее блок управления, арифметический блок, блок обнаружения и коррекции ошибок, первый, второй и третий регистры, генератор контрольных сигналов, причем вход

блока обнаружения и коррекции ошибок соединен со входом устройства, первый выход - с первым входом третьего регистра, а второй выход - со входом управления и первым входом арифметического блока, второй вход которого подключен к первому выходу блока управления, третий вход - к выходу третьего регистра, первый выход - ко входу первого регистра, выход которого соединен с первым выходом устройства и

СО входом генератора контрольных сигналов, выход которого подключен к первому входу второго регистра, выход которого соединен со вторым выходом устройства, отличающееся тем, что, с целью повышения надежности устройства, оно содержит триггер, элемент НЕ, элемент И, четвертый, пятый и шестой регистры, две схемы сравнения, причем второй выход блока управления соединен с первым входом триггера, второй вход которого подключен ко второму выходу арифметического блока, а выход - ко входу элемента НЕ, выход которого соединен с первым входом элемента И, второй вход которого подключен к третьему выходу блока обнаружения и коррекции ошибок, а выход - ко второму входу второго регистра, третий и четвертый выходы арифметического блока подключены соответственно ко входам четвертого и пятого

регистров, выходы которых соединены соответственно с первыми входами схем сравнения, второй вход первой схемы сравнения подключен ко второму выходу блока обнаружения и коррекции ошибок, четвертый выход которого соединен со входом шестого регистра, выход которого подключен ко второму входу второй схемы сравнения, выходы первой и второй схем сравнения соединены соответственно со вторым и третьим входами третьего регистра.

Источники информации, принятые во внимание при экспертизе

1.Процессор ЭВМ ЕС-1020. Р. М. Асцатуров, В. П. Качков и др. М., «Статистика, 1975.

2.Патент США № 3573728, кл. 340- 146.1, опублик. 1969 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Устройство для выборки микрокоманд | 1976 |

|

SU615478A1 |

| Запоминающее устройство с коррекцией ошибок | 1978 |

|

SU744740A1 |

| Запоминающее устройство с коррекцией ошибок | 1980 |

|

SU942160A2 |

| Устройство для контроля блоков оперативной памяти | 1980 |

|

SU940242A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Процессор ввода-вывода с коррек-циЕй ОшибОК | 1979 |

|

SU849221A1 |

| Устройство для сопряжения модулейВычиСлиТЕльНОй СиСТЕМы C KOHTPO-лЕМ | 1978 |

|

SU807258A1 |

| Устройство для контроля и коррекции информации | 1980 |

|

SU940160A1 |

| Устройство для коррекции микрокоманд | 1984 |

|

SU1164709A1 |

Авторы

Даты

1980-10-07—Публикация

1979-01-10—Подача