(54) УСТРОЙСТВО СОГЛАСОВАНИЯ ТТЛ СХЕМ С МДП ИНТЕГРАЛЬНЫМИ СХЕМАМИ

вор n-канального транзистора второго инвертора подключен к затвору п-канального транзистора первого инвертора, выход которого подключен к затвору п-канального транзистора третьего инвертора, затворы р-канальных транзисторов второго и третьего инверторов подключены соответственно к выходам третьего и второго инверторов, введены два МДПтранзистора. исток п-канального транзистора подключен к шине источника отрицательного напряжения, затвор подключен к выходу первого инвертора, сток - к затвору п-канального транзистора первого инвертора и стоку р-канального транзистора, затвор которого подключен к шине нулевого потенциала, а исток - ко входу устройства и стоку входного транзистора.

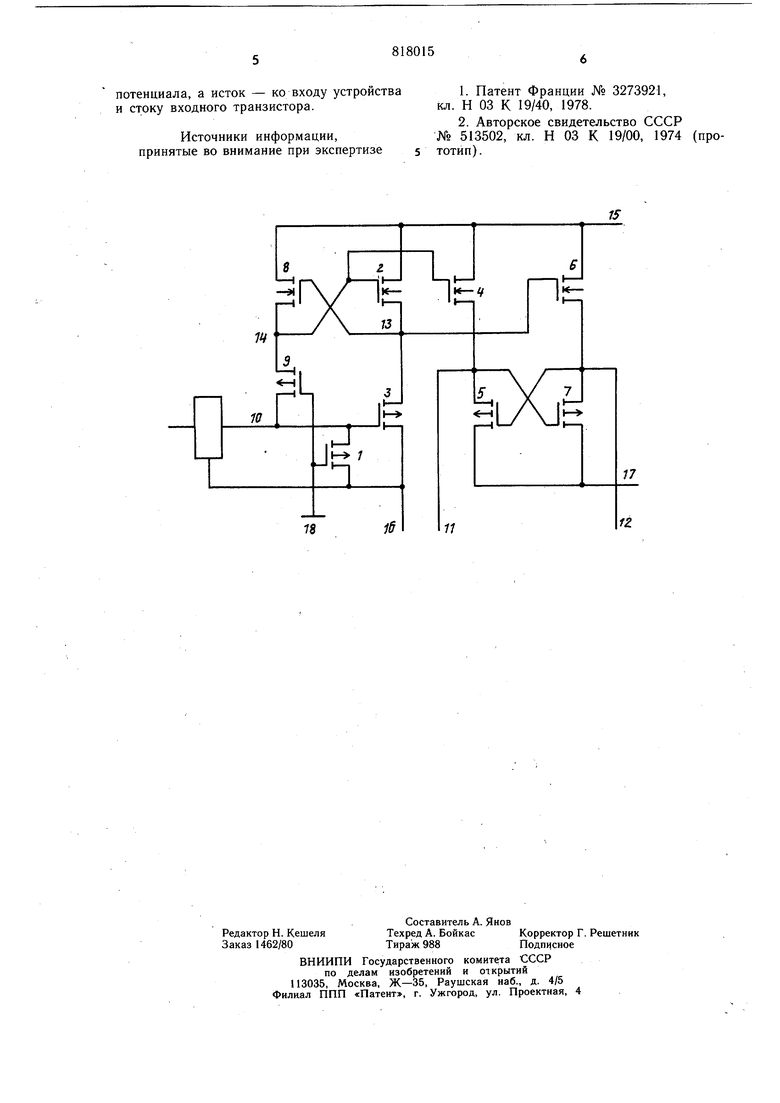

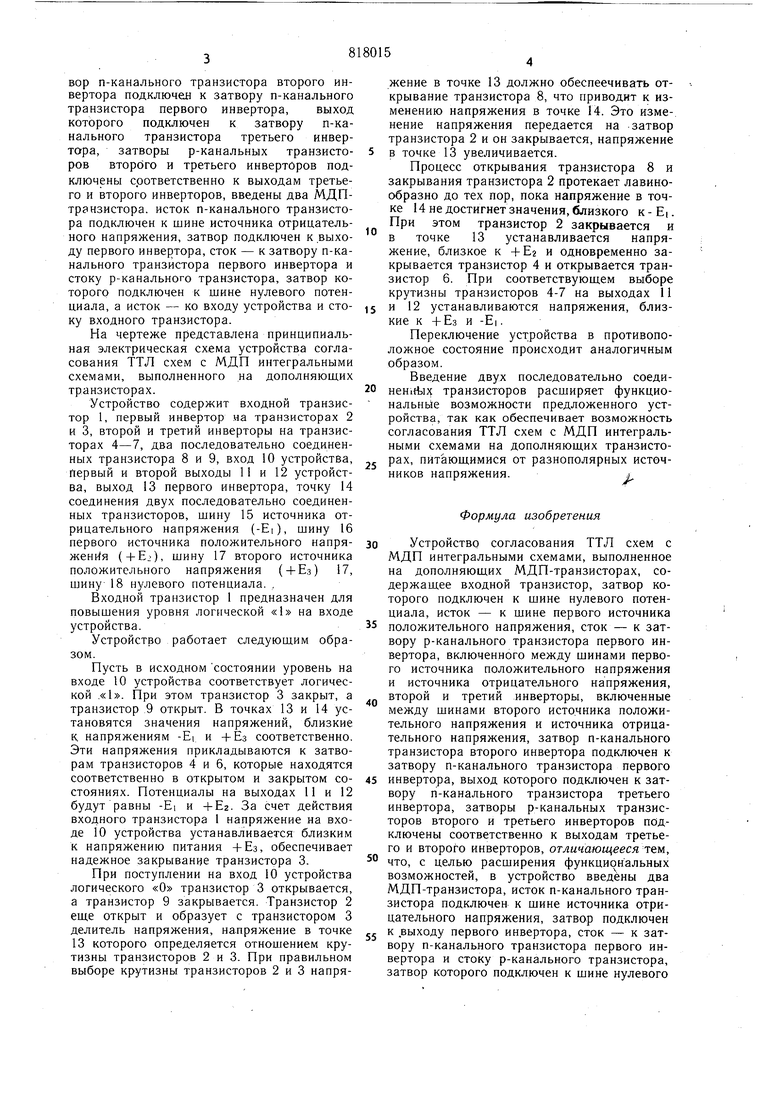

На чертеже представлена принципиальная электрическая схема устройства согласования ТТЛ схем с МДП интегральными схемами, выполненного на дополняюших транзисторах.

Устройство содержит входной транзистор 1, первый инвертор на транзисторах 2 и 3, второй и третий инверторы на транзисторах 4-7, два последовательно соединенных транзистора 8 и 9, вход 10 устройства, первый и второй выходы 11 и 12 устройства, выход 13 первого инвертора, точку 14 соединения двух последовательно соединенных транзисторов, шину 15 источника отрицательного напряжения (-E|), шину 16 первого источника положительного напряжения ( + Е.)), шину 17 второго источника положительного напряжения ( + Ез) 17, шину 18 нулевого потенциала. ,

Входной транзистор 1 предназначен для повышения уровня логической «1 на входе устройства.

Устройство работает следующим образом.

Пусть в исходном состоянии уровень на входе 10 устройства соответствует логической .«1. При этом транзистор 3 закрыт, а транзистор 9 открыт. В точках 13 и 14 установятся значения напряжений, близкие к. напряжениям -Ei и +Ез соответственно. Эти напряжения прикладываются к затворам транзисторов 4 и 6, которые находятся соответственно в открытом и закрытом состояниях. Потенциалы на выходах 11 и 12 будут равны -El и -ьЕг. За счет действия входного транзистора 1 напряжение на входе 10 устройства устанавливается близким к напряжению питания +Ез, обеспечивает надежное закрывание транзистора 3.

При поступлении на вход 10 устройства логического «О транзистор 3 открывается, а транзистор 9 закрывается. Транзистор 2 еще открыт и образует с транзистором 3 делитель напряжения, напряжение в точке 13 которого определяется отношением крутизны транзисторов 2 и 3. При правильном выборе крутизны транзисторов 2 и 3 напряжение в точке 13 должно обеспеечивать открывание транзистора 8, что приводит к изменению напряжения в точке 14. Это изменение напряжения передается на затвор транзистора 2 и он закрывается, напряжение в точке 13 увеличивается.

Процесс открывания транзистора 8 и закрывания транзистора 2 протекает лавинообразно до тех пор, пока напряжение в точке 14 не достигнет значения, близкого к - EI . При этом транзистор 2 закрывается и в точке 13 устанавливается напряжение, близкое к + ЕЗ и одновременно закрывается транзистор 4 и открывается транзистор 6. При соответствующем выборе крутизны транзисторов 4-7 на выходах 11 и 12 устанавливаются напряжения, близкие к +ЕЗ и -Е|.

Переключение устройства в противоположное состояние происходит аналогичным образом.

Введение двух последовательно соедиHeHiftix транзисторов расширяет функциональнь е возможности предложенного устройства, так как обеспечивает возможность согласования ТТЛ схем с МДП интегральными схемами на дополняющих транзисторах, питающимися от разнополярных источников напряжения.j

Формула изобретения

0 Устройство согласования ТТЛ схем с МДП интегральными схемами, выполненное на дополняющих МДП-транзисторах, содержащее входной транзистор, затвор которого подключен к шине нулевого потенциала, исток - к шине первого источника

5 положительного напряжения, сток - к затвору р-канального транзистора первого инвертора, включенного между шинами первого источника положительного напряжения и источника отрицательного напряжения, второй и третий инверторы, включенные между шинами второго источника положительного напряжения и источника отрицательного напряжения, затвор п-канального транзистора второго инвертора подключен к затвору п-канального транзистора первого

5 инвертора, выход которого подключен к затвору п-канального транзистора третьего инвертора, затворы р-канальных транзисторов второго и третьего инверторов подключены соответственно к выходам третьего и второго инверторов, отличающееся 7ем,

° что, с целью расширения функциональных возможностей, в устройство введены два МДП-транзистора, исток п-канального транзистора подключен к шине источника отрицательного напряжения, затвор подключен

J к .выходу первого инвертора, сток - к затвору п-канального транзистора первого инвертора и стоку р-канального транзистора, затвор которого подключен к шине нулевого потенциала, а исток - ко входу устройства и стоку входного транзистора. Источники информации, принятые во внимание при экспертизе s 1.Патент Франции № 3273921, кл. Н 03 К 19/40, 1978. 2.Авторское свидетельство СССР № 513502, кл. Н 03 К 19/00, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство согласования ТТЛ-элементов с МДП-интегральными элементами | 1982 |

|

SU1064469A1 |

| Устройство согласования ТТЛ-элементов с МДП-элементами | 1980 |

|

SU919089A1 |

| Формирователь парафазных импульсов | 1981 |

|

SU984013A1 |

| Устройство согласования уровней напряжения /его варианты/ | 1983 |

|

SU1138940A1 |

| Устройство преобразования уровней напряжения | 1983 |

|

SU1109907A1 |

| Устройство согласования уровней напряжения на КМДП-транзисторах | 1985 |

|

SU1483628A1 |

| Устройство для последовательного включения источников питания в МДП интегральных схемах | 1986 |

|

SU1406771A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Формирователь сигнала выборки на МДП-транзисторах | 1986 |

|

SU1338024A1 |

| Устройство согласования ТТЛ с МДП элементами | 1980 |

|

SU932617A1 |

1Z

11

Авторы

Даты

1981-03-30—Публикация

1979-04-09—Подача