1133

Изобретение относится к ш-1пульс- ной технике и может быть использованс в сачестве выходного буферного устройства, например усилители счи1Ъ1ва- ния в интегральных МДП-микросхемах, в частности в запоминающих устройст вах.

Цель изобретения - обеспечение сохранения информации на выходе устройства, особенно в случае активной нагрузки, например ТТЛ-схем, при вводе или смене данных в устройстве - достигается путем изоляции при вводе данных входа выходного усилителя от переключаемого запоминающего триггера с помощью введенного разделительного транзистора, управляемого от дополнительно введе И ых инвертора и разрядного тпанзистора сохранения предыдущего состояния триггера и, следовательно, выхода устройства за счеч , хранимого па входной емкости, выходного усилителя.

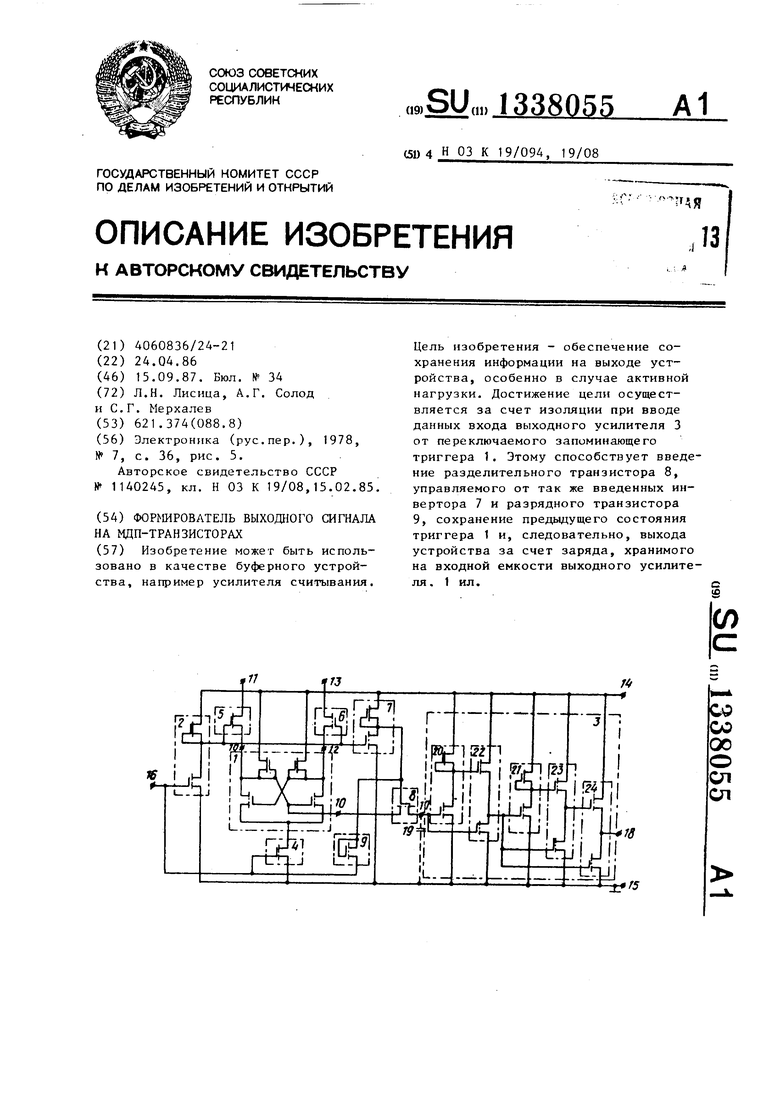

Па чертеже изображена прпнц1тиаль ная схема формирователя выходного сигнала на МДП-транзисторах. Устрой- CTUO содержит триггер 1, инвертор 2, выходной усилитель 3, ключевой транзистор 4, первый 5 и второй 6 пере- к.чючающие транзисторы, дополнительны инвертор 7, разделительны транзисто 8 и разрядный транзистор 9,

Первый выход.10 триггера 1 через периь пере ключающи транзистор 5 подко Бочен к перво входной шине II данных, а второй выход 12 триггера 1 через второй переключающий транзис тор 6 под слючег к второй входной тине 13 данных. Триггер 1 соединен последов ательпо с ключевьЕч транзисторо 4 шиной 14 питания и общей шиной 15, Затвор кльачевого тра11зистора 4 об 1 единен с истоком шзрядного транзистора 9 и входом инвертора 2 и подключен к тактовой шине 16. Выход инвертора 2 подкл очен к затворам первого 5 и второго 6 переключающих транзисторов и входу дополнительного инвертора 7, выход которого соединен с затвором и стоком разрядного транзистора 9 и с затвором разделительного транзистора 8, который включен м между первым выходом 10 инвертора 1 и входом 17 выходного усилителя 3, выхо,ц 18 которого является выходной шиной устройства.

На чертеже показан также паразит

иый конденсатор 19, емкость которого

рав.ча емкостей iicTiJKa разделительного транзистора 8 и входной емкости входтюго усшнп еля 3 и приведен

пример конкретногч) вьпюлиения выходно- .,

го усилителя 3 по трехкаскаднои схеме

с использованием первого 20 и второго 21 инверторов и трех последовательно соединенных парафазных каскадов 22,

23 и 24.

Устройство работает следующим образом.

При вводе 11Н(|.)ормации в устройство на тактовую шину 16 подается ci-и нал

низкого уровня, который закрывает

ключевой транзистор 4. Благодаря току через разряднь. й транзистор 9 закрывается также paздeлитeJ Iьныi l транзистор 8, Состояние тр птера 1 при этом не успевает заметно измениться, и на конденсаторе 19 сох 5аняется заряд, соотиетству;шций напряжению на мерв ом выходе 10 триггера 1 до момента переключения триггера. Этот заряд поддер- юшает логическое состояние выходной шины 18 устройства, жзско.чьку его уте ;ка через затворы МДП-транзисторов элеме ггов выходного усилителя 3 крайне незначительна. При этом к выходной шине 18 устройства может быть подключена любая нагрузка, в том числе активная, например в виде ТТЛ схем.

5

О

5

На выходе инвертора 2 4)Ормируется при зтом ВЫСОКИ потенцпал, котор1йй открывает переключающие транзисторы 5 и 6 и поддерживает дополнительньш инвертор 7 в нулевом состоянии на выходе, что удерживает разделительный транзистор 8 в закрытом состоянии.

На входные шины 11 и 13 данных подаются взаимно дополняющие сигналы, . которые через открытые переключающие транзисторы 5 и 6 поступают на выходы 10 и 12 триггера 1, который при этом отключен от общей ишны 15 благодаря 11акрытому ключевому транзистору 4. Когда выходы триггера 10 и 12 в соответствии с информацией на входных шинах 11 и 13 изменят свое состояние за уровень порога перектпо- чения триггепа I, на тактовую шину 16 подается сигнал высокого уровня, ключевой транзистор 4 открывается, g подк.тночая триггер 1 к общей иипе 15, и регенеративный процесс перб ключения триггера завершается.

Одновременно на выходе инвертора 2 формируется сигнал низкого уровня.

0

которым закрырае:т переключающие транзисторы 5 н 6, отключая входные шины 11 и 13 данных от триггера 1 для подготовки их к новому циклу.

Дополнительны инвертор 7 гфи этом переходит в единичное состояние и открывает разделительный транзистор 8, а разрядный транзистор 9 закрывается, так как на его истоке высокий потенциал .

Информационный сигнал с первого выхода 10 триггера 1, соответств аощий его новому состоянию, передается на вход 17 выходного усилителя 3, который срабатывает и Р зменяет состояние выходной 1В устройства.

TaKiiM образом в процессе ввода (записи) информации в устройство, состояние его выходной шины не изменяется .

Фор

у л а и 3 о б р е т е н и я

Формирователь выходного сигнала на МДП-транзисторах, содержащий триггер, выходной усилитель, инвертор, ключевой транзистор, первый и второй переключающие транз1гсторы, первый

Составитель В. Лементуев Редактор Л. Маковская Техред М.Ходамич Корректоре. Шекмар

Заказ 4144/55Тираж 901

ВПНИИИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

11роизяод(.г-ненно-г1олиграфическое предприятие, г. Ужгород, ул. Проектная, 4

выход триггера через ги;р1 ый 1К р( 1,лю- чающий транзистор соед11нсн с п -рвоГ) входной шиной даигп. х, а пторой ныход соответственно через BTopoii переключающий транзистор - с рторой входной шиной данн1 х, тр1И гер включен последовательно с Kn 04Cnb N ГрЛИЗИСТОрОМ

ieждy шиной питания и общей тиной,

затвор ключевого транзистора подклю-, чен к тактовой шине и входу инвертора, выход которого соед1И ен с затворами первого и второго переключающих транзисторов, о т л и ч а ю щ и йс я тем, что, с целью сохранения 1 :нформации на выходе устройства при вводе данных, в него введены дополни- тель; .ый инвертор, разрядный и разделительный транзисто.)ы, ггричем выход

инвертора соединен с вхс дом дополнительного инвертора, выход которого ггодключен к затвору и стоку разрядного транзистора и затвору раздетп - тельного транзистора, которьгй BKJHOчен между первым выходом триггера и УХОДОМ выходного ус:илп1теля, выход ко торого является выходной UIUHOJ уст- pojicTBa, а исток разрядного транзистора соединен с тактовой шиной.

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Адресный формирователь | 1981 |

|

SU1014027A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Устройство согласования ТТЛ-элементов с МДП-элементами | 1980 |

|

SU919089A1 |

| Усилитель-формирователь выходных сигналов постоянных запоминающих устройств на МОП-Транзисторах | 1983 |

|

SU1140245A1 |

| Буферное устройство | 1979 |

|

SU822366A1 |

| Квазистатический счетный триггер на мдп-транзисторах | 1975 |

|

SU632060A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Реверсивный счетчик на мдп-транзисторах | 1977 |

|

SU711690A1 |

| Элемент памяти для регистра сдвига | 1978 |

|

SU706880A1 |

Изобретение может быть использовано в качестве буферного устройства, например усилителя считывания. Цель изобретения - обеспечение сохранения информации на выходе устройства, особенно в случае активной нагрузки. Достижение цели осуществляется за счет изоляции при вводе данных входа выходного усилителя 3 от переключаемого запоминающего триггера 1. Этому способствует введение разделительного транзистора 8, управляемого от так же введенных инвертора 7 и разрядного транзистора 9, сохранение предыдущего состояния триггера 1 и, следовательно, выхода устройства за счет заряда, хранимого на входной емкости выходного усилителя. 1 ил. с (Р L:L. rJ«i Гп -feJ eg 00 00 о ел ел I .,.

| Электроника (рус.пер.), 1978, № 7, с | |||

| Коридорная многокамерная вагонеточная углевыжигательная печь | 1921 |

|

SU36A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Усилитель-формирователь выходных сигналов постоянных запоминающих устройств на МОП-Транзисторах | 1983 |

|

SU1140245A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-09-15—Публикация

1986-04-24—Подача