Изобретение касается способа модулирования сигналов, устройства модулирования сигналов, способа демодулирования сигналов и устройства демодулирования сигналов, которые используют для записи или воспроизведения цифровых сигналов, таких, как цифровые речевые сигналы, цифровые видеосигналы и данные на носителе записи, и, например, способа модулирования сигналов, устройства модулирования сигналов, способа демодулирования сигналов и устройства демодулирования сигналов, которые можно приспосабливать к эталонному устройству для постоянного оптического диска или к устройствам записи- воспроизведения для перезаписываемого оптического диска.

Предпосылки создания изобретения

При записи цифровых сигналов, таких, как цифровые речевые сигналы, цифровые видеосигналы или данные, вначале к цифровым сигналам добавляются данные кода исправления ошибок, и получающиеся данные маршрутизируются в схему модулирования, где он преобразуется посредством канального кодирования в код, подходящий к характеристикам системы записи-воспроизведения.

Оптический диск, такой, как компакт-диск (КД), представляет собой среду записи, имеющую широкую область применения в качестве блочной среды для видеоинформации или в качестве запоминающего устройства для вычислительной машины. Система на оптических дисках воспроизводит сигналы, записанные на отражательной поверхности диска через прозрачную подложку, имеющую толщину порядка 1,2 мм. На оптическом диске записывают такую информацию, как преобразованные в цифровую форму сигналы звукового сопровождения, видеосигналы или цифровые данные. В этом случае, к цифровым сигналам добавляют данные кода исправления ошибок, и получающиеся данные маршрутизируются в схему модулирования, где они преобразуются посредством так называемого канального кодирования в кодовые данные, соответствующие характеристикам системы записи-воспроизведения.

Формат сигнала вышеупомянутой системы на компакт-дисках (КД) можно кратко представить следующим образом:

Частота выборки - 44,1 кГц

Количество двоичных разрядов квантования - 16 (линейного)

Система модуляции - EFM

Скорость передачи канальных разрядов - 4,3218 мегабит в секунду

Система коррекции ошибок - C1R1 (перекрестно-перемежающийся код Рида-Соломона)

Скорость передачи данных - 2,034 мегабит в секунду

Используемая система модуляции представляет собой преобразование 8-14 или EFM.

В случае модуляции EFM, входной 8 разрядный код, далее называемый символом, преобразуется в 14-канальный двоичный код, к которому добавляется сигнал кадровой синхронизации из 24 канальных двоичных разрядов и дополнительный код из 14 канальных двоичных разрядов, и соседние коды соединяются посредством объединяющих разрядов, состоящих из трех канальных двоичных разрядов. Получающиеся данные регистрируются системой модуляции NRZI (без возвращения к нулю с инверсией).

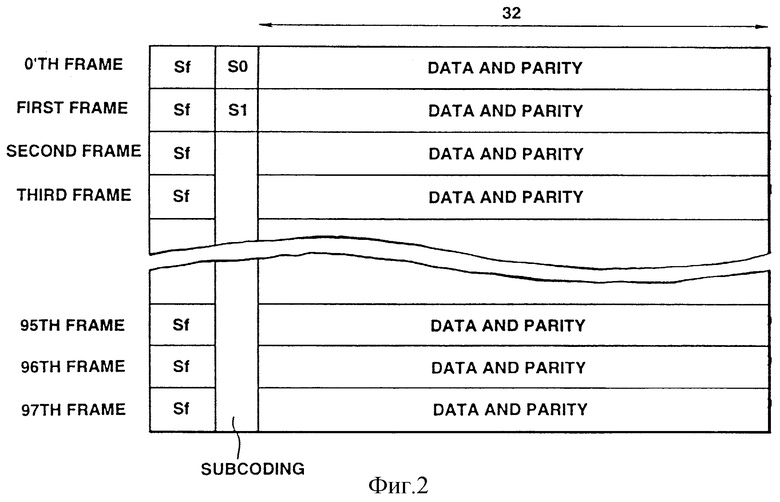

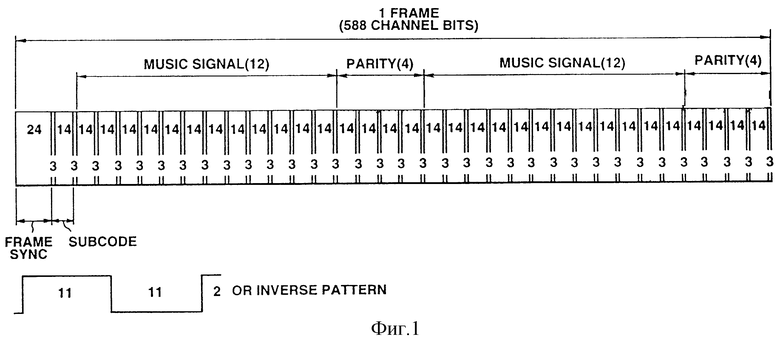

На фиг. 1 показана структура кадра системы из компакт-диска.

Рассматривая фиг. 1, видим, что 24-символьные данные (сигналы музыки) и 8 символов контроля по четности, поступающие в схему модулирования из устройства кодирования перекрестно- перемежающимся кодом Рида-Соломона (ППКРС) во время синхронизации (6 областей значений выборок, шесть выборок, каждая из L и P каналов, где каждая выборка представляет 16-разрядные данные), преобразуются в 14 канальных двоичных разрядов и присоединяются объединяющими двоичными разрядами из трех канальных разрядов с целью получения 588 канальных разрядов на кадр. Получающиеся данные регистрируются системой без возвращения к нулю с инверсией (БВНИ) на скорости передачи канальных двоичных разрядов, равной 4,3218 мегабит в секунду.

Соответственные символы, поступающие в схему модулирования, преобразуются относительно таблицы преобразования, составленной из постоянного запоминающего устройства (ПЗУ), в комбинацию канальных разрядов, в которой количество "0"-й между "1" и "1" не менее 2 и не более 10. Комбинация канальных разрядов сигнала кадровой синхронизации Sf представляет "100000000001000000000010" в двоичном выражении. Что касается комбинации граничных разрядов, то выбирают одну из комбинаций "000", "001", "010" и "100". Каждый кадр субкодирования составлен из 98 кадров. В качестве субкадра для 0-го и первого кадров добавляют сигнал синхронизации субкадра S0 (равного "00100000000001") и S1 (равного "00000000010010") (см. фиг. 2).

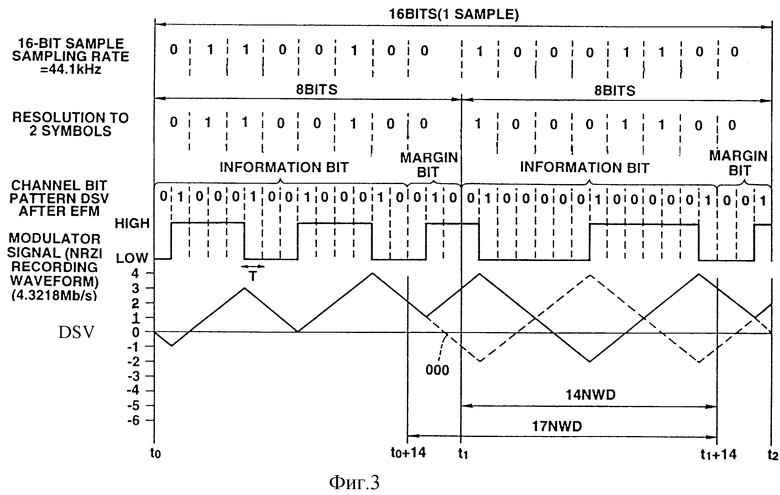

На фиг. 3 показана для типичного значения выборки входных данных комбинация канальных разрядов после модуляции EFM и изменения цифровой суммы (ИЦС).

Каждая 16-разрядная выборка разбивается на старшие 8 двоичных разрядов и младшие 8- двоичных разрядов, каждые из которых поступают в схему модуляции через кодирующее устройство ППКРС для преобразования 8-14 с целью получения 14 канальных информационных двоичных разрядов. Между "1" и "1" информационных разрядов, как описано выше, расположено не менее 2 и не более 10 "0"-й. Выбирается одна из комбинаций объединяющих двоичных разрядов "000", "001", "010" и "100". Это правило наблюдается всегда при соединении частей 14 информационных двоичных разрядов, так что сигналы EFM, основанные на 17-канальных разрядах, вырабатываются и выводятся из схемы модулирования со скоростью 4,3218 мегаразрядов в секунду. Количество канальных разрядов, в случае сигнала кадровой синхронизации Sf, составляет 27.

Поскольку между произвольным канальным разрядом "1" и следующим канальным разрядом "1" расположено не менее 2 и не более 10 канальных разрядов, период, в течение которого продолжается высокий уровень или низкий уровень формы сигнала записи без возвращения к нулю с инверсией (БВНИ), то есть длина волны записи, необходим не менее 3Т и не более 11Т (фиг. 3).

В этом случае самая короткая длина волны записи составляет 3Т, а самая большая длина волны записи составляет 11Т, где Т представляет период синхронизации канала, равный 4,3218 МГц. Это далее называется правилом 3Т-11Т регулирования модуляции EFM.

Теперь рассмотрим значение или изменение цифровой суммы (ИЦС) в качестве показателя баланса по постоянному току формы сигнала записи БВНИ. Изменение ИЦС задается в виде временного интервала формы сигнала записи. То есть, вариант ИЦС, когда высокий уровень формы сигнала записи продолжается в течение единичного времени Т, представляет +1, тогда как вариант ИЦС, когда низкий уровень формы сигнала записи продолжается в течение единичного времени Т, представляет -1.

Временное изменение ИЦС, когда предполагается, что начальное значение ИЦС в момент времени t0 равно нулю, приведено в самой нижней части фиг. 3. Модулированный сигнал в течение времени от t1 до t2 не однозначно определяется 17-канальной комбинацией двоичных разрядов "01000001000001001", а зависит от уровня модулированных сигналов в момент времени t1, то есть от конечного уровня формы модулированного сигнала в течение временного интервала от t0 до t1 (далее называемого CWLL).

Таким образом, показанная форма модулированного сигнала представляет форму CWLL в момент времени t0, находящуюся на низком уровне (CWLL = "0"). Форма модулированного сигнала для GWLL = "1" (высокий уровень) инвертируется из комбинации для CWLL = "0", так что высокий и низкий уровни инвертируются в низкий и высокий уровни, соответственно.

Аналогичным образом, ИЦС также увеличивается и уменьшается в зависимости от CWLL, так что если CWLL = "0" в момент времени t0, вариант ИЦС с информационной комбинацией "01000100100010" (далее называемый 14 NWD), то есть вариант ИЦС в течение периода времени от t0 до t0 +14 представляет +2, как показано на фиг. 3. И, наоборот, если CWLL = "1" в момент времени t0, то 14NWD = -2. Вариант ИЦС с момента времени t0 + 14 до t1 + 14 называется 17NWD.

Теперь приведем пояснение граничным двоичным разрядам, вводимым между моментами времени t0 + 14 и t1. Из четырех комбинаций двоичных разрядов "000", "001", "010" и "100", комбинацию "001" или "100" нельзя вводить по вышеупомянутому правилу 3Т-11Т, так что можно вводить только "010" или "000". То есть, если количество "0"-й на заднем конце предыдущей комбинации информационных разрядов, выводимых до объединяющего разряда, составляет В, а количество "0"-й на ведущем конце впоследствии выводимой текущей комбинации информационных разрядов составляет А, то поскольку В=1 и А=1, ведущий и задний концы объединяющего разряда должны быть "0" и "0", так что комбинация объединяющих разрядов, которые можно вводить, становится равной "OXO", где X является произвольным разрядом (безразлично).

В самой нижней части фиг. 3 показано изменение ИЦС с разрядами "010", введенными в качестве объединенных разрядов, сплошной линией, тогда как ИЦС с разрядами "000", введенными в качестве объединяющих разрядов, показано пунктирной линией. Обычно, подлежащие введению объединяющие разряды в месте соединения необходимо выбирать так, чтобы удовлетворялось правило 3Т-11Т регулирования модуляции. Аналогичным образом, запрещаются такие объединяющие разряды, которые при введении создают повторение по два раза комбинации 11Т, которая такая же, как и комбинация кадровой синхронизации 11Т.

Из удовлетворяющих вышеупомянутым требованиям объединяющих разрядов выбирают в качестве оптимальных такие объединяющие разряды, которые при введении создают наименьшее абсолютное значение накопленного ИЦС от объединяющего разряда до конца следующей комбинации информационных разрядов, подсоединенной к преобладающему накопленному ИЦС.

В показанном на фиг. 3 примере ИЦС в момент времени t1 + 14, при введении объединяющих разрядов "010", представляет +3, тогда как в тот же временной момент, при ведении объединяющих разрядов "000", ИЦС составляет -1, так что выбираются объединяющие разряды "000".

Определяемые вышеописанным алгоритмом объединяющие разряды удовлетворяют правилу 3Т-11Т регулирования модуляции в соединяющей части между двумя 14- разрядными данными, запрещая в то же время генерирование ошибочного сигнала кадровой синхронизации и приближая накопленное изменение ИЦС сигнала EFM к значению, по возможности, ближе к нулю.

Между тем, в случае обычной системы EFM, поскольку самая короткая длина серии ограничивается двумя, два объединяющих разряда достаточны, если это необходимо для цели перекрытия ограничениями длины серии. Если количество объединяющих разрядов можно уменьшить до двух, плотность записи данных можно увеличить на коэффициент 17/16 без изменения физического размера, например, длины волны записи.

Однако существуют только три сорта двухразрядных объединяющих двоичных разрядов. Кроме того, часто происходит то, что можно вводить только один из трех сортов объединяющих разрядов из-за ограничений, типа ограничений, налагаемых длиной серии. Таким образом, в случае обычной системы управления изменением ИЦС, здесь присутствует большое количество областей, в которых невозможно управлять ИЦС. В результате этого, низкочастотные составляющие модулированных сигналов нельзя в достаточной степени подавлять с целью воздействия на сервостабилизацию или частоту появления ошибок в данных при демодуляции данных.

Ввиду вышеизложенного, основной целью настоящего изобретения является обеспечить способ модулирования сигналов, устройство модулирования сигналов, способ демодулирования сигналов и устройство демодулирования сигналов, благодаря которым входные М двоичных разрядов, типа входной 8- разрядной кодовой последовательности, непосредственно преобразуются в N-канальные двоичные разряды, например, в 16- канальные двоичные разряды, без использования вышеупомянутых объединяющих разрядов во время модулирования сигналов, снижая тем самым плохие воздействия на управление ИЦС, а также позволяя осуществлять достаточное подавление низкочастотных составляющих.

Раскрытие изобретения

В соответствии с настоящим изобретением обеспечен способ модулирования сигналов, предназначенный для преобразования информационной последовательности на М-разрядкой основе в кодовую последовательность на N-разрядной основе, где М и N являются целыми числами, имеющими соотношение M<N, и для соединения N- разрядного кода со следующим N-разрядным кодом, причем способ включает в себя: первый этап приема информационной последовательности на М-разрядной основе в качестве значения входного сигнала; второй этап преобразования М-разрядных данных в N-разрядный код в соответствии с таблицей преобразования и третий этап вывода кодовой последовательности на N-разрядной основе в качестве результата модуляции. Таблица преобразования составлена из первой и второй подтаблиц, включающих в себя многочисленные кодовые группы, соответственно. Многочисленные кодовые группы включают в себя различные коды для одинаковых входных данных. Вторая подтаблица представляет собой таблицу, которая частично дублируется первой подтаблицей и создается посредством назначения различных кодов для данных первых входных данных вторым входным данным первой подтаблицы. Первую и вторую подтаблицы составляют так, что кодовые наборы дублированных частей принимают варианты изменений цифровой суммы, которые имеют противоположные знаки. Коды назначают последовательно всем кодовым группам в дублированных частях первой и второй подтаблиц относительно входных данных от кода, имеющего максимальное абсолютное значение варианта изменения цифровой суммы.

В соответствии с настоящим изобретением обеспечено также устройство модулирования сигналов, предназначенное для преобразования информационной последовательности на М-разрядной основе в кодовую последовательность на N-разрядной основе, где М и N являются целыми числами, имеющими соотношение М<N, и для соединения N-разрядного кода со следующим N-разрядным кодом, причем устройство включает в себя: средство приема, предназначенное для приема информационной последовательности на М- разрядной основе в качестве значения входного сигнала; средство преобразования, предназначенное для преобразования М-разрядных данных в N-разрядный код в соответствии с таблицей преобразования, и выходное средство, предназначенное для вывода кодовой последовательности на N-разрядной основе в качестве результата модуляции. Таблица преобразования состоит из первой и второй подтаблиц, включающих в себя многочисленные кодовые группы, соответственно. Многочисленные кодовые группы включают в себя различные коды для одинаковых входных сигналов данных. Вторая подтаблица представляет собой таблицу, которая частично дублирована первой подтаблицей и составлена посредством назначения различных кодов для данных первых входных данных вторым входным данным первой подтаблицы. Первая и вторая подтаблицы составлены таким образом, что кодовые наборы дублированных частей принимают варианты изменений цифровой суммы, которые имеют противоположные знаки. Коды назначаются последовательно всем единичным таблицам в дублированных частях первой и второй таблиц относительно входных данных от кода, имеющего максимальное абсолютное значение варианта изменения цифровой суммы.

В соответствии с настоящим изобретением обеспечен также способ демодулирования сигналов, предназначенный для обратного преобразования кодовой последовательности на N- разрядной основе с целью вырабатывания информационной последовательности на М-разрядной основе, где M и N являются целыми числами, имеющими соотношение М<N, причем способ включает в себя: первый этап приема входной кодовой последовательности на N-разрядной основе; второй этап обратного преобразования N- разрядного входного кода в М-разрядные данные в соответствии с таблицей обратного преобразования и третий этап вывода информационной последовательности на М-разрядной основе в качестве результата демодуляции. Таблица обратного преобразования состоит из первой и второй подтаблиц, включающих в себя многочисленные кодовые группы, соответственно. Многочисленные кодовые группы имеют одинаковые выходные данные для различных входных кодов. Вторая подтаблица представляет собой таблицу, которая частично дублирована первой подтаблицей и создана посредством назначения различных входных кодов данным из первых выходных данных вторым выходным данным первой подтаблицы. Первая и вторая подтаблицы составлены таким образом, что кодовые наборы в дублированных частях принимают варианты изменений цифровой суммы, которые имеют противоположные знаки. Всем кодовым группам в дублированных частях первой и второй подтаблиц последовательно назначаются выходные данные от кода, имеющего максимальное абсолютное значение варианта изменения цифровой суммы.

В соответствии с настоящим изобретением обеспечено также устройство демодулирования сигналов, предназначенное для обратного преобразования кодовой последовательности на N-разрядной основе с целью вырабатывания информационной последовательности на M-разрядной основе, где М и N представляют собой целые числа, имеющие соотношение M<N, причем устройство включает в себя: принимающее средство, предназначенное для приема входной кодовой последовательности на N-разрядной основе; средство обратного преобразования, предназначенное для обратного преобразования N-разрядного входного кода в M-разрядные данные в соответствии с таблицей обратного преобразования, и выходное средство, предназначенное для вывода последовательности данных на M-разрядной основе в качестве результата демодуляции. Таблица обратного преобразования состоит из первой и второй подтаблиц, включающих в себя многочисленные группы, соответственно. Многочисленные кодовые группы имеют одинаковые выходные данные для различных входных кодов. Вторая подтаблица представляет собой таблицу, которая частично дублируется первой подтаблицей и создана посредством назначения различных входных кодов данным из первых выходных данных вторым выходным данным первой подтаблицы. Первая и вторая подтаблицы составлены таким образом, что кодовые наборы в дублированных частях принимают варианты изменений цифровой суммы, которые имеют противоположные знаки. Всем кодовым группам в дублированных частях первой и второй подтаблиц последовательно назначаются выходные данные от кода, имеющего максимальное абсолютное значение варианта изменения цифровой суммы.

В соответствии с настоящим изобретением обеспечен также способ модулирования сигналов, предназначенный для преобразования информационной последовательности на М-разрядной основе относительно заранее установленной таблицы преобразования в кодовую последовательность на N-разрядной основе, где М и N представляют собой целые числа, имеющие соотношение M<N, и для соединения N-разрядного кода со следующим N-разрядным кодом. Таблица преобразования создается посредством первого этапа выбора кодов, удовлетворяющих заранее установленным правилам модуляции из всех возможных комбинаций кодов на N-разрядной основе, второго этапа классифицирования выбранных кодов на многочисленные кодовые группы в соответствии с многочисленными различными кодовыми условиями, третьего этапа расчета вариантов изменений цифровой суммы кодов многочисленных кодовых групп; четвертого этапа последовательного расположения кодов от кода, имеющего более высокий вариант изменения цифровой суммы многочисленных кодовых групп; пятого этапа назначения расположенных в определенном порядке кодом М-разрядным данным от кода, имеющего больший вариант изменения цифровой суммы кодовых групп с целью вырабатывания первой подтаблицы, и шестого этапа назначения кодов, отличных от кодов, включенных в первую подтаблицу кодов, соответствующих заранее определенным правилам модуляции, первым данным для вторых данных всех данных от кода, имеющего большее абсолютное значение варианта изменения цифровой суммы, с целью вырабатывания второй подтаблицы, имеющей часть, дублированную первой подтаблицей.

В случае настоящего изобретения, так как в дублированных частях таблиц преобразования соответствующие кодовые наборы имеют вероятности изменений цифровой суммы (ИЦС), которые имеют противоположные знаки и близки друг к другу по абсолютному значению, управление изменением ИЦС можно добиться посредством выбора одной из дублированных частей без использования граничного двоичного разряда, используемого при обычной модуляции. Кроме того, поскольку используется таблица преобразования, в которой коды, имеющие более высокие абсолютные значения вариантов значений цифровой суммы, последовательно назначаются дублированной части, по существу, подавляются низкочастотные составляющие модулированных сигналов.

Краткое описание чертежей

Фиг. 1 представляет структуру кода обычного модулированного выходного сигнала.

Фиг. 2 представляет структуру кода подкодирования обычного модулированного выходного сигнала.

Фиг. 3 представляет обычные значения выборок и EFM- модулированную форму сигнала.

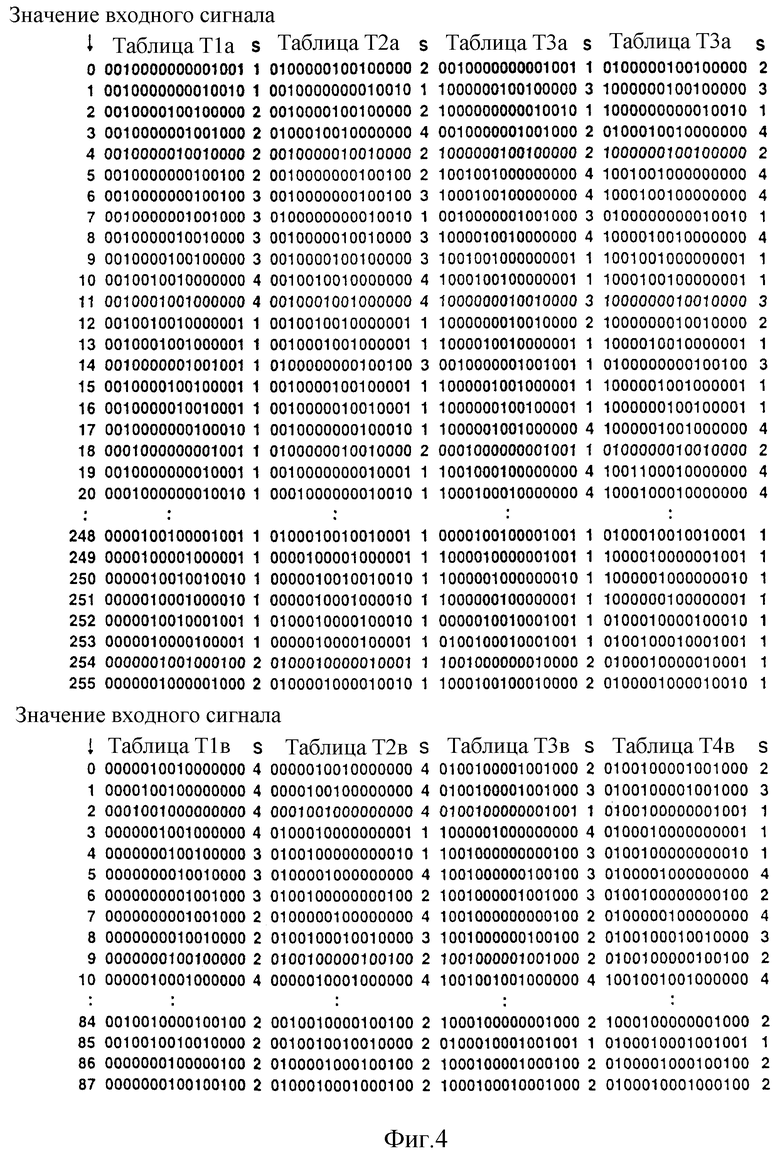

Фиг. 4 представляет пример таблицы преобразования, используемой в соответствующем настоящему изобретению варианте осуществления.

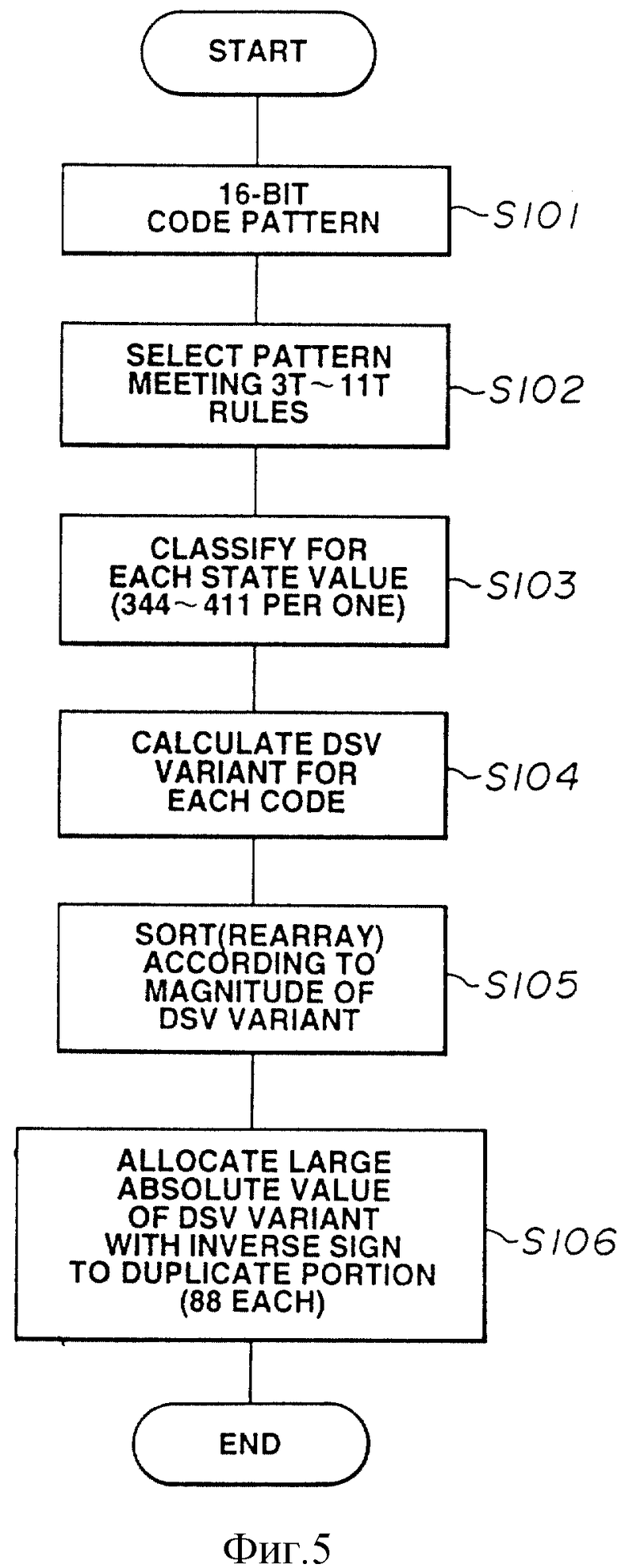

Фиг. 5 представляет блок-схему, иллюстрирующую пример алгоритма составления таблицы преобразования.

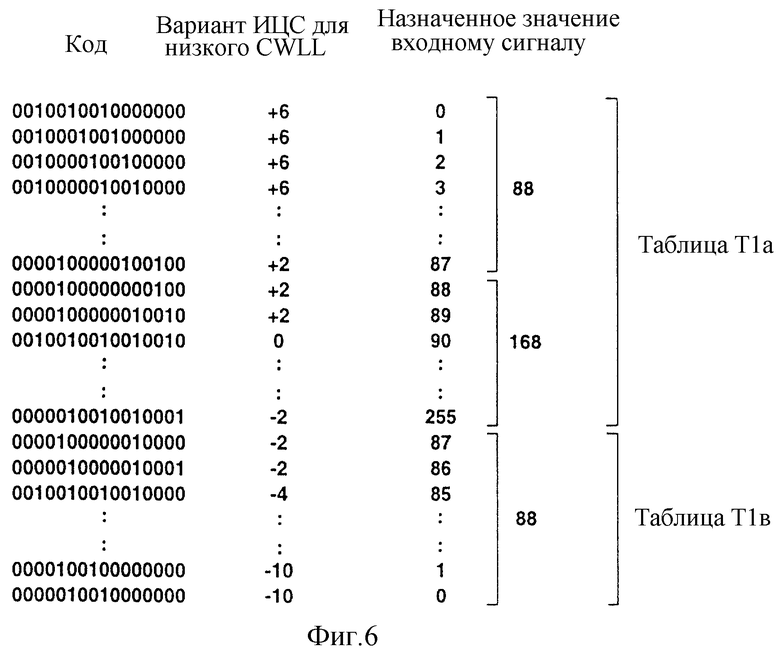

Фиг. 6 представляет пример единичной таблицы со значением переменной состояния, равным 1.

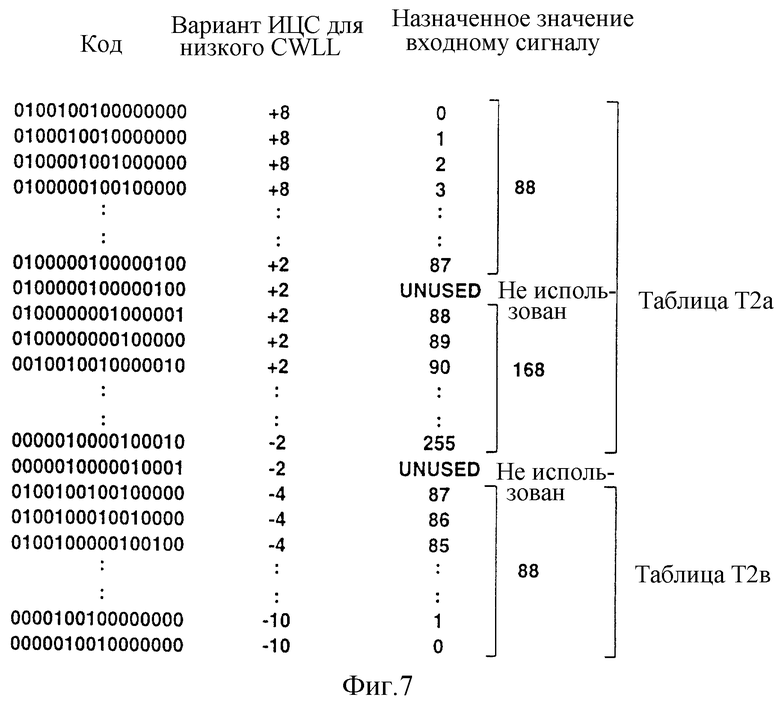

Фиг. 7 представляет пример единичной таблицы со значением переменной состояния, равным 2.

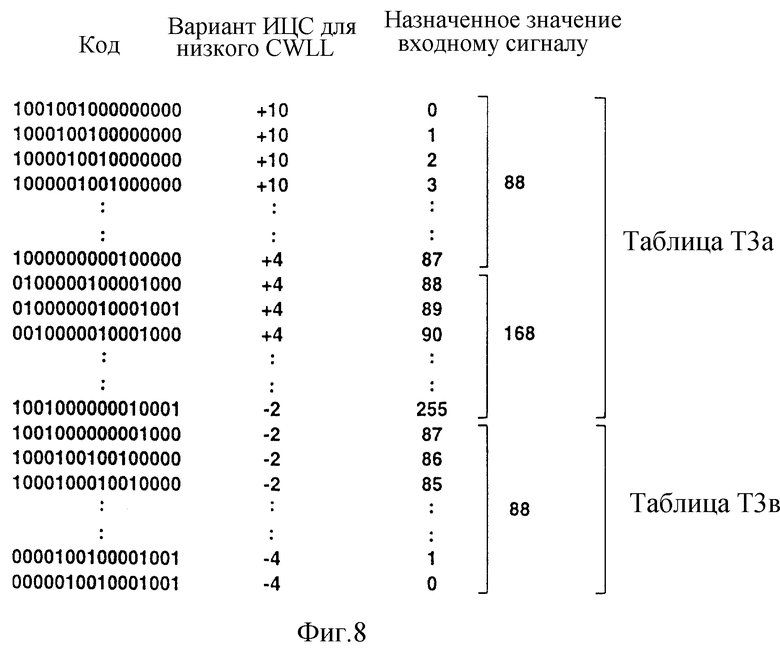

Фиг. 8 представляет пример единичной таблицы со значением переменной состояния, равным 3.

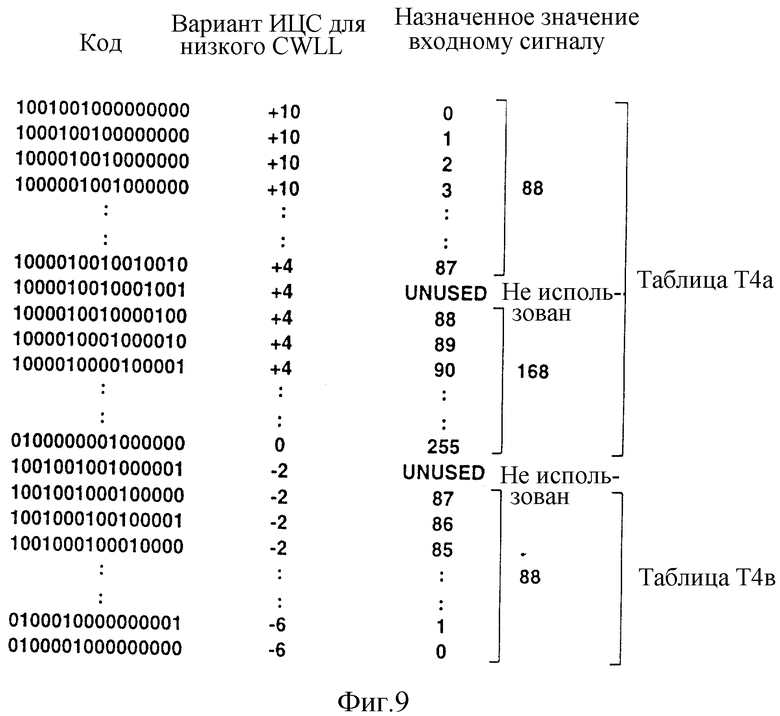

Фиг. 9 представляет пример единичной таблицы со значением переменной состояния, равным 4.

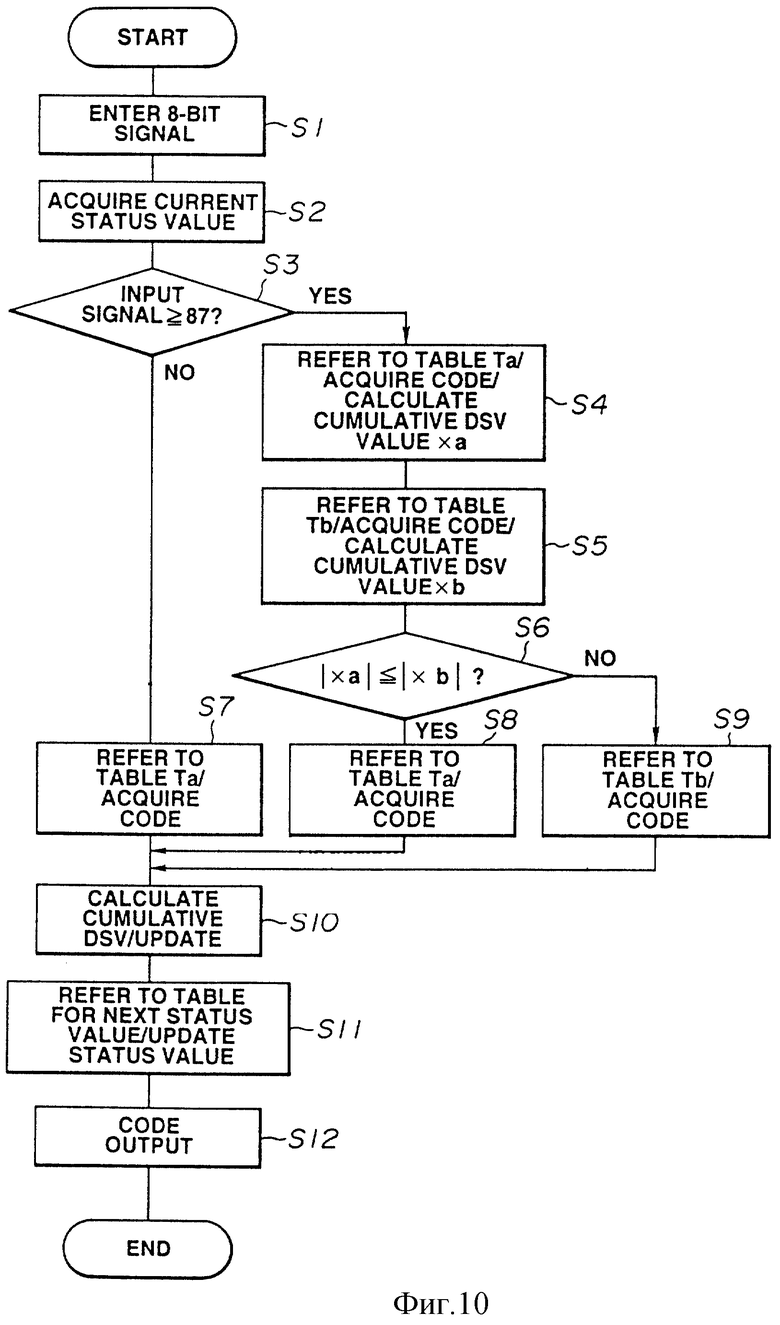

Фиг. 10 представляет блок-схему, иллюстрирующую пример алгоритма, используемого в настоящем изобретении способа модулирования сигналов.

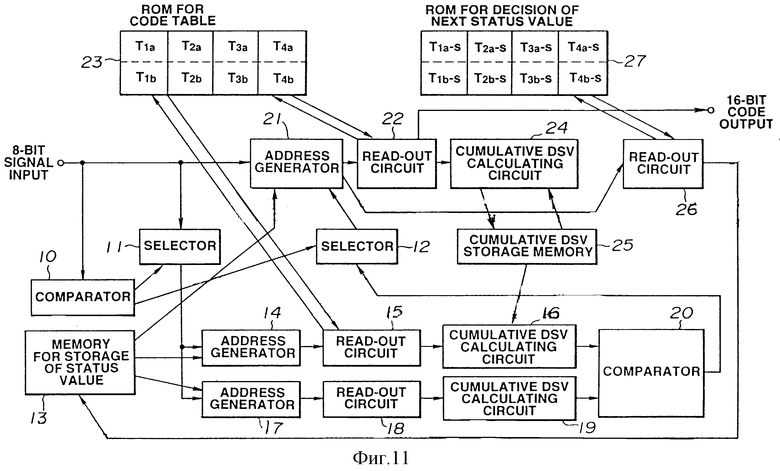

Фиг. 11 представляет блок-схему, изображающую иллюстративную структуру использующего настоящее изобретение устройства модулирования сигналов.

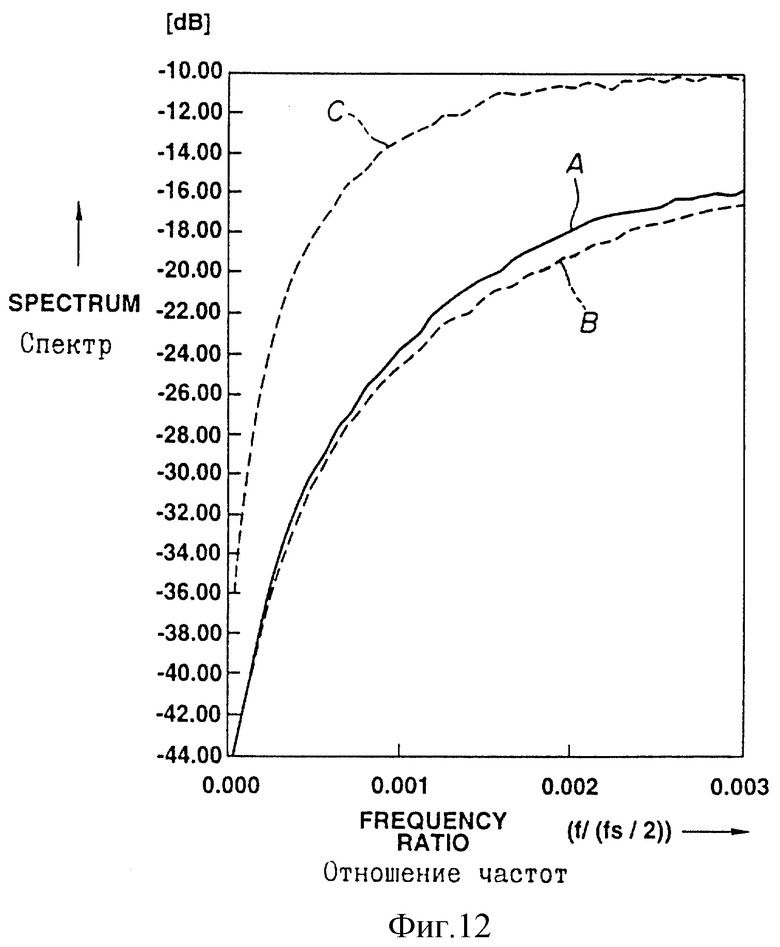

Фиг. 12 представляет график, иллюстрирующий, каким образом низкочастотные составляющие в модулированном сигнале можно уменьшить в соответствующем настоящему изобретению варианте осуществления по сравнению с обычной системой.

Фиг. 13 представляет блок-схему, иллюстрирующую пример алгоритма соответствующего настоящему изобретению варианта осуществления способа модулирования сигналов.

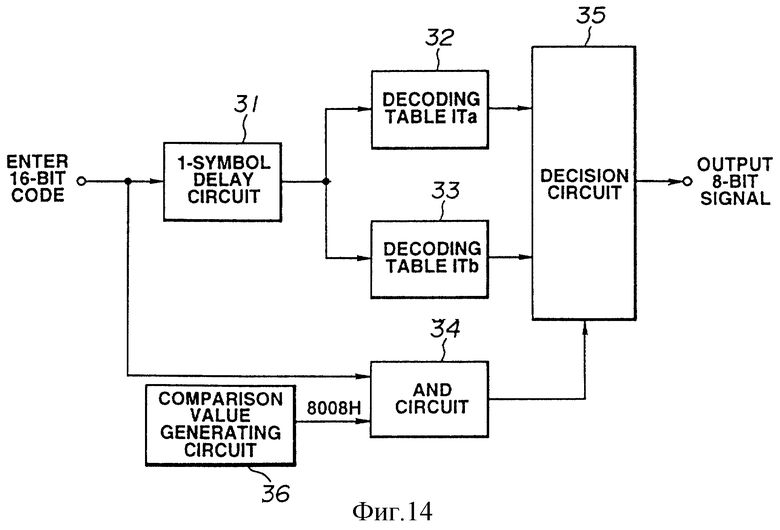

Фиг. 14 представляет блок-схему, изображающую структуру использующего настоящее изобретение устройства демодулирования сигнала.

Лучший способ выполнения изобретения

Теперь будет приведено описание со ссылкой на чертежи предпочтительных вариантов осуществления способа модулирования сигналов, устройства модулирования сигналов, способа демодулирования сигналов и устройства демодулирования сигналов.

На соответствующие настоящему изобретению способ модулирования сигналов и устройство модулирования сигналов влияет предположение преобразования входной информационной последовательности на M- разрядной основе в кодовую последовательность на N-разрядной основе, где М и N являются целыми числами, находящимися в соотношении М<N, и соединения N-разрядного кода со следующим N-разрядным кодом. Таблица преобразования, предназначенная для преобразования информационной последовательности на М-разрядной основе в вышеупомянутую кодовую последовательность на N-разрядной основе, частично дублируется.

Дублированные части конфигурируют таким образом, что варианты изменения цифровой суммы (значения цифровой суммы) кодов каждого из двух взаимно связанных кодовых наборов имеют противоположные знаки и близкие друг к другу по абсолютному значению.

Пример таблицы преобразования показан на фиг. 4.

Таблица преобразования составлена из множества, например из четырех различных типов единичных таблиц Т1, Т2, Т3 и Т4, где каждая единичная таблица имеет дублированную часть, как показано на фиг. 4. То есть, если таблица наборов кодов (комбинаций канальных двоичных разрядов) для совокупности значений входных сигналов для единичной таблицы обозначена позицией Тa, часть ее удваивается с целью образования таблицы Тb. В случае показанного на фиг. 4 иллюстративного примера удвоены 88 кодов со значениями входных сигналов от 0 до 87. В настоящем описании таблица Тa и таблица Тb представляют таблицу передней стороны и таблицу задней стороны, соответственно.

Таким образом, в случае показанного на фиг. 4 примера, таблица преобразования состоит из четырех сортов таблиц T1a, Т2a, T3a, Т4a для 256 16-разрядных кодов или 256 16-канальных комбинаций двоичных разрядов, связанных со значениями 8-разрядных входных сигналов от 0 до 255, составляющих таблицу передней стороны, и четырех таблиц Т1b, Т2b, Т3b, Т4b, которые удваиваются для 88 16-канальных комбинаций двоичных разрядов таблиц Т1a, Т2a, Т3a, Т4a, имеющих значения входных сигналов от 0 до 87, составляющих таблицу задней стороны. В настоящем варианте осуществления удвоенные части таблицы преобразования, которая представляет собой 16-разрядные коды для значений входных сигналов от 0 до 87 таблиц Т1a, Т2a, Т3a, Т4a и 16-разрядные коды для значений входных сигналов от 0 до 87 таблиц Т1b, Т2b, Т3b, Т4b, конфигурируют так, что варианты значения или изменения цифровой суммы связанных кодовых наборов имеют противоположную полярность и близкие по величине друг другу.

Ниже приводится описание варианта осуществления способа модулирования сигналов с использованием показанной на фиг. 4 таблицы преобразования.

Как показано на фиг. 4, в случае настоящего варианта осуществления, входной 8-разрядный сигнал (данные) преобразуется в 16-разрядный код. В обычной системе EFH входной 8-разрядный сигнал преобразуется в 14- разрядную комбинацию информационных двоичных разрядов, которая соединяется с соседней 14-разрядной комбинацией информационных двоичных разрядов через 3-разрядные объединяющие разряды. В настоящей системе 8-разрядный входной сигнал непосредственно преобразуется в 16-разрядный код без использования объединяющих разрядов. Настоящая система модуляции далее называется системой модуляции 8-16. Модуляция 8-16 также удовлетворяет условию EFM, состоящему в том, что количество "0"-й между "1" и "1" должно быть не менее 2 и не более 10, то есть правилу 3Т-11Т.

При модуляции EFM для преобразования входного 8-разрядного сигнала в 14- разрядный код обеспечивают только одну таблицу. В случае модуляции 8-16 для преобразования входного 8-разрядного сигнала в 16- разрядный код обеспечивают многочисленные сорта таблиц. В показанном на фиг. 4 варианте использованы четыре сорта единичных таблиц Т1, Т2 T3 и Т4.

Далее приводится пояснение "значений переменной состояния", используемых при классификации единичных таблиц.

Значения переменной состояния играют роль указателей, предназначенных для определения, которую из таблиц преобразования необходимо использовать при преобразовании входного 8-разрядного сигнала (данных) в 16-разрядный код. Таким образом, типы значений переменной состояния равны сорту различных сортов единичных таблиц таблицы преобразования. То есть, в настоящем варианте имеются четыре типа значений переменной состояния [1] - [4], связанных с четырьмя сортами единичных таблиц Т1, Т2, Т3 и Т4.

Значения переменной состояния испытывают переход каждый раз, когда происходит преобразование 8-разрядного символа в 16-разрядный код. Если 16-разрядный код оканчивается "1" или "10", то значение переменной состояния осуществляет переход к [1]. Если 16- разрядный код оканчивается не менее чем 2 и не более чем 5 последовательными "0"-и, то значение переменной состояния осуществляет переход к [2] или [3]. Если 16-разрядный код оканчивается не менее чем 6 и не более чем 9 последовательными "0"-и, значение переменной состояния претерпевает переход к [4]. Если кодом, подвергающимся переходу к значению переменной состояния [2], и кодом, подвергающимся переходу к значению переменной состояния [3], можно управлять как совершенно различными кодами, то при создании таблицы можно произвольно определять, представляет ли значение переменной состояния [2] или [3].

Таблица преобразования, предназначенная для преобразования входного 8-разрядного сигнала в 16-разрядный код, имеет следующие характеристики.

Единичная таблица T1, используемая, когда значение переменной состояния представляет [1] , составляется из 16-разрядных кодов, начинающихся по меньшей мере с двух "0"-й, с целью удовлетворения такому условию, что количество "0"-й между "1" и "1" должно быть не менее 2 и не более 10 (правило 3Т-11Т). Причина состоит в том, что 16-разрядный код, модулированный до перехода значения переменной состояния к [1], оканчивается "1" или "10".

По той же причине единичные таблицы Т2 или Т3, используемые для значений переменной состояния [2] или [3] соответственно, составлены из 16-разрядных кодов, начинающихся с 0-5 последовательных "0"-й. Следует отметить, что единичная таблица Т2, используемая для значения переменной состояния, равного [2] , составлена из кодов, имеющих и первый разряд и 13-й разряд (то есть четвертый разряд от самого младшего двоичного разряда), равные "0", где самый старший двоичный разряд представляет первый разряд, в то же время единичная таблица Т3, используемая для значения переменной состояния, равного [3] , составлена из кодов, имеющих один или оба из первого двоичного разряда и 13-го двоичного разряда (четвертый разряд от самого младшего двоичного разряда) равными "1", причем самым старшим двоичным разрядом и здесь является первый разряд.

Единичная таблица 4, используемая, когда значение переменной состояния равно [4], составлена из 16-разрядных кодов, начинающихся с "1" или с "01".

Здесь существуют 16-разрядные коды, которые можно использовать совместно для двух различных значений переменной состояния. Например, 16-разрядный код, начинающийся с трех последовательных "0"-й и имеющий первый и 13-й двоичные разряды, равными "0", можно использовать как со значением переменной состояния, равным [1], так и со значением переменной состояния, равным [2] . Чтобы предотвратить возможность путаницы во время декодирования, таблицу необходимо конфигурировать так, чтобы коды различных значений переменной состояния связывались с одним и тем же входным значением (данными) 8-разрядных сигналов.

С другой стороны, 16-разрядный код такого типа, в котором значение переменной состояния впоследствии подвергается переходу к [2] или [3], можно связывать с двумя полностью отличающимися сортами входных 8-разрядных сигналов. Хотя сам по себе 16-разрядный код нельзя однозначно декодировать, его можно правильно декодировать посредством неизбежной установки следующего появляющегося значения переменной состояния [2] или [3]. Ниже приводится объяснение этого способа.

Здесь обеспечена другая таблица, предназначенная для индикации соответственных кодов единичных таблиц, к которому из [1] - [4] переходят следующие значения переменной состояния, когда входные 8-разрядные сигналы преобразуются в коды. Если 16- разрядные коды оканчиваются не менее чем 2 и не более чем 5 последовательными "0"-и, невозможно посредством только свойств кода определить, переходят ли значения переменной состояния далее к [2] или [3] . Однако следующие значения переменной состояния можно однозначно определить посредством наличия ссылки на эту таблицу. Между тем, после комбинации синхронизации необходимо значение переменной состояния [1].

В показанном на фиг. 4 примере следующее значение переменной состояния показано буквой S, предназначенной для составления таблицы, состоящей из значений переменной состояния S, указывающих направление перехода.

Используя вышеприведенные таблицы, модулятор модулирует 8-разрядные входные символы в 16- разрядные коды. Текущие значения переменной состояния запоминаются во внутренней памяти, и по значениям переменной состояния идентифицируется таблица, на которую необходимо ссылаться, 8- разрядные входные сигналы преобразуются таблицей посредством осуществления модуляции. Одновременно из таблицы определяются и удерживаются в памяти следующие значения переменной состояния, так что будет идентифицирована таблица, подлежащая использованию во время следующего преобразования. Ниже приводится объяснение практической конфигурации аппаратного средства.

Управление изменением цифровой суммы или значением цифровой суммы (ИЦС) производится следующим образом:

Производится проверка для каждого значения переменной состояния, сколько здесь существует 16- разрядных кодов, которые удовлетворяют ограничениям длины прогона (правило 3Т- 11Т) и можно удовлетворительно использовать. Для противодействия появлению двух повторяющихся комбинаций 11Т, которые такие же, как и комбинация кадровой синхронизации, предварительно исключается такой 16-разрядный код, в котором располагаются десять "0", за которыми следует "1", за которой, в свою очередь, следует пять "0"-й. Причина состоит в том, что если код соединить с 16-разрядной кодовой комбинацией, начинающейся с пяти последовательных "0"-й, создаются две повторяющиеся комбинации 11Т. Если после преобразования в 16-разрядный код значение переменной состояния подвергается переходу к [2] или [3], код можно использовать двумя способами, так что эти коды подсчитываются дважды.

Результаты расчетов показывают, что 344 16-разрядных кодов можно использовать со значением переменной состояния [1], 345 16- разрядных кодов можно использовать со значением переменной состояния [2], 344 16-разрядных кодов можно использовать со значением переменной состояния [3] и 411 16-разрядных кодов можно использовать со значением переменной состояния [4]. Поскольку входной сигнал представляет собой 8-разрядный сигнал, достаточно 256 кодов, так что имеются по меньшей мере 88 избыточных кодов для соответствующих значений переменной состояния. Эти 88 избыточных кодов используются для целей управления ИЦС. То есть, используя эти избыточные коды, отдельно обеспечивается таблица с количеством из 88 компонентов в качестве таблицы задней стороны. Эта таблица задней стороны обеспечена в настоящем варианте осуществления для входных 8-разрядных сигналов от "0" до "87".

Для достижения эффективного управления изменением ИЦС в случае настоящей системы управления ИЦС, таблицы передней стороны и задней стороны составляются по следующему принципу.

Здесь имеются 16-разрядные коды, которые могут использовать совместно два различных значения переменной состояния, как описано выше. Поскольку таблицу необходимо создавать таким образом, чтобы все время одинаковые входные значения (данные) 8-разрядных сигналов связывались с этим кодом, способы создания таблиц в этом случае усложняются из-за этих ограничений. Поскольку здесь предполагается показать способ создания таблицы с целью эффективного управления ИЦС, последующее описание производится при предположении, что соответственные значения переменной состояния принимаются независимо, а 16- разрядные коды, которые можно использовать для соответственных значений переменной состояния, можно свободно назначать соответственным значениям входных 8-разрядных сигналов.

Показанная на фиг. 5 блок-схема предназначена для иллюстрирования способа создания вышеупомянутой таблицы преобразования, более конкретного способа создания необязательного одного из четырех сортов единичных таблиц таблицы преобразования.

На фиг. 5 показано, что на этапе S101 определяется совокупность комбинаций 16-разрядных кодов. На следующем этапе S102 выбираются комбинации или коды двоичных разрядов, которые удовлетворяют условию ограничения длины прогона (3Т-11Т). На следующем этапе S103 коды классифицируются на коды, которые следуют вышеупомянутым условиям, основанным на значении переменной состояния. Количество 16-разрядных кодов, которые можно использовать для этих значений переменной состояния, составляет 344-411, как это объяснялось выше. Например, количество 16- разрядных кодов, которые можно использовать для значения переменной состояния [1], равно 344.

На следующем этапе S104 рассчитывается величина изменения ИЦС для являющегося низким уровня, непосредственно предшествующего каждому коду (равного CWLL), для каждого кода каждого значения переменной состояния. Поскольку длина кода составляет 16 двоичных разрядов, а величина изменения ИЦС на код составляет -10 у минимума и +10 у максимума, то если, например, значение переменной состояния равно [1], тогда величина изменения ИЦС составляет -10 у минимума и +6 у максимума.

На следующем этапе S105 последовательно располагаются, посредством осуществления классификации, 344 16-разрядных кодов, имеющих значение переменной состояния, равное [1], начиная с кода, имеющего более высокий вариант ИЦС на положительной стороне, до кода, имеющего более высокий вариант изменения ИЦС на отрицательной стороне.

На следующем этапе S106 выбираются 88 16-разрядных кодов в порядке уменьшения величины изменения ИЦС на положительной стороне и последовательно назначаются "0" -"87" 8- разрядным входным сигналам в показанной на фиг. 6 таблице T1a передней стороны для значения переменной состояния [1]. Чем больше абсолютное значение изменения ИЦС выбранных 88 16-разрядных кодов, тем меньшим оказывается значение входного 8-разрядного сигнала, которому назначается 16-разрядный код. С другой стороны, 88 16-разрядных кодов выбираются в порядке уменьшения величины изменения ИЦС на отрицательной стороне и последовательно назначаются "0"-"87" 8-разрядным входным сигналам в показанной на фиг. 6 таблице задней стороны Т1b, чем больше абсолютное значение изменения ИЦС выбранных 88 16-разрядных кодов, тем меньше значение входного 8-разрядного сигнала, которому назначается 16-разрядный код. И наконец, выбираются 168 16-разрядных кодов в порядке маленького абсолютного значения изменения ИЦС и назначаются "88- 255" 8-разрядным входным сигналам в показанной на фиг. 6 таблице передней стороны Т1a.

Если значение переменной состояния равно [1], то количество 16-разрядных кодов, которые можно использовать, составляет 344, так что совокупность кодов, которые можно использовать, можно выбрать на этом этапе, как показано на фиг. 6.

На фиг. 7, 8 и 9 показаны примеры распределения значений входных сигналов в единичных таблицах таблицы преобразования, которые используются для значений переменной состояния [2], [3] и [4], соответственно.

На фиг. 6 - 9 последовательность 16-разрядных сигналов, имеющих одинаковую величину изменения ИЦС, изменяется во время классификации относительно последовательности, приведенной в примере на фиг. 4. Однако любую из этих таблиц можно использовать без какого-либо затруднения.

Если таблицы передней стороны и задней стороны Тa, Тb создаются на вышеописанном принципе, то можно выбирать один из двух 16-разрядных кодов с противоположными знаками и с более высоким абсолютным значением варианта ИЦС для входного 8- разрядного сигнала, имеющего значение между "0" и "87", позволяя тем самым осуществлять эффективное управление ИЦС. Если входной 8- разрядный сигнал имеет значение между "88" и "255", то 16- разрядные коды уникально комплектуются так, что нельзя выполнять управление ИЦС. Однако поскольку эти 16-разрядные коды имеют более низкое абсолютное значение варианта ИЦС, становится возможным все время поддерживать более низкое абсолютное значение накопленного ИЦС.

Таблица задней стороны Тb с 88 элементами, определяемыми, как описано выше, имеет такие же характеристики, как характеристики таблицы передней стороны Тa с 256 элементами, за исключением того, что количество элементов маленькое.

Управление ИЦС выполняется, используя таблицу передней стороны Тa и таблицу задней стороны Тb. Если входной 8-разрядный сигнал имеет значение между "0" и "87", то можно адаптивно выбирать, которую из таблиц передней стороны Та или задней стороны Тb необходимо использовать во время преобразования входного 8-разрядного сигнала в 16-разрядный код. Таким образом, в случае настоящего варианта осуществления, все время рассчитывается накопленное ИЦС, рассчитывается накопленное ИЦС в случае, если преобразование выполняется с использованием таблицы передней стороны Тa, и накопленное ИЦС в случае, если преобразование выполняется с использованием таблицы задней стороны Тb, и для выполнения преобразования выбирается одна из таблиц, в которой уменьшается абсолютное значение накопленной ИЦС ближе к нулю.

На фиг. 10 приведено пояснение алгоритма соответствующей настоящему варианту осуществления системы модулирования сигнала, в котором используется вышеописанная таблица преобразования.

Когда на этапе S1 вводится 8-разрядный сигнал (данные), на этапе S2 получается текущее значение переменной состояния. Затем на этапе S3 производится проверка, больше ли 87-го 8-разрядный входной сигнал или нет.

Если на этапе S3 принято решение ДА, то есть, если обнаружено, что значение входного сигнала соответствует 87 или меньше, программа переходит к этапу S4, чтобы обратиться к таблице передней стороны Тa, чувствительной к текущему значению переменной состояния с целью получения 16-разрядного кода, соответствующего значению входного сигнала, и рассчитывать накопленное значение ИЦС ха. На следующем этапе S5 осуществляется обращение к таблице обратной стороны Тb, чувствительной к текущему значению переменной состояния, чтобы получить 16-разрядный код, соответствующий значению входного сигнала, и рассчитать накопленное значение ИЦС xb. На следующем этапе S6 определяется, находятся ли накопленные значения ИЦС ха и xb в соотношении  или нет.

или нет.

Если результатом принятия решения на этапе S3 является НЕТ, то есть если определено, что входной сигнал больше 87, программа переходит к этапу S7, чтобы обратиться к таблице передней стороны Тa, чувствительной к текущему значению переменной состояния, с целью получения 16-разрядного кода, соответствующего значению входного сигнала, до перехода программы к этапу S10. Если результатом принятия решения на этапе S6 является ДА, то есть если  происходит обращение к таблице передней стороны Тa, чтобы получить 16-разрядный код до перехода программы к этапу S10. Если результатом принятия решения на этапе S6 является НЕТ, то есть если абсолютное значение накопленной величины ИЦС xb таблицы задней стороны Тb окажется маленьким, происходит обращение к таблице задней стороны Тb, чтобы получить 16-разрядный код до перехода программы к этапу S10.

происходит обращение к таблице передней стороны Тa, чтобы получить 16-разрядный код до перехода программы к этапу S10. Если результатом принятия решения на этапе S6 является НЕТ, то есть если абсолютное значение накопленной величины ИЦС xb таблицы задней стороны Тb окажется маленьким, происходит обращение к таблице задней стороны Тb, чтобы получить 16-разрядный код до перехода программы к этапу S10.

На этапе S10 рассчитывается и корректируется накопленное ИЦС. На этапе S11 производится обращение к таблице

для следующего значения переменной состояния, то есть к таблице, совместно показывающей следующее значение переменной состояния S фиг. 4, чтобы откорректировать значение переменной состояния. На следующем этапе S12 выводится полученный 16- разрядный код.

На фиг. 11 показана в виде блок-схемы типичная структура устройства модулирования сигнала, предназначенного для реализации воплощающей настоящее изобретение системы модулирования сигналов.

На фиг. 11 8-разрядный входной сигнал поступает в схему компаратора 10 и схему генерирования адреса 21.

Компаратор 10 сравнивает входной 8-разрядный сигнал со значением "88". Если значение 8-разрядного входного сигнала меньше "88", становится осуществимой вышеупомянутое управление ИЦС. Таким образом, компаратор 10 подает команды на селекторы 11 и 12 ввести режим управления ИЦС.

Если компаратором 10 подана команда на ввод режима управления ИЦС, селектор 11 передает 8-разрядный входной сигнал на генераторы адресов 14 и 17. Если 8-разрядный входной сигнал не менее "88", то компаратор 10 подает команду на действие, соответствующее тому, что управление ИЦС оказывается неосуществимым и не выполняется. Таким образом, входной 8- разрядный сигнал не подается на адресные генераторы.

Запоминающее устройство 13 значений переменной состояния представляет собой запоминающее устройство, предназначенное для хранения текущего значения переменной состояния от [1] до [4].

Запоминающее устройство 25 накопленного ИЦС представляет собой память для хранения текущего значения накопленного изменения ИЦС.

Постоянное запоминающее устройство (ПЗУ) 23 таблицы преобразования для 16-разрядных кодов представляет собой ПЗУ таблицы для хранения 16-разрядных кодов, в которые следует преобразовывать 8-разрядные значения входных сигналов. Имеются четыре единичных таблицы Т1, Т2, Т3 и Т4, связанные с соответственными значениями переменной состояния. Кроме того, поскольку речь идет о значениях входных сигналов "0" - "87", 16-разрядные коды дублируются, так что здесь присутствуют коды, включенные в таблицу передней стороны Тa, и коды, включенные в таблицу задней стороны Тb. Таким образом, существуют восемь сортов таблиц Т1a - Т4b. Используя эти таблицы Т1a - Т4b, оказывается возможным принимать адрес, который определяется из трех параметров, то есть из 8- разрядного входного сигнала, значения переменной состояния и значения, показывающего, следует ли использовать таблицу передней стороны или таблицу задней стороны, и найти соответственный 16- разрядный код.

ПЗУ 27 таблицы принятия решения о следующем значении переменной состояния представляет собой ПЗУ таблицы, предназначенное для запоминания следующего значения переменной состояния, которое преобладает после преобразования значения 8-разрядного входного сигнала в 16-разрядный код. Имеются четыре таблицы для соответственных значений переменной состояния, тогда как, поскольку речь идет о значениях входных сигналов от "0" до "87", таблицы удваиваются, так что дополнительно к таблице передней стороны имеется таблица задней стороны. То есть, таблицы принятия решения о следующем значении переменной состояния Т1a-S, Т1b-S, T2a-S, T2b-S, T3a-S, T3b-S, T4a-S, Т4b-S связаны с кодовыми таблицами Т1a, Т1b, Т2a, Т2b, Т3a, Т3b, Т4a и Т4b, соответственно. Эти таблицы Т1a-S, Т4b-S принимают адреса, определяемые по трем параметрам, а именно по значению 8- разрядных входных сигналов, текущему значению переменной состояния и значению, показывающему, подлежит ли использованию таблица передней стороны или таблица задней стороны, и определяют связанное следующее значение переменной состояния.

Схема 14 генерирования адреса принимает 8-разрядный входной сигнал и текущее значение переменной состояния, поступающее из запоминающего устройства 13 хранения значений переменной состояния, чтобы выработать адрес, предназначенный для получения из ПЗУ 23 таблицы 16-разрядных кодов, адрес, предназначенный для получения 16-разрядного кода в случае использования таблицы Тa (далее называемой первой таблицей), с целью передачи адреса в схему считывания 15.

Схема считывания 15 принимает адресный сигнал из схемы генерирования адреса 14 и, используя адресный сигнал, получает 16-разрядный код из ПЗУ 23 таблицы 16-разрядных кодов. Этот код передается в схему 16 вычисления накопленного изменения ИЦС.

Схема 16 расчета накопленного ИЦС производит расчет по 16-разрядному коду, принятому из схемы считывания 15, и по текущему значению накопленного ИЦС, полученному из запоминающего устройства 25 запоминания накопленного ИЦС, значение накопленной ИЦС, получающееся от использования 16-разрядного кода, и передает рассчитанное значение накопленного ИЦС в схему компаратора 20.

В схему 17 генерирования адреса поступает 8-разрядный входной сигнал и текущее значение переменной состояния из запоминающего устройства 13 хранения значений переменной состояния. Схема 17 генерирования адреса вырабатывает также адрес, получающийся от использования второй таблицы из ПЗУ 23 таблицы 16- разрядных кодов, и маршрутизирует адрес в схему считывания 18.

На схему считывания 18 поступает сигнал адреса со схемы 17 вырабатывания адреса, и, используя сигнал адреса, схема 18 вырабатывает 16-разрядный код из ПЗУ 23 таблицы 16-разрядных кодов. Этот код маршрутизируется в схему 19 расчета накопленного изменения ИЦС.

Схема 19 расчета накопленного ИЦС рассчитывает по 16- разрядному коду, принятому из схемы считывания 18, и значению текущего ИЦС, принятому из запоминающего устройства 25 хранения накопленного изменения ИЦС, значение накопленного ИЦС, получающегося от использования 16-разрядного кода, и передает рассчитанное значение в схему компаратора 20.

На компаратор поступает из схемы 16 расчета накопленного ИЦС и схемы 19 расчета накопленного ИЦС значение накопленного ИЦС в случае осуществления преобразования с использованием первой таблицы и значение накопленного ИЦС в случае осуществления преобразования с использованием второй таблицы, и сравнивает соответствующие абсолютные значения друг с другом. Определяется, которая из таблиц дает меньшее абсолютное значение накопленного ИЦС, и сигнал, показывающий, которую таблицу следует использовать, передается на селектор 12.

Если компаратор 10 подает команду ввести режим изменения ИЦС, селектор 12 маршрутизирует сигнал, показывающий, какую из таблиц, первую или вторую, следует использовать, на генератор адреса 21. Если компаратор 10 подает команду не выполнять управление ИЦС, с селектора 12 подается сигнал на генератор адреса 21, предназначенный для подачи команды на генератор адреса 21, в любом случае использовать первую таблицу.

Используя значение 8- разрядного входного сигнала, текущее значение переменной состояния, принятое из запоминающего устройства 13 хранения значения переменной состояния, и сигнал с селектора 12, показывающий, какую следует использовать таблицу, первую или вторую, генератор адреса 21 вырабатывает адрес, предназначенный для получения 16-разрядного кода из ПЗУ 23 таблицы 16-разрядных кодов, и адрес, предназначенный для получения следующего значения переменной состояния из ПЗУ таблицы принятия решения о следующем значении переменной состояния, и передает адрес в схемы считывания 22 и 26.

На схему считывания 22 поступает сигнал с генератора адреса 21, и, используя сигнал адреса, эта схема получает 16-разрядный код из ПЗУ 23 таблицы 16-разрядных кодов. Этот код представляет собой выходной 16-разрядный код, который поступает с настоящего модулятора. Со схемы считывания 22 поступает также 16-разрядный код на схему 24 расчета накопленного ИЦС.

Схема 24 расчета накопленного ИЦС рассчитывает для 16- разрядного кода, принятого со схемы считывания 22, и накопленного ИЦС, принятого из запоминающего устройства 25 хранения накопленного ИЦС, значение накопленного ИЦС, которое преобладает после использования 16-разрядного кода, и корректирует содержимое запоминающего устройства 25 хранения накопленного ИЦС рассчитанным значением.

На схему считывания 26 поступает сигнал адреса со схемы генерирования адреса 21, и, используя сигнал адреса, эта схема получает следующее значение переменной состояния из ПЗУ 27 таблицы принятия решения о следующем значении переменной состояния. Со схемы считывания 26 следующее значение переменной состояния поступает на запоминающее устройство 13 хранения значения переменной состояния для корректирования в нем содержимого.

На фиг. 12 кривая А иллюстрирует низкочастотные составляющие, определяемые преобразованием Фурье, формы сигнала записи, создаваемой при модулировании входных 8-разрядных сигналов выборки, используя вышеописанные соответствующие настоящему изобретению способ и устройство модулирования сигналов.

С другой стороны, кривая В на фиг. 12 показывает низкочастотные составляющие формы сигнала записи, создаваемые при модулировании тех же сигналов выборок, используя EFM и преобразование Фурье, вырабатываемой формы сигнала записи, тогда как кривая С на фиг. 12 показывает низкочастотные составляющие формы сигнала записи, создаваемые при модулировании тех же сигналов выборок, и используя систему, соответствующую обычной системе EFM, имеющей два объединяющих разряда, и преобразование Фурье созданной формы сигнала записи.

Из кривых А, В и С фиг. 12 видно, что в случае воплощения настоящего изобретения, низкочастотные составляющие можно уменьшить до уровня, по существу равного уровню, достигаемому обычной системой EFM, несмотря на то, что эффективность модуляции эквивалентна эффективности обычной системы EFM с двумя объединяющими разрядами, то есть в 17/16 раза выше эффективности модуляции обычной системы EFM.

Теперь будет приведено объяснение способа приема сигнала, модулированного соответствующей настоящему изобретению системой модулирования, и демодулирования принятых сигналов в исходный 8- разрядный сигнал.

В случае обычной системы EFM, в которой 14- разрядные информационные двоичные разряды связываются с 8- разрядным входным сигналом в полном однозначном отношении, обратное преобразование из 14-разрядных информационных двоичных разрядов в 8-разрядные сигналы можно получить без какого-либо неудобства.

В случае соответствующего настоящему изобретению варианта осуществления, имеются случаи, когда одинаковые 16-разрядные сигналы назначаются различным 8-разрядным входным сигналам, так что демодулятор не может произвести обратное преобразование просто при приеме 16-разрядных кодов. Таким образом, если соответствующий настоящему изобретению демодулятор не может осуществить обратное преобразование при приеме 16- разрядного кода, он принимает другой следующий символ, то есть другой последующий 16-разрядный код, чтобы осуществить обратное преобразование на основании двух символов. На фиг. 13 показан алгоритм соответствующей настоящему изобретению системы демодулирования.

Теперь будет приведено пояснение показанного на фиг. 13 итога алгоритма демодулирования.

16-разрядный код, который можно назначить совместно двум совершенно различным значениям входных 8-разрядных значений, непременно ограничивается кодом, в котором значение переменной состояния следующий раз изменяется к [2] или [3] , как объяснялось выше. Кроме того, если значение переменной состояния, к которому затем переходит один из таких 16- разрядных кодов, представляет [2], значение переменной состояния, к которому затем переходит другой из 16-разрядных кодов, непременно представляет [3]. Используемая для значения переменной состояния [2] таблица составляется из кодов, каждый из которых имеет первый разряд и 13-й разряд, равные 0, где самым старшим разрядом является первый разряд, тогда как таблица, используемая для значения переменной состояния [3], состоит из кодов, каждый из которых имеет один или оба из первого разряда и 13-го разряда, равные 1, где самым старшим двоичным разрядом является первый разряд.

Из этих условий вытекает, что если значение переменной состояния подлежащего обратному преобразованию 16-разрядного кода переходит к [2], последующий 16-разрядный код имеет первый разряд и 13-й разряд равными 0, тогда как, если значение переменной состояния подлежащего обратному преобразованию 16-разрядного кода переходит к [3], последующий 16-разрядный код имеет один или оба первый разряд и 13-й разряд равными 1. Таким образом, если демодулятор при приеме 16-разрядного кода не способен осуществлять обратное преобразование, он принимает другой последующий символ (16-разрядный код) на этапе S25 фиг. 13 с целью проверки первого и 13-го разрядов на этапе S26. Таким образом, на этапе S27 производится проверка, оба ли эти двоичные разряды представляют "0". Если результатом проверки на этапе S27 является ДА, то есть, если оба двоичных разряда представляют "0", подлежащий обратному преобразованию 16-разрядный код представляет собой код, значение переменной состояния которого далее переходит к [2]. Если результатом проверки на этапе S27 является НЕТ, то есть, если один или оба из этих двоичных разрядов представляют "1", подлежащий обратному преобразованию 16-разрядный код представляет собой код, значение переменной состояния которого далее переходит к [3]. Это позволяет однозначно осуществлять обратное преобразование.

Используя иллюстрированный пример, произведем объяснение этой операции путем ссылки на представленную на фиг. 4 таблицу преобразования.

В случае таблицы передней стороны Т1a единичной таблицы Т1, показанной на фиг. 4 таблицы преобразования, при значении переменной состояния, равной 1, оба 16-разрядных кода для 8-разрядных входных сигналов "5" и "6" представляют собой 0010000000100100". Таким образом, демодулятор при приеме кода "0010000000100100" не может выполнять обратное преобразование. В таком случае, демодулятор считывает другой последующий символ. Таким образом, если последующий считываемый код представляет, например, "0010000000001001", то этот код представляет собой код, который преобразован для значения переменной состояния [3], потому что 13-й разряд кода представляет "1". Если текущий код представляет собой такой же код, здесь "0010000000100100", значение переменной состояния далее переходит к [2] или [3], если значением входного сигнала является "5" или "6", соответственно, демодулятор может правильно осуществлять декодирование, то есть он может проверить, является ли входной сигнал таким сигналом, значение переменной состояния которого в следующий момент переходит к [3], то есть "6".

На блок-схеме фиг. 13, на этапе S21 вводится 16-разрядный код. На этапе S22 производится обращение к таблице обратного преобразования. На этапе S23 производится проверка, можно ли выполнить однозначное декодирование. Если это так, то программа, естественно, может перейти к этапу S24 с целью вывода декодированного 8-разрядного сигнала.

На фиг. 14 представлена блок-схема иллюстративной конструкции демодулятора сигналов, в котором использовано настоящее изобретение.

На фиг. 14 16-разрядный входной код подается на схему 31 1- символьной задержки и логический элемент И.

Схема 31 1-символьной задержки задерживает входной 16-разрядный код на один символ. Задержанный таким образом на один символ 16-разрядный код поступает в ПЗУ 32 таблицы декодирования, имеющего первую таблицу декодирования 1Ta, и в ПЗУ 33 таблицы декодирования, имеющее вторую таблицу для декодирования 1Tb.

ПЗУ 32 первой таблицы декодирования, имеющее в себе первую таблицу декодирования 1Ta, принимает 16-разрядный код - для осуществления обратного преобразования с целью получения на выходе 8-разрядного сигнала. Если код представляет собой 16-разрядный код такого типа, который сам по себе не позволяет однозначно осуществлять обратное преобразование, демодулятор после вывода 16-разрядного кода дает на выходе 8-разрядный сигнал, значение переменной состояния которого переходит к [2]. Значение 8-разрядного выходного сигнала поступает на схему принятия решения 35.

Аналогично ПЗУ 32 первой таблицы декодирования, ПЗУ 33 второй таблицы декодирования, имеющее вторую таблицу для декодирования 1Tb, принимает 16-разрядный код и осуществляет обратное преобразование с целью получения на выходе 8-разрядного сигнала. Если 16-разрядный входной код представляет собой такой код, который позволяет осуществлять монистическое обратное преобразование, то на выходе ничего не появляется или появляются специальные данные. Если 16-разрядный код представляет собой такой код, который сам по себе не позволяет осуществлять монистическое обратное преобразование, модулятор, после вывода кода, обеспечивает на выходе 8-разрядное значение сигнала, значение переменной состояния которого переходит к [3]. Полученный таким образом на выходе модулятора 8- разрядный сигнал поступает на схему принятия решения 35.

Логическая схема И 34 производит логическую операцию И с входным 16-разрядным кодом и 16-разрядным кодом "1000000000001000", поступающим со схемы вырабатывания значения сравнения 36, который в шестнадцатеричном исчислении представляет "8008", с целью проверки первого и 13-го разряда входного 16-разрядного кода, и дает на выходе "0" и "1", если все двоичные разряды 16-разрядного выходного кода логической схемы И представляют "0" и, наоборот, соответственно. Поскольку "8008" представляет собой такой код, в котором только первый разряд и 13-й разряд представляют "1", а остальные разряды являются "0", в том случае, если самым старшим двоичным разрядом является первый разряд, выходной сигнал логического элемента И 34 представляет собой "0" или "1", если и первый разряд и 13-й разряд представляют "0", или если один или оба из первого и 13-го разрядов являются "1", соответственно.

На схему принятия решения 35 поступают сигнал с логической схемы И 34 и значения 8-разрядных сигналов из ПЗУ 32 первой таблицы декодирования и ПЗУ 33 второй таблицы декодирования. Вначале, если из ПЗУ 33 второй таблицы декодирования не поступает 8-разрядный сигнал или поступают специальные данные, то это показывает, что 16-разрядный входной код декодирован однозначно в 8-разрядный сигнал, так что на выходе схемы 35 принятия решения появляется в качестве выходного сигнала значение 8-разрядного сигнала, поступающего из ПЗУ 32 первой таблицы декодирования. Если значение 8-разрядного сигнала поступает из ПЗУ 33 второй таблицы декодирования, то это показывает, что входной 16-разрядный код не может быть однозначно декодирован в значение 8-разрядного сигнала. Поскольку данные, поступающие из ПЗУ 32 первой таблицы декодирования и ПЗУ 33 второй таблицы декодирования, прошли через схему 31 задержки на символ, эти сигналы являются кодами предварительного считывания на один символ. Таким образом, если 16-разрядный код, поступающий на вентильный элемент И 34, является кодом, преобразованным в отношении значения переменной состояния [2], то есть, если выходной сигнал логического элемента И 34 представляет "0", на выходе схемы принятия решения 35 появляется в качестве выходного сигнала 8-разрядный сигнал, поступающий из ПЗУ 32 первой таблицы декодирования. С другой стороны, если 16-разрядный код, поступающий на логический элемент И 34, является кодом, преобразованным в отношении переменной состояния [3], то есть, если выходной сигнал логического элемента И 34 представляет "1", на выходе схемы принятия решения 35 в качестве выходного сигнала появляется 8-разрядный сигнал, поступающий из ПЗУ 33 второй таблицы декодирования.

Вышеописанный вариант осуществления настоящего изобретения предпочтительно применяют прежде всего для модуляции и демодуляции при цифровой записи речевого сигнала, видеосигнала или данных на оптических дисках высокой плотности. Ниже приведен типичный формат сигнала на оптическом диске высокой плотности.

Система модуляции - Тип преобразования 8-16

Скорость передачи канальных двоичных разрядов - 24,43 мегабит в секунду

Система исправления ошибок - Перекрестно-перемежающийся код Рида-Соломона

Скорость передачи данных - 12,216 мегабит в секунду

Настоящее изобретение не ограничивается вышеописанными вариантами осуществления. Например, количество двоичных разрядов N входного сигнала или количество канальных двоичных разрядов М преобразованного сигнала не ограничивается величинами N = 8 или М = 16, а могут устанавливаться на требуемые произвольные величины.

Промышленная применимость

Как описано выше, в случае настоящего изобретения, поскольку дублированные части таблицы преобразования составлены таким образом, что коды каждого из двух связанных кодовых наборов представляют собой такие коды, в которых варианты изменения цифровой суммы (ИЦС) имеют противоположные знаки и примерно равны между собой по абсолютному значению, можно удовлетворительно подавить низкочастотные составляющие модулированного сигнала.

Кроме того, в случае настоящего изобретения таблица преобразования состоит из первой и второй подтаблиц, включающих в себя многочисленные кодовые группы, а подлежащая использованию при следующем преобразовании кодовая группа подключается кодом непосредственно перед преобразованием, так что N-разрядный код можно подсоединить без использования граничных двоичных разрядов.

Далее, в случае настоящего изобретения, таблица преобразования состоит из двух типов подтаблиц, обеспечивающих противоположные результаты положительного и отрицательного действий на накопленное изменение ИЦС, и модуляция выполняется двумя адаптивно подключаемыми подтаблицами, так что можно в достаточной степени подавлять низкочастотные составляющие модулированных сигналов.

В противоположность преобразованию 8-14, то есть модуляции EFM, обычно используемой в компакт-дисках, 8-разрядные входные сигналы можно преобразовывать в 16-канальные двоичные коды без использования объединяющих двоичных разрядов. То есть, в противоположность обычному способу, при котором 8-разрядная комбинация преобразуется в 14-разрядную информационную двоичную комбинацию и три объединяющих двоичных разряда, давая таким образом в итоге 17 двоичных разрядов, плотность записи информации можно увеличить на коэффициент 17/16, обеспечивая в то же время подавление низкочастотных составляющих.

Для увеличения плотности записи можно рассмотреть возможность преобразовывать 8-разрядный символ в 14 информационных разрядов, плюс два объединяющих разряда, обеспечивая таким образом в итоге 16 двоичных разрядов. В противоположность этому способу, низкочастотные составляющие модулированных сигналов можно в достаточной степени подавить вследствие наличия двух типов таблиц преобразования, обеспечивающих возможность выполнения инверсных операций, то есть положительной и отрицательной операций на накопленном изменении ИЦС, и модуляция выполняется в то время, как соответственным образом сменяются эти два типа таблиц.

Кроме того, сигналы, модулированные в соответствии с настоящей системой, можно декодировать посредством предварительного считывания дополнительного символа и выполнения декодирования сигнала совместно с демодулированным символом.

Изобретение относится к области записи или воспроизведения цифровых сигналов. Сущность изобретения: таблица преобразования с частичным дублированием используется в качестве таблицы преобразования, предназначенной для преобразования информационной последовательности на М-разрядной основе в кодовую последовательность на N-разрядной основе, где М и N являются целыми числами, имеющими соотношение М < N, без использования граничных двоичных разрядов. Таблица преобразования состоит из первой и второй подтаблиц, включающих в себя многочисленные кодовые группы, которые включают в себя различные коды для одинаковых входных данных. Вторая подтаблица представляет собой таблицу, которая частично дублируется первой подтаблицей и создается посредством назначения различных кодов данных из первых входных данных вторым входным данным. Коды последовательно назначаются всем кодовым группам в дублированных частях первой и второй подтаблиц в отношении входных данных от кода, имеющего максимальное абсолютное значение варианта изменения цифровой суммы. Благодаря этому, обеспечивается возможность подавления низкочастотных составляющих модулированного сигнала. 5 с. и 63 з.п. ф-лы, 14 ил.

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Пожарный двухцилиндровый насос | 0 |

|

SU90A1 |

| Автоматический огнетушитель | 0 |

|

SU92A1 |

| Делительный стол | 1976 |

|

SU558780A1 |

| Устройство для изготовления проволочных резисторов с аксиальными выводами | 1973 |

|

SU558310A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Тепловой газоанализатор | 1976 |

|

SU553530A1 |

| EP 0467674 А3, 22.01.1992 | |||

| US 5325240 А, 28.06.1994 | |||

| US 4688205 А, 18.08.1987 | |||

| СПОСОБ ПРИГОТОВЛЕНИЯ БЕЗДРОЖЖЕВОГО ХЛЕБА | 2004 |

|

RU2258372C1 |

| УСТРОЙСТВО ДЛЯ ОТВОДА ТЕПЛА ОТ ЭЛЕМЕНТОВ РАДИОЭЛЕКТРОННОЙ АППАРАТУРЫ С ПОВТОРНО-КРАТКОВРЕМЕННЫМИ ТЕПЛОВЫДЕЛЕНИЯМИ | 2003 |

|

RU2257606C2 |

| СПОСОБ ПРОИЗВОДСТВА БЕЛКОВО-МОЛОЧНОГО ПРОДУКТА | 2002 |

|

RU2246220C2 |

| Способ получения пропионовой кислоты | 1950 |

|

SU98153A1 |

| Способ упрочнения деталей, посредством циклической пластической деформации | 1960 |

|

SU133480A1 |

| КАРЕТОЧНЫЙ УЗЕЛ ПЕДАЛЬНОГО ПРИВОДА ВЕЛОСИПЕДА | 0 |

|

SU180100A1 |

| Способ получения гидроксилсодержащего каучука | 1961 |

|

SU143553A1 |

| Реле времени | 1959 |

|

SU123563A1 |

| Устройство для цифровой магнитной записи | 1990 |

|

SU1764084A1 |

| Устройство для цифровой магнитной записи | 1988 |

|

SU1569878A1 |

| Устройство для воспроизведения цифровой магнитной записи | 1987 |

|

SU1422245A1 |

Авторы

Даты

2001-07-27—Публикация

1995-07-07—Подача