Изобретение относится к микроэлектронике и может быть использовано при конструировании интегральных схем на МДПтранзисторах.

Цель изобретения - повышение надежности формирователя.

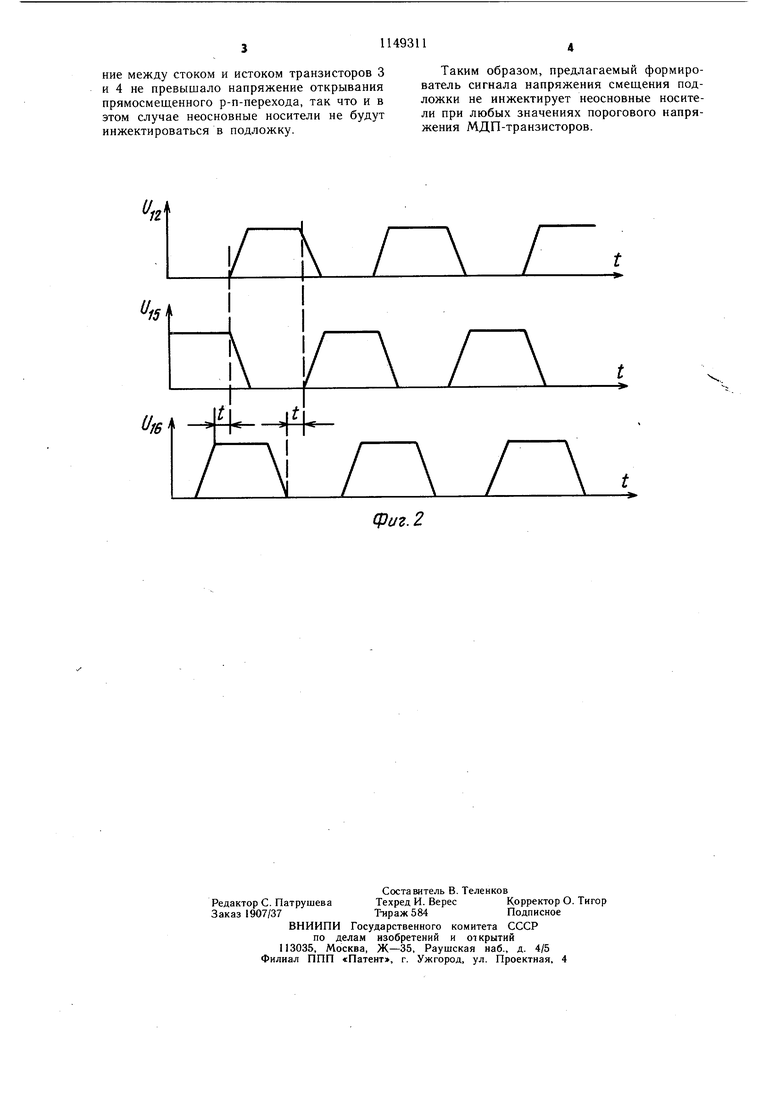

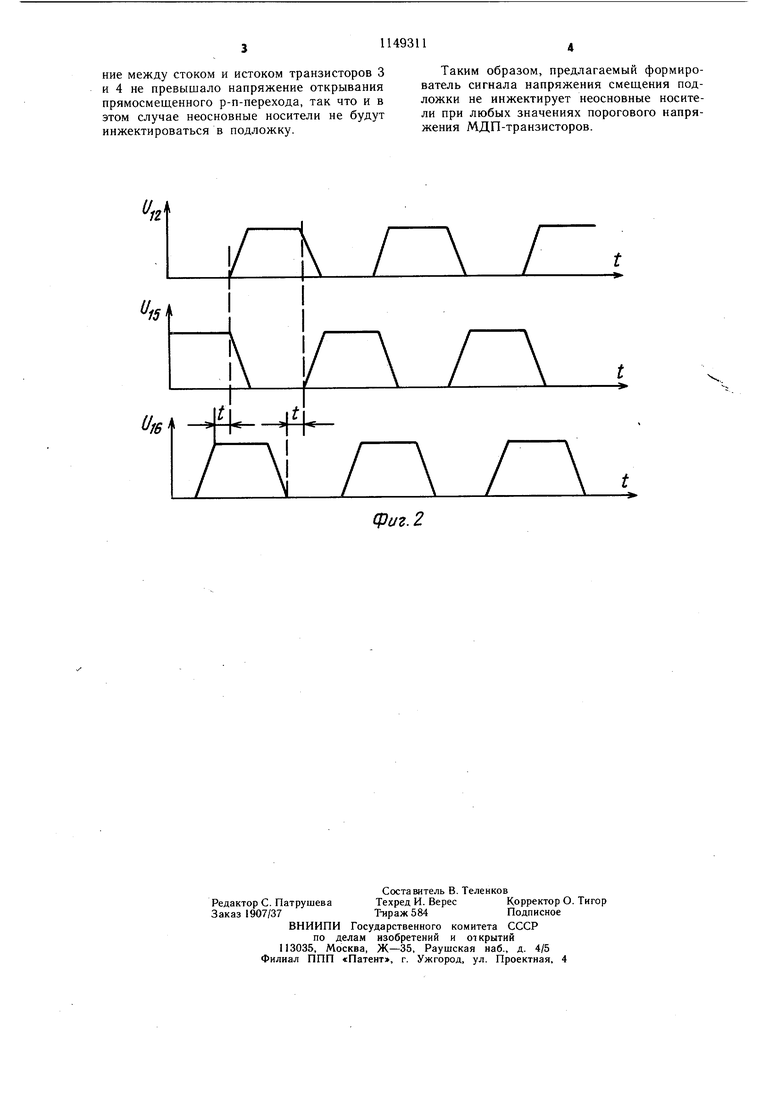

На фиг. 1 приведена принципиальная схема формирователя сигнала напряжения смещения подложки; на фиг. 2 - временная диаграмма входных сигналов.

Формирователь сигнала напряжения смещения подложки для интегральных схем содержит первый конденсатор 1, первый ключевой транзистор 2, второй ключевой транзистор 3, триггер на транзисторах 4 и 5, пороговые транзисторы 6 и 7, нагрузочный транзистор 8, второй, третий и четвертый конденсаторы 9-11. Первая обкладка конденсатора 1 подключена к первой входной шине 12, вторая соединена со стоком и затвором первого ключевого транзистора 2 и истоком второго ключевого транзистора 3, исток транзистора 2 соединен с общей шиной 13, сток транзистора 3 соединен с истоком транзисторов 4 и 5 триггера, истоками пороговых транзисторов 6 и 7 и выходной шиной 14, затвор первого транзистора триггера 4 соединен со стоком транзистора 5, стоком нагрузочного транзистора 8, одной обкладкой третьего конденсатора 10 и с затвором второго ключевого транзистора 3, затвор второго транзистора триггера 5 соединен со стоком первого транзистора триггера 4 одними обкладками второго и четвертого конденсаторов 9 и И, затвором и стоком одного порогового транзистора 7, другие обкладки второго 9, третьего 10 и четвертого 11 конденсаторов подключены соответственно к первой 12, второй 15 и третьей 16 входным шинам, затвор погрузочного транзистора 8 соединен с третьей входной шиной 16, затвор и сток другого порогового транзистора 6 соединен с истоком нагрузочного транзистора 8.

Формирователь сигнала напряжения смещения подложки работает при подаче последовательности импульсов напряжения одинаковой частоты на входные шины 12, 15, 16 с временными соотношениями, указанными на фиг. 2. Начала фронтов на первой и второй входных шинах 12 и 15 совпадают, фазы противоположны.

Импульс на третьей входной шине 16 опережает импульс на первой входной шине 12 на время t, равное 0,25-0,1 от периода следования импульсов.

Импульсы должны иметь амплитуду, превышающую по крайней мере в 1,5-2 раза пороговое напряжение МДП-транзистора.

К началу положительного фронта импульса на первой входной шине 12 затвор транзистора 3 через транзисторы 6 и 8 разряжен до потенциала выходной плюс величина порогового напряжения, транзистор 3 практически закрыт.

Во время положительного полупериода импульса на шине 12 конденсатор 1 заряжается до напряжения, равного амплитуде им пульса на шине 12 за вычетом величины порогового напряжения.

. Отрицательный фронт импульса на второй входной шине 15 передается через конденсатор 10 на затворы транзисторов 3 и 4, обеспечивая надежное запирание этих тран5 зисторов.

Положительный фронт импульса на шине 12 передается через конденсатор 9 на затвор транзистора 5.

Транзистор 5 удерживается в открытом

„ состоянии так, что падение напряжения между стоком и истоком транзистора 5 существенно меньше напряжения открывания р-п-перехода (стоковая область транзистора 5 - подложка), инжектирование носителей не происходит. Это обеспечивается тем,

5 что в то время, когда через транзистор 5 протекает максимальный ток, а он максимален во время отрицательного фронта импульса на шине 15, напряжение на затворе транзистора 5 также максимально, так при

- положительном фронте импульса на входе 12 почти вся амплитуда входного импульса передается на затвор транзистора 5.

К моменту прихода отрицательного фронта на вход 16 затвор транзистора 5 уже разряжен через транзистор 7 до напряжения выходной шины 14 плюс пороговое напряжение МДП-транзистора. Отрицательным фронтом импульса на входе 16 через конденсатор 11 транзистор 5 надежно закрывается.

Положительный фронт импульса на входе 15 почти полностью передается на затворы транзисторов 3 и 4, так как транзистор 5 к этому времени закрыт, а транзистор 8 либо также закрыт, либо открыт небольшим напряжением.

5 Высокое напряжение на затворах транзисторов 3 и 4 сохраняется до прихода положительного фронта на входную шину 16, после чего затворы разряжаются через транзисторы 6 и 8 до потенциала выходной шины плюс пороговое напряжение МДПтранзистора.

Во время отрицательного полупериода импульса на первой входной шине 12 заряд с конденсатора 1 через открытый транзистор 3 передается на выходную шину 14.

5 Затвор транзистора 5 в это время через открытый транзистор 4 подключен к выходной шине. Проводимости транзисторов 3 и 4 выбираются таким образом, чтобы напряжение между стоком и истоком транзисторов 3 и 4 не превышало напряжение открывания прямосмещенного р-п-перехода, так что и в этом случае неосновные носители не будут инжектироваться в подложку.

Таким образом, предлагаемый формирователь сигнала напряжения смещения подложки не инжектирует неосновные носители при любых значениях порогового напряжения МДП-транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адресный формирователь | 1988 |

|

SU1624521A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

| Адресный формирователь | 1981 |

|

SU991504A1 |

| Формирователь напряжения смещения подложки для интегральных схем | 1986 |

|

SU1322374A1 |

| Усилитель считывания | 1982 |

|

SU1120405A1 |

| Формирователь сигнала выборки на МДП-транзисторах | 1986 |

|

SU1338024A1 |

| Формировтель напряжения смещения подложки для интегральных схем | 1983 |

|

SU1185396A1 |

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1993 |

|

RU2043665C1 |

| Формирователь импульсов | 1981 |

|

SU1003348A1 |

| Формирователь импульсов | 1982 |

|

SU1091327A1 |

ФОРМИРОВАТЕЛЬ СИГНАЛА НАПРЯЖЕНИЯ СМЕЩЕНИЯ ПОДЛОЖКИ ДЛЯ ИНТЕГРАЛЬНЫХ СХЕМ, содержащий первый конденсатор, первый и второй ключевые транзисторы, одна обкладка первого конденсатора подключена к первой входной шине, другая соединена со стоком, затвором первого и истоком второго ключевых транзисторов, исток первого ключевого транзистора соединен с общей щнной, сток второго ключевого транзистора соединен с выходной щиной, отличающийся тем, что, с целью повышения надежности формирователя, он содержит триггер: выполненный на первом и втором транзисторах, пороговые транзисторы, нагрузочный транзистор, второй, третий и четвертый конденсаторы, причем истоки первого и второго транзисторов триггера соединены с истоками пороговых транзисторов и с выходной щиной формирователя, затвор первого и сток второго транзисторов триггера соединены со стоком на грузочного транзистора, одной из обкладок третьего конденсатора и затвором второго ключевого транзистора, затвор второго и сток первого транзисторов триггера соединены с одними обкладками второго и четвертого конденсаторов, с затвором и истоком одного порогового транзистора, другие обкладки второго, третьего и четвертого конденсаторов подключены соответственно к персл вой, второй и третьей входным шинам, затвор нагрузочного транзистора соединен с третьей входной щиной, затвор и исток другого порогового транзистора соединены с истоком нагрузочного транзистора. i4 ;о оо

фиг. 2

| International Solid-State Circuits Conference Digest | |||

| of Teehnical Papers, IEEE, 1979, p | |||

| Крутильная машина для веревок и проч. | 1922 |

|

SU143A1 |

| «Электроника, 1977, № 16, с | |||

| Коридорная многокамерная вагонеточная углевыжигательная печь | 1921 |

|

SU36A1 |

Авторы

Даты

1985-04-07—Публикация

1983-06-21—Подача