Изобретение относится к электронике и может быть использовано в БИС на Н/ТП-транзисторах.

Цель изобретения - снижение потребляемой мощности за счет устранения пороговых потерь.

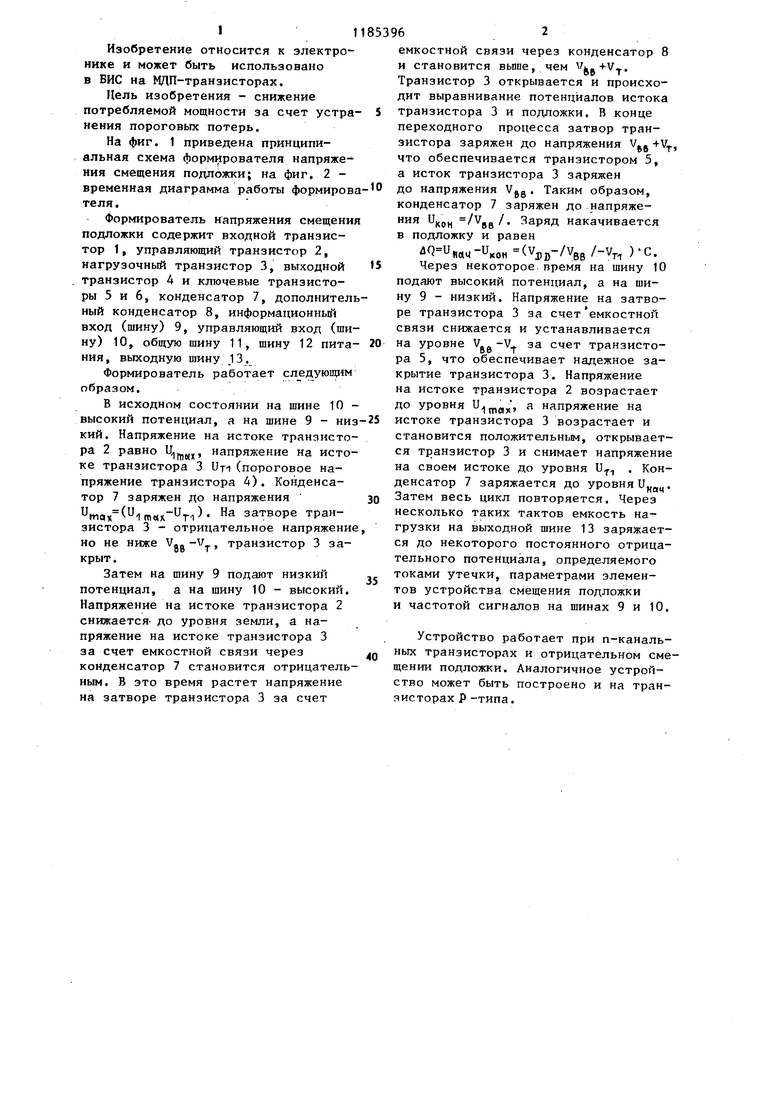

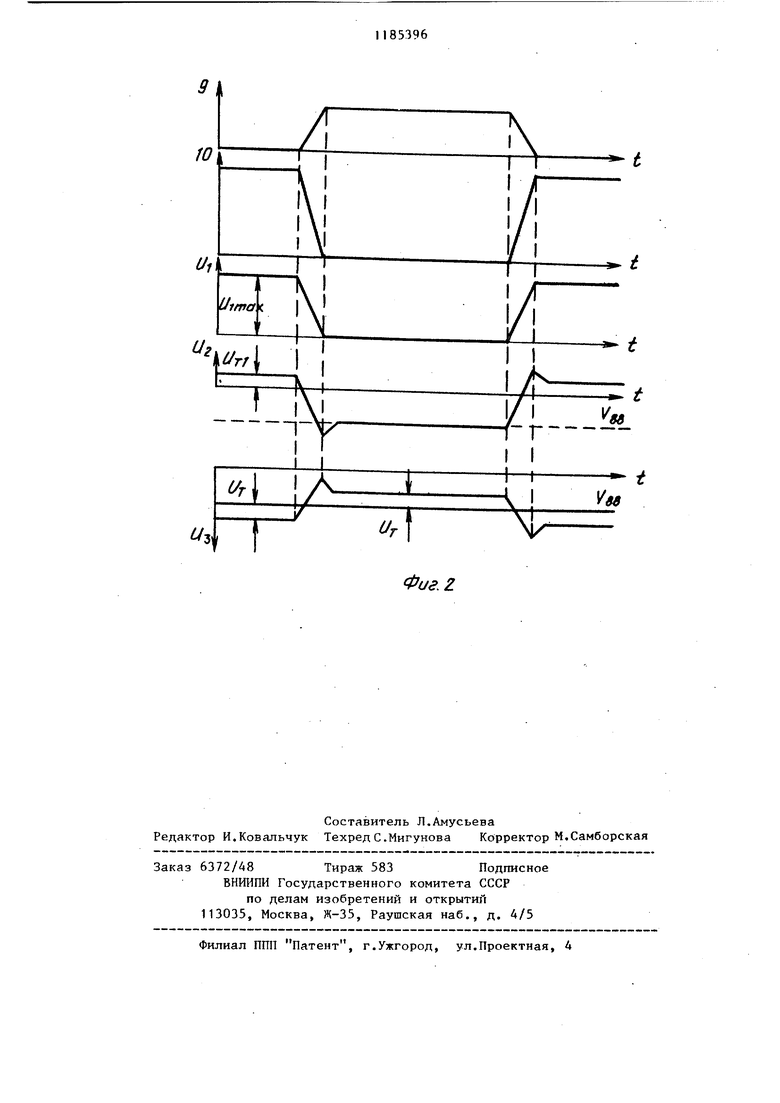

На фиг. 1 приведена принципиальная схема формирователя напряжения смещения подложки; на фиг, 2 временная диаграмма работы формирова теля.

Формирователь напряжения смещения подложки содержит входной транзистор 1, управляющий транзистор 2, нагрузочный транзистор 3, выходной транзистор 4 и ключевые транзисторы 5 и 6, конденсатор 7, дополнительный конденсатор 8, информационньй вход (шину) 9, управляющий вход (шину) 10, общую шину 11, шину 12 питания, выходную шину 13.

Формирователь работает сл едующим образом.

В исходном состоянии на шине 10 высокий потенциал, а на шине 9 - низ кий. Напряжение на истоке транзистора 2 равно , напряжение на истоке транзистора 3 Uy-i (пороговое напряжение транзистора 4). Конденсатор 7 заряжен до напряжения

Umar(tm«rUri) затворе транзистора 3 - отрицательное напряжение но не ниже Vgg-v, транзистор 3 закрыт .

Затем на шину 9 подают низкий потенциал, а на шину 10 - высокий. Напряжение на истоке транзистора 2 снижается- до уровня земли, а напряжение на истоке транзистора 3 за счет емкостной связи через конденсатор 7 становится отрицательным. В это время растет напряжение на затворе транзистора 3 за счет

емкостной связи через конденсатор 8 и становится вьппе, чем Транзистор 3 открывается и происходит выравнивание потенциалов истока транзистора 3 и подложки. В конце переходного процесса затвор транзистора заряжен до напряжения V -t-V что обеспечивается транзистором 5, а исток транзистора 3 заряжен до напряжения Vgg. Таким образом, конденсатор 7 заряжен до напряжения UHP накачивается в подложку и равен

Q u«rt4-u,oH (VJ,J,-/VBB /-v, )С.

Через некоторое время на шину 10 подают высокий потенциал, а на шину 9 - низкий. Напряжение на затворе транзистора 3 за счет емкостной связи снижается и устанавливается на уровне V.-V за счет транзистора 5, что обеспечивает надежное закрытие транзистора 3. Напряжение на истоке транзистора 2 возрастает до уровня , а напряжение на истоке транзистора 3 возрастает и становится положительным, открывается транзистор 3 и снимает напряжение на своем истоке до уровня . . Конденсатор 7 заряжается до уровня и„дц. Затем весь цикл повторяется. Через несколько таких тактов емкость нагрузки на выходной шине 13 заряжается до некоторого постоянного отрицательного потенциала, определяемого токами утечки, параметрами элементов устройства смещения подложки и частотой сигналов на шинах 9 и 10.

Устройство работает при п-канальных транзисторах и отрицательном смещении подложки. Аналогичное устройство может быть построено и на транзисторах Р-типа.

ГТ

Фuг.Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь напряжения смещения подложки для интегральных схем | 1986 |

|

SU1322374A1 |

| Формирователь сигнала напряжения смещения подложки для интегральных схем | 1983 |

|

SU1149311A1 |

| Адресный формирователь | 1988 |

|

SU1624521A1 |

| Адресный формирователь | 1981 |

|

SU991504A1 |

| Формирователь импульсов | 1982 |

|

SU1091327A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

| Адресный формирователь | 1981 |

|

SU1007133A1 |

| Формирователь импульсов | 1982 |

|

SU1238230A1 |

| Адресный формирователь | 1981 |

|

SU970460A1 |

| Усилитель считывания | 1982 |

|

SU1120405A1 |

ФОРМИРОВАТЕЛЬ НАПРЯЖЕНИЯ СМЕЩЕНИЯ ПОДЛОЖКИ ДЛЯ ИНТЕГРАЛЬНЫХ . СХЕМ, содержшчий управляющий транзистор, затвор которого является управЛЯЮР1ИМ входом формирователя, а сток подключен к шине питания, входной транзистор, затвор которого является информационным входом формирователя, сток подключен к истоку управляющего транзистора, конденсатор, одна обкладка которого соединена с истоком управляющего транзистора, нагрузочный транзистор и выходной транзистор, затвор и сток которого соединены с другой обкладкой конденсатора и истоком нагрузочного транзистора, сток которого является вьрсодом формирователя, истоки входного и выходного транзисторов подключены к общей шине, отличающийся тем, что, с целью снижения потребляемой мощности, в него введены дополнительный конденсатор и два ключевых транзистора, затвор первого и истоки первого и второго кхпочевых транзисторов соединены с затвором нагрузочного транзистора и одной обкладкой (Л дополнительного конденсатора, другая обкладка которого соединена с затвором входного транзистора, стоки первого и второго ключевых транзисторов и затвор второго подключены к стоку нагрузочного транзистора.

| IEE International Sol id-State Circuits Conference | |||

| Digest of Technical Papers, 1979, p | |||

| Крутильная машина для веревок и проч. | 1922 |

|

SU143A1 |

| Электроника | |||

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Коридорная многокамерная вагонеточная углевыжигательная печь | 1921 |

|

SU36A1 |

Авторы

Даты

1985-10-15—Публикация

1983-06-21—Подача