.

2.Запоминающее устройство с диагностикой отказов, содержащее группы формирователей сигналов четности, блоки сравнения, блок индикации и накопитель,выкоды первой группы которого являются информационными выходами устройства, а выходы второй и третьей групп соединены соответственно с одними из входов первого и второго блоков сра1внения, другие входы которых подключены соответственно к выходам формирователе сигналов четности первой и второй групп, отличающееся тем что, с целью расщирения области применения устройства, в него введены формирователи кода Бергера, сумматоры по модулю два и элементы ИЛИ-НЕ выходы которых соединены с входами блока индикации, а входы - с одними из выходов сумматоров по модулю два, входы которых подключены соответственно к входам первого и второго блоков сравнения, причем входы формирователей кода Бергера соединены с выходами первой группы накопителя,

а выходы - с входами формирователей сигналов четности, другие выходы сумматоров по. модулю два являются контрольными выходами устройства.

3.Запоминающее устройство с диагностикой отказов, содержащее ГРУПпы формирователей сигналов четности, блоки сравнения, блок индикации и накопитель, входы и вькоды первой группы которого являются информационными и выходами устройства, выходы второй и третьей групп накопителя подключены соответственно с

.одним из входов первого и второго блоков сравнения, другие, входы которых соединены соответственно с выходами формирователей сигналов четности первой и второй групп, о тли чающееся тем, что, с целью расщирения области применения устройства, в него введены формирователи кода Бергера, сумматоры по модулю два, коммутаторы и элементы ШШ-НЕ,, выходы которых соединены с

6958.

входами блока индикации, а входы - с выходами сумматоров по-.модулю два, входы которых подключены соответственно к выходам первого и второго блоков сравнения, входы формирователей кода Бергера соединены с выходами первой группы накопителя, а вьгходы с входами формирователей сигналов четности первой и второй групп, выходы которых подключены соответственно к входам первого и второго коммутаторов, выходы которых соединены соответственно с входами вто1: ой и третьей групп накопителя.

4.Устройство по п. 1, отличающееся тем, что адресные входы накопителя соединены с входами цругих формирователей кода Бергера первой и второй групп.

5.Устройство по пп. 1 и 4, отличающееся тем, что выходы других формирователей кода Бергера первой и второй групп подключены соответственно к входам других формирователей сигналов четности первой и третьей групп.

6.Устройство по пп, 1 и 4, отличающееся тем, что вьгходы других формирователей кода Бергера первой и второй групп соединены соответственно с входами других формирователей сигналов четности второй и четвертой групп,

7.Устройство по п. 1, отличающееся тем, что адресные входы накопителя подключены

к входам других формирователей сигналов четности групп с первой по четвертую.

8.Устройство по п. 1, отличающееся тем, что адресные входы накопителя соединены с входами других формирователей сигналов чётности первой и третьей групп,

9.Устройство по п. 1, о т л ичающееся тем, что адресные входы накопителя соединены с входами других формирователей сигналов четности второй и четвертой групп.

. 1

Изобретение относится к вьшислительной технике, в част1ности к запоминающим устройствам со схемами обнаружения ошибок, и может быть использовано в полупроводниковых модульных запоминающих устройствах.

Цель изобретения - повьшение информационной емкости устройства за счет увеличения отношения числа информационных разрядов к контрольным, а также расширение области применения и обеспечение возможности обнаружения адресных ошибок.

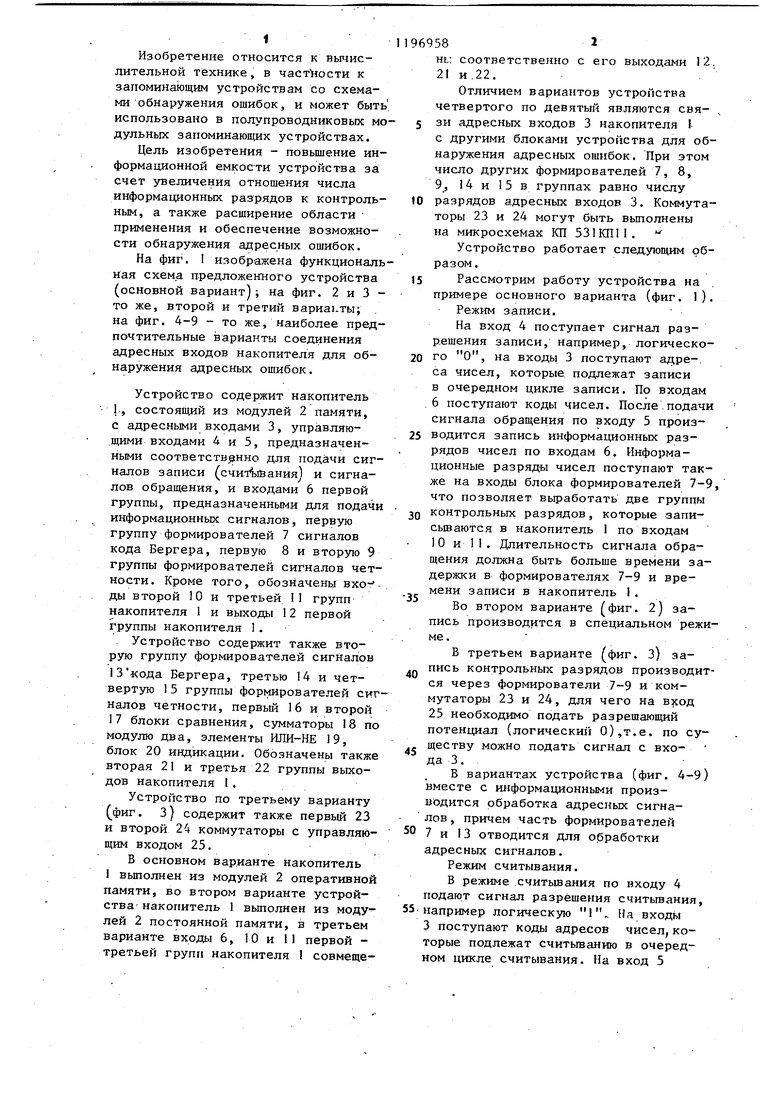

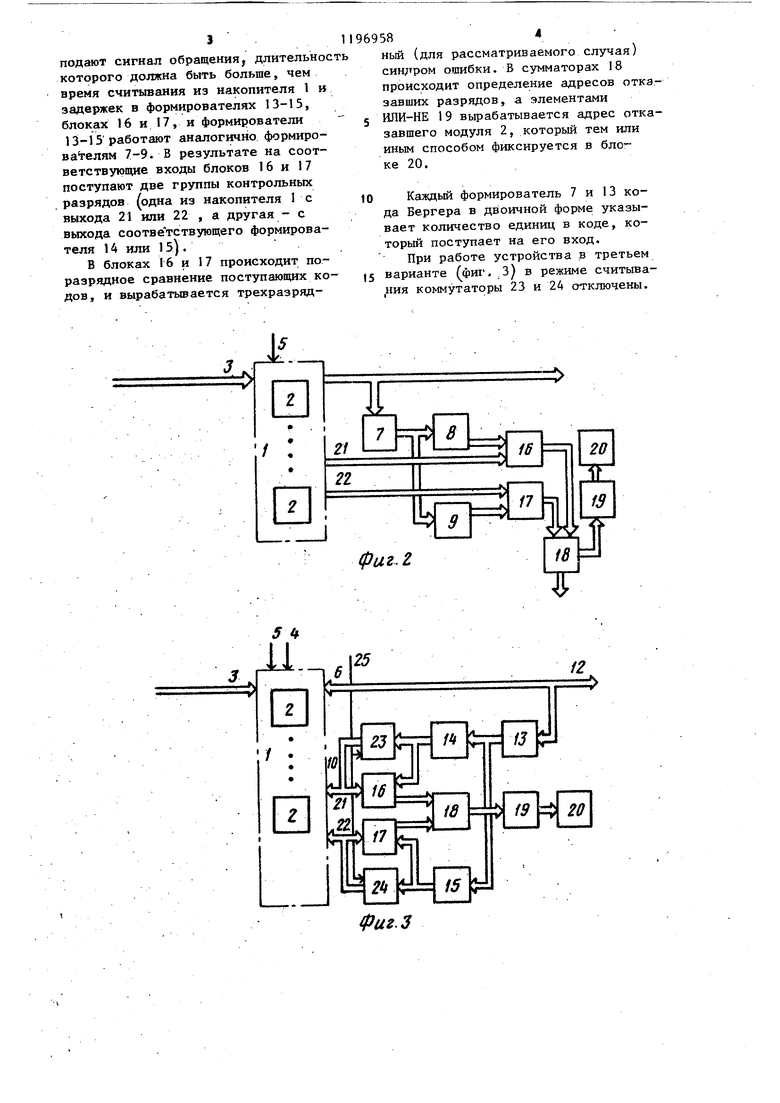

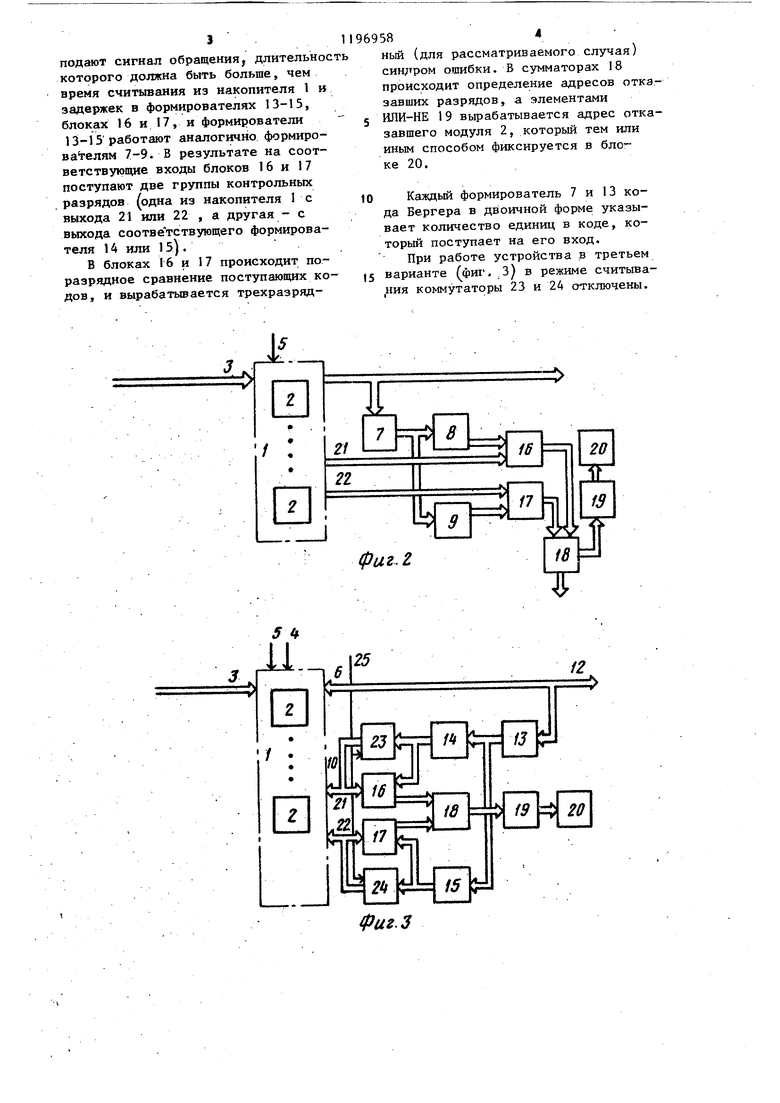

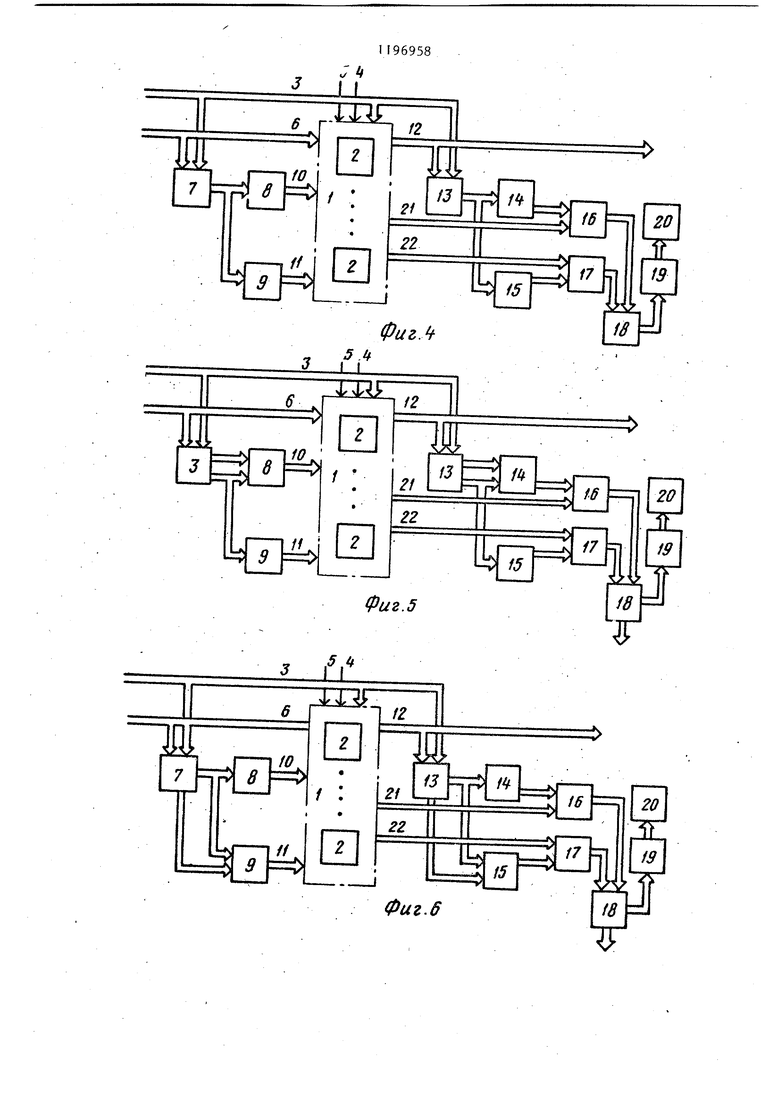

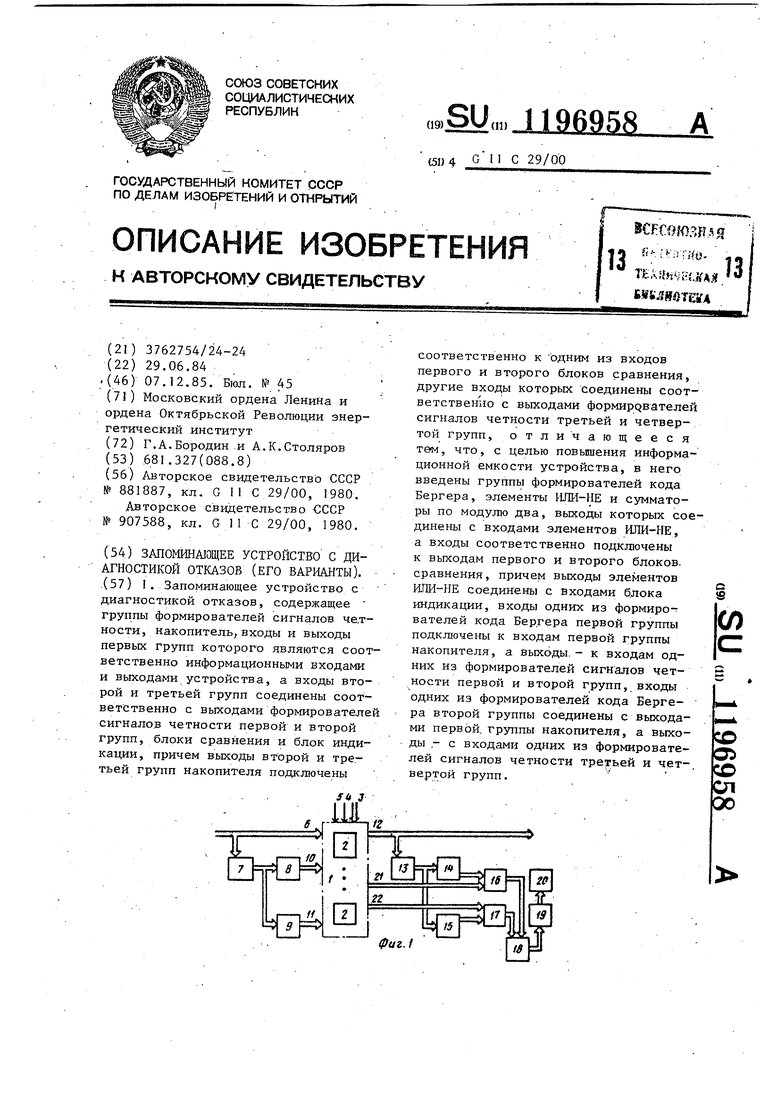

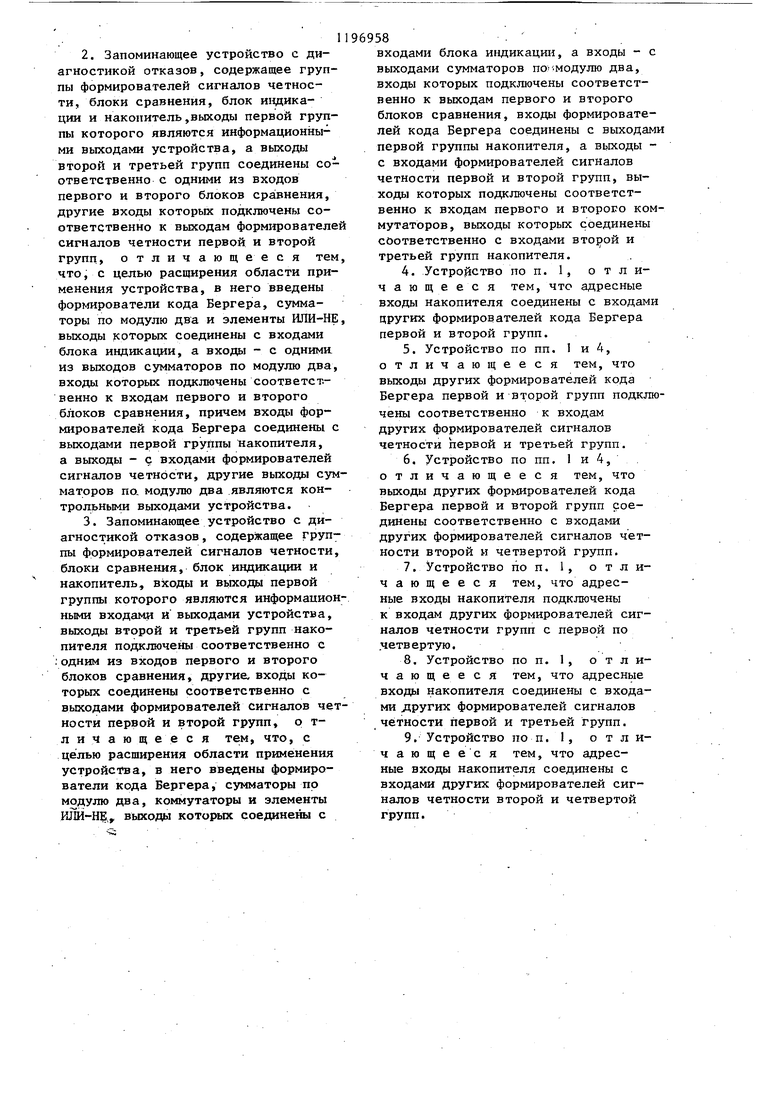

На фиг. I изображена функциональная схема предложенного устройства (основной вариант); на фиг. 2 и 3 то же, второй и третий варианты; . на фиг. 4-9 - то же, наиболее предпочтительные варианты соединения адресных входов накопителя для обнаружения адресных ошибок.

Устройство содержит накопитель 1, состоящий из модулей 2 памяти, с адресными входами 3, управляющими входами 4 и 5, предназначенными соответственно для подачи сигналов записи (счи-Айания) и сигналов обращения, и входами 6 первой группы, предназначенными для подачи информационных сигналов, первую группу формирователей 7 сигналов кода Бергера, первую 8 и вторую 9 группы формирователей сигналов четности. Кроме того, обозначены второй 10 и третьей II групп накопителя 1 и выходы 12 первой группы накопителя I.

Устройство содержит также вторую группу формирователей сигналов

13«ода Бергера, третью 14 и четвертую 15 группы формирователей сигналов четности, первый 16 и второй I7 блоки сравнения, сумматоры 18 по модулю два, элементы ИЛИ-НЕ 19, блок 20 индикации. Обозначены также вторая 21 и третья 22 группы выходов накопителя I.

Устройство по третьему варианту (фиг. 3) содержит также первый 23 и второй 24 коммутаторы с управляющим входом 25.

В основном варианте накопитель I вьшолнен из модулей 2 оперативной памяти, во втором варианте устройства накопитель 1 вьшолнен из модулей 2 постоянной памяти, в третьем варианте входы 6, 10 и II первой третьей групп накопителя I совмеще196958

HL: соответственно с его выходами 12. 21 и.22.

Отличием вариантов устройства четвертого по девятый являются свя- ., 5 зи адресных входов 3 накопителя I с другими блоками устройства для обнаружения адресных ошибок. При этом число других формирователей 7, 8, 9, 14 и 15 в группах равно числу 10 разрядов адресных входов 3. Коммутаторы 23 и 24 могут быть вьтолнены на микросхемах КП 531КП11.

Устройство работает след.у1ощим образом.

15 Рассмотрим работу устройства на . примере основного варианта (фиг. 1).

Режим записи.

На вход 4 поступает сигнал разрешения записи, например, логического О, на входы 3 поступают адре-. са чисел, которые подлежат записи в очередном цикле записи. По входам 6 поступают коды чисел. После.подачи сигнала обращения по входу 5 производится запись информационных разрядов чисел по входам 6. Информационные разряды чисел поступают также на входы блока формирователей 7-9, что позволяет выработать две группы 30 контрольных разрядов, которые записьшаются в накопитель 1 по входам 10 и II. Длительность сигнала обращения должна быть больше времени задержки в формирователях 7-9 и времени записи в накопитель 1.

-35

Во втором варианте (фиг. 2) запись производится в специальном режи. ме.

В третьем варианте (фиг. З) запись контрольных разрядов производит4 /

ся через формирователи 7-9 и коммутаторы 23 и 24, для чего на вход 25 необходимо подать разрешающий потенциал (логический 0),т.е. по су., ществу можно подать сигнал с вхо45

да 3.

В вариантах устройства (фиг. 4-9) вместе с информационными производится обработка адресных сигналов , причем часть формирователей 50 7 и I3 отводится для обработки адресных сигналов. Режим считывания. В режиме считьшания по входу 4 подают сигнал разрешения считьшания, 55. например логическую I. FJa входы 3 поступают коды адресов чисел, которые подлежат считьгоанию в очередном цикле считывания. На вход 5

Э

подают сигнал обращения, длительно которого должна быть больше, чем время считывания из накопителя 1 и задержек в формирователях 13-15, блоках 16 и 17, и формирователи 13-15работают аналогично формировагелям 7-9. В результате на соответствующие входы блоков 16 и I7 поступают две группы контрольных разрядов (одна из накопителя 1 с выхода 21 или 22 , а другая - с выхода соответствующего формирователя 14 или 15) .

В блоках 16 и 17 происходит поразрядное сравнение поступающих кодов, и вырабатьшается трехразрядJf.

584

ньм (для рассматриваемого случая) синлром ошибки. В сумматорах 18 происходит определение адресов отказавших разрядов, а элементами ИЛИ-НЕ 19 вырабатывается адрес отказавшего модуля 2, который тем или иным способом фиксируется в блоке 20.

Каждьш формирователь 7 и 13 кода Бергера в двоичной форме указывает количество единиц в коде, который поступает на его вход.

При работе устройства в третьем

варианте (фиг. З) в режиме считыва11ИЯ коммутаторы 23 и 24 отключены.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1983 |

|

SU1149317A1 |

| Запоминающее устройство с самоконтролем /его варианты/ | 1984 |

|

SU1272358A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1149319A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с обнаружением наиболее вероятных ошибок | 1983 |

|

SU1149313A1 |

| Запоминающее устройство с исправлением ошибок | 1985 |

|

SU1305781A1 |

| Запоминающее устройство с коррекцией ошибок (его варианты) | 1984 |

|

SU1188790A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302326A1 |

. Запоминающее устройство с диагностикой отказов, содержащее группы формирователей сигналов че.тности, накопитель, входы и выходы первых групп которого являются соответственно информационными входами и выходами устройства, а входы второй и третьей групп соединены соответственно с выходами формирователей сигналов четности первой и второй групп, блоки сравнения и блок индикации, причем выходы второй и третьей групп накопителя подключены 8СНСОЮЛ ДЯ 13 |з rcASlj s HUAjir/ .7fforew соответственно к одним из входов первого и второго блоков сравнения, другие входы которых соединены соответственно с выходами формиррвателей сигналов четности третьей и четвертой групп, отличающееся тем, что, с целью повышения информационной емкости устройства, в него введены группы формирователей кода Бергера, элементы ИЛИ-НЕ и сумматоры по модулю два, выходы которых соединены с входами элементов ИЛИ-НЕ, а входы соответственно подключены к выходам первого и второго блоков, сравнения, причем выходы элементов о Ш1И-НЕ соединены с входами блока индикации, входы одних из формиро-т (Л вателей кода Бергера первой группы подключены к входам первой группы накопителя, а выходы, - к входам одних из формирователей сигналов четности первой и второй групп, входы одних из формирователей кода Бергера второй группы соединены с выходами первой, группы накопителя, а выхосо ды - с входами одних из формироватеО5 лей сигналов четности третьей и чет-, х вертой групп. ел 00

Л

Фиг.З

.;« и

Ф

If

-г

3 I I

L:

А

rv

г-1 17 ; 1F

J

22

Ч

U

J

.J

5iV

| Контактор постоянного тока с бездуговой коммутацией | 1980 |

|

SU881887A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU907588A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-12-07—Публикация

1984-06-29—Подача