к

05

со

|ЬО

М

1

Изоб1эетение относится к вьмислительной технике и может бь1ть использовано в цифровых вычисл1 тельных устройствах для перевода чисел из двоичног-о кода в код системы остаточных классов,

Цель изобретения - сокраще 1ие количества оборудования.

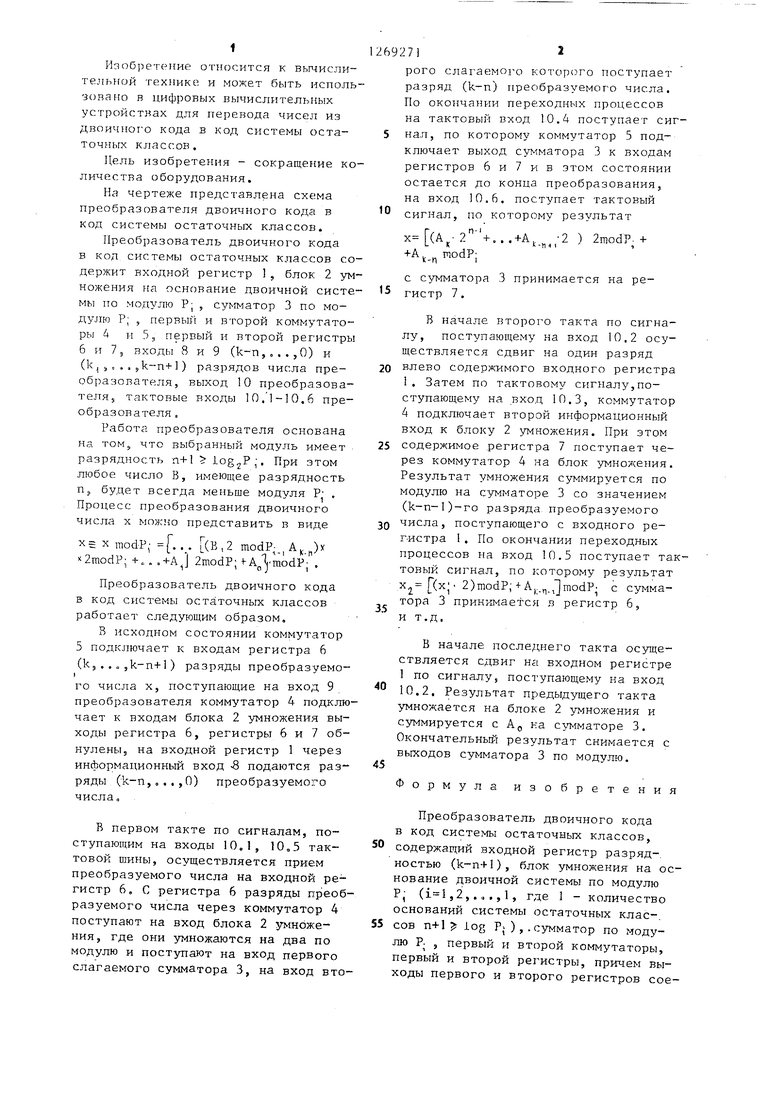

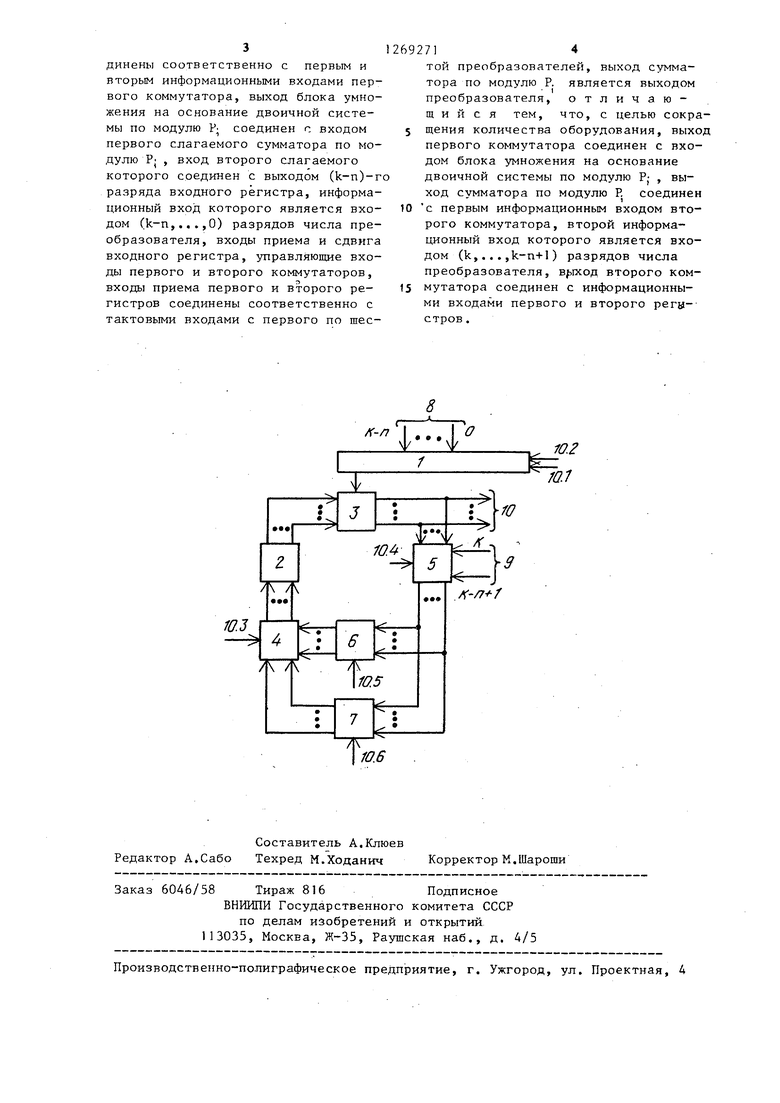

На чертеже представлена схема преобразователя двоичного кода в код системы остаточных классов.

Преобразователь двоичного кода в код системы остаточных классов содержит входной регистр 1, блок 2 умножения на основание двоичной системы по модулю Р; 5 сумматор 3 по модулю Р; , первый и второй коммутаторы 4 и 5, первый и второй регистры 6 и 7, входы 8 и 9 (k-n,,..,0) и (1, j . . jk-n+) разрядов числа преобразователя, выход 10 преобра.зователя, тактовые входы 10,1-10.6 преобразователя ,

Работа преобразователя основана на том, что выбранный модуль имеет разрядность п+1 5 ,. При этом любое число В, имеющее разрядность п., будет всегда меньше модуля , Процесс преобразования двоичного числа X можно представить в виде

х X ... (В, 2 modP-, А|.)х 2raodP;+.. .+А 2modP; i-A modP; .

Преобразователь двоичного кода в код системы остаточных классов работает следующим образом.

В исходном состоянии коммутатор 5 подключает к входам регистра 6

(kj . .., jk-n+1) разряды преобразуемоt го числа X, поступающие на вход 9

преобразователя коммутатор 4 подключает к входам блока 2 умножения выходы регистра 6, регистры 6 и 7 обнулены, на входной регистр 1 через информационный вход -8 подаются разряды (k-n,,..,0) преобразуемого числа,

В первом такте по сигналам, поступающим на входы 10,1, 10,5 тактовой шины, осуществляется прием преобразуемого числа на входной регистр 6. С регистра 6 разряды преобразуемого числа через коммутатор 4 поступают на вход блока 2 умножения, где они умножаются на два по модулю и поступают на вход первого слагаемого сумматора 3, на вход вто69271

рого слагаемого которого поступает разряд (k-n) преобразуемого числа. По окончании переходных процессов на тактовый вход 10.4 поступает сиг5 нал, по которому коммутатор 5 подключает выход сумматора 3 к входам регистров 6 и 7 и в этом состоянии остается до конца преобразования, на вход 10.6. поступает тактовый сигнал, по которому результат

х( + ...+А,.;2 ) 2mod + +А,., modP;

с сумматора 3 принимается на ре5 гистр 7.

В начале второго такта по сигналу, поступающему на вход 10.2 осуществляется сдвиг на один разряд

20 влево содержимого входного регистра 1. Затем по тактовому сигналу,поступающему на вход 10.3, коммутатор 4 подключает второй информационный вход к блоку 2 умножения. При этом

25 содержимое регистра 7 поступает через коммутатор 4 на блок умножения. Результат умножения суммируется по модулю на сумматоре 3 со значением (k-п-1)-го разряда преобразуемого

3Q числа, поступающего с входного регистра 1 . По окончании переходных процессов на вход 10.5 поступает тактовый сигнал, по которому результат Хл (х 2)modP,+ Aj,.., modP с сумматора 3 принижается в регистр 6,

и т.д.

в начале последнего такта осуществляется сдвиг на входном регистре 1 по сигналу, поступающему на вход 10.2. Результат предыдущего такта умножается на блоке 2 умножения и суммируется с Ар на сумматоре 3. Окончательный результат снимается с

выходов сумматора 3 по модулю. 5

Формула изобретения

Преобразователь двоичного кода в код системы остаточных классов,

0 содержащий входной регистр разряд-, ностью (k-n+1), блок умножения на основание двоичной системы по модулю Р; (,2,.,,,,, где 1 - количество оснований системы остаточных клас-.

5 сов п+1 log р. ),.сумматор по модулю р. , первый и второй коммутаторы, первый и второй регистры, причем выходы первого и второго регистров соединены соответственно с первым и вторым информационными входами первого коммутатора, выход блока умножения на основание двоичной системы по модулю р. соединен с входом первого слагаемого сумматора по модулю PJ , вход второго слагаемого которого соединен с выходом (k-n)-r разряда входного регистра, информационный вход которого является входом (k-n,.,.,0) разрядов числа преобразователя, входы приема и сдвига входного регистра, управляющие входы первого и второго коммутаторов, входы приема первого и второго регистров соединены соответственно с тактовыми входами с первого по шес692714

той преобразователей, выход сумматора по модулю Р. является выходом преобразователя, отличающийся тем, что, с целью сокра5 щения количества оборудования, выход первого коммутатора соединен с входом блока умножения на основание двоичной системы по модулю Pj , выход сумматора по модулю Р. соединен 10 с первым информационным входом второго коммутатора, второй информационный вход которого является входом (k,...,k-n+l) разрядов числа преобразователя, второго ком15 мутатора соединен с информационными входами первого и второго регу-стров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в код системы остаточных классов | 1984 |

|

SU1156058A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1985 |

|

SU1322483A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1987 |

|

SU1432784A1 |

| Преобразователь двоичного кода в модулярный код | 1985 |

|

SU1267624A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU1001079A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU983701A1 |

| Преобразователь непозиционного кода в двоичный код | 1988 |

|

SU1578810A1 |

| Устройство для вычисления остатка по модулю 2 @ +1 | 1990 |

|

SU1734212A1 |

| РЕВЕРСИВНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА В ДВОИЧНЫЙ | 1990 |

|

RU2022467C1 |

| Преобразователь числа в модулярный код | 1987 |

|

SU1444961A1 |

Изобретение относится к вычислительной технике. Целью изобретения является сокращение количества оборудования. Поставленная цель достигается тем, что в преобразователе двоичного кода в код системы остаточных классов, содержащем вхоДной регистр, блок умножения на два по модулю, сумматор по модулю,первый и второй коммутаторы, первый и второй регистры, первый регист;. используется для приема старших разрядов преобразуемого числа. Это позволяет уменьшить разрядность входного регистра. 1 ил.

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU983701A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU1001079A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-07—Публикация

1985-04-08—Подача