Изобретение относится к вычислительной технике и может быть использовано для организации межпроцессорного обмена в многопроцессорных вычислительных системах, а также для асинхронной связи приемника (передатчика) информации с ЭВМ.

Целью изобретения является расширение области применения устройства путем обеспечения асинхронного бесконфликтного обмена между источником и приемником информации.

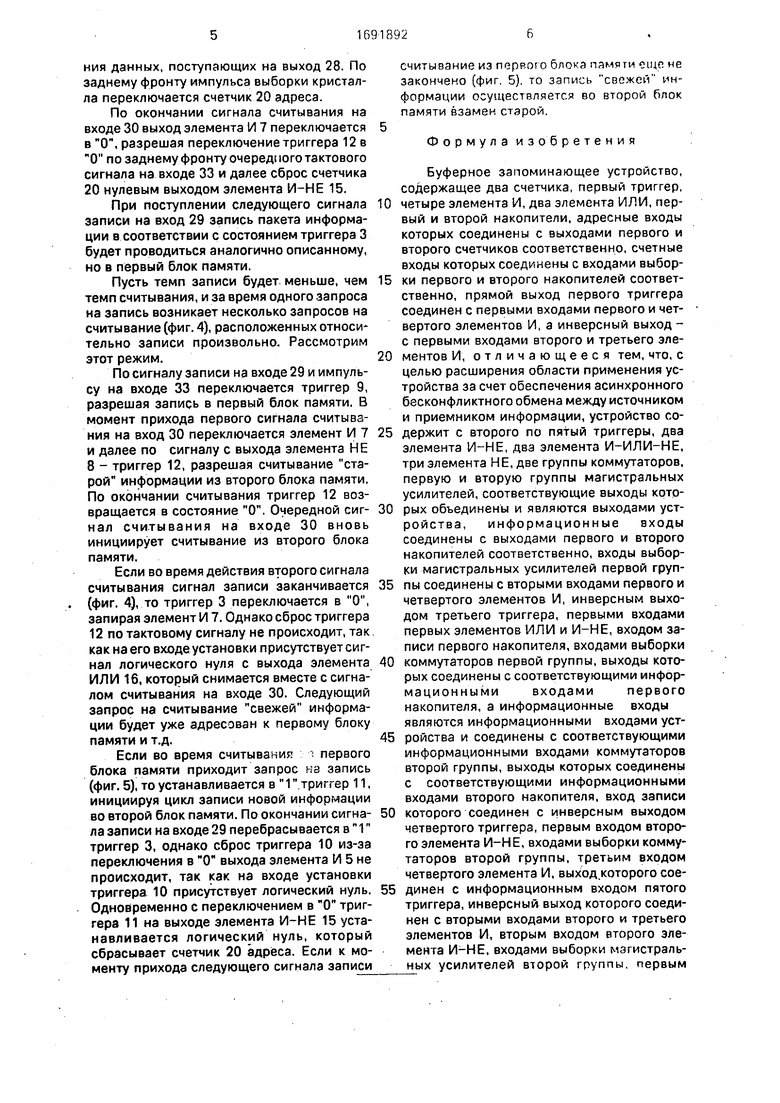

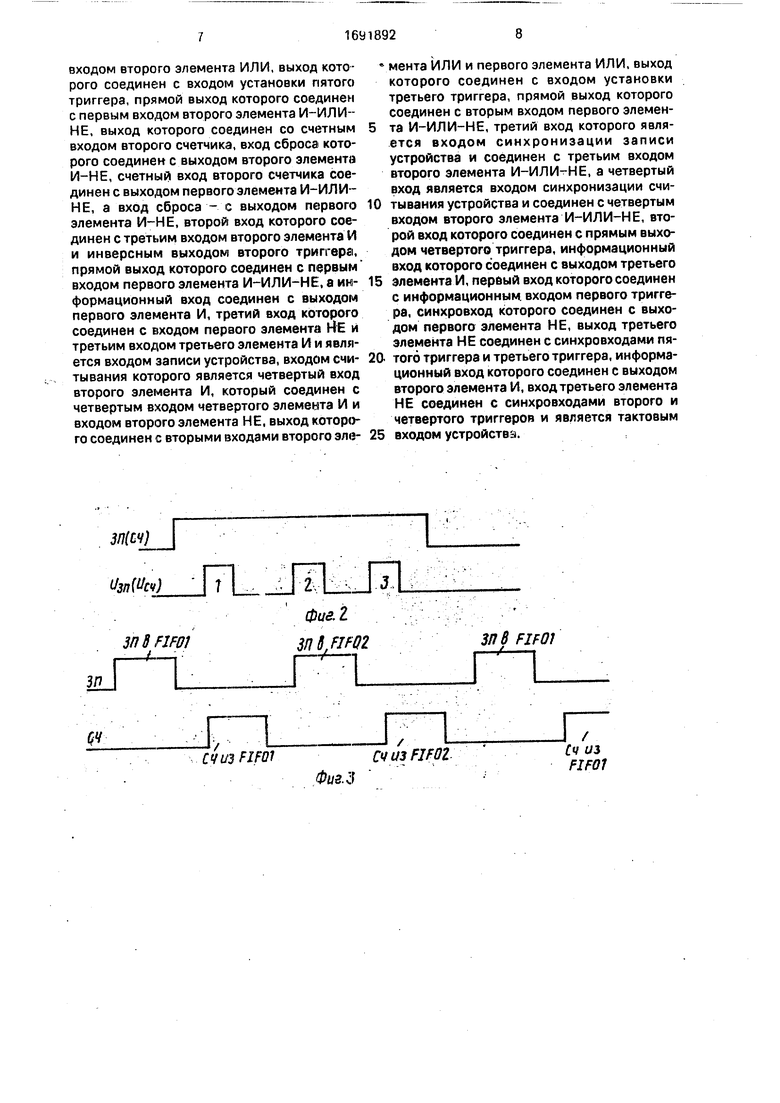

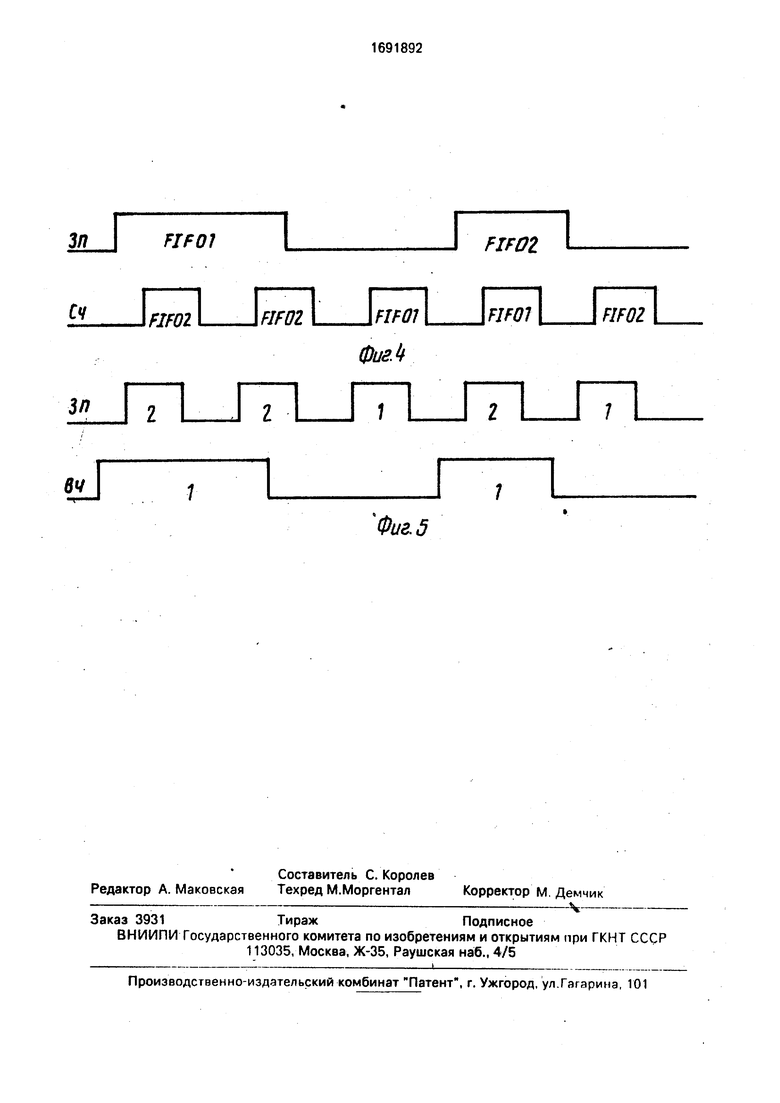

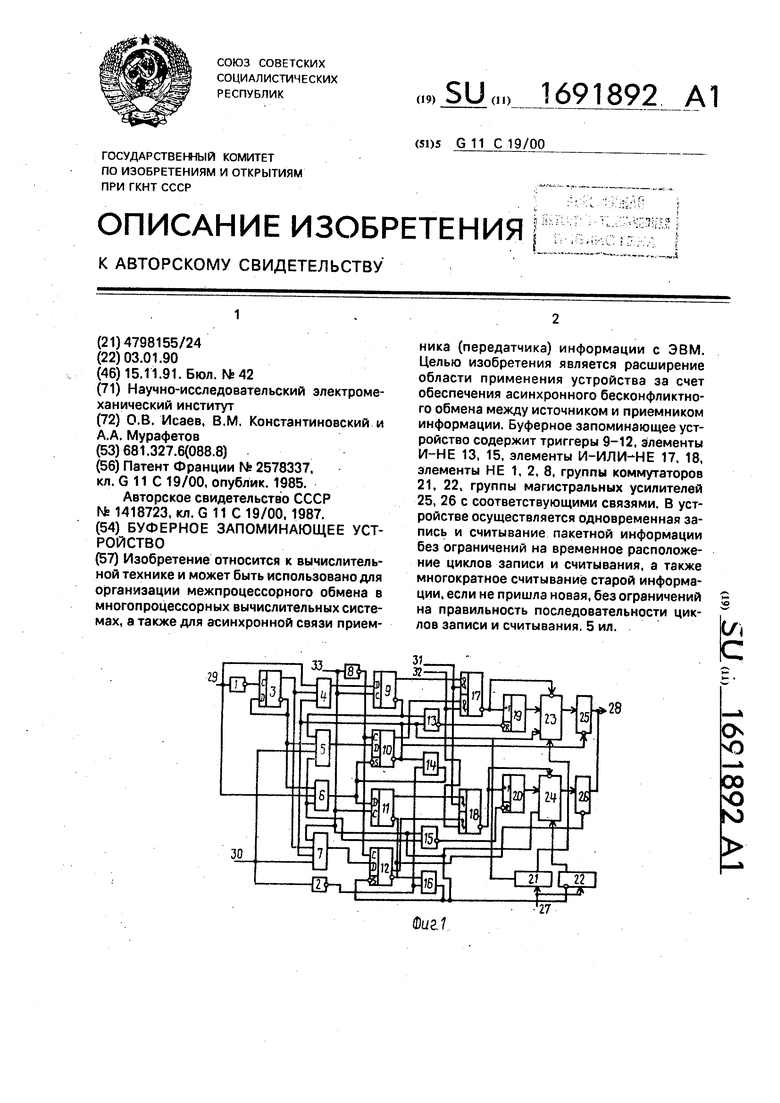

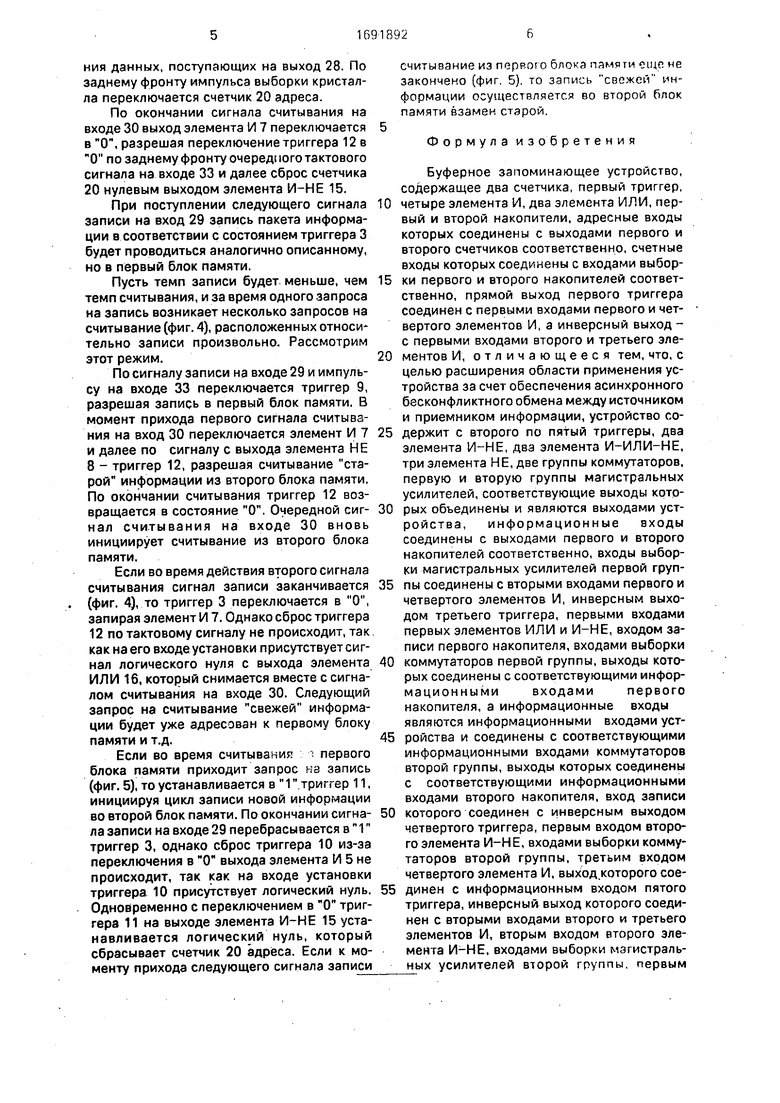

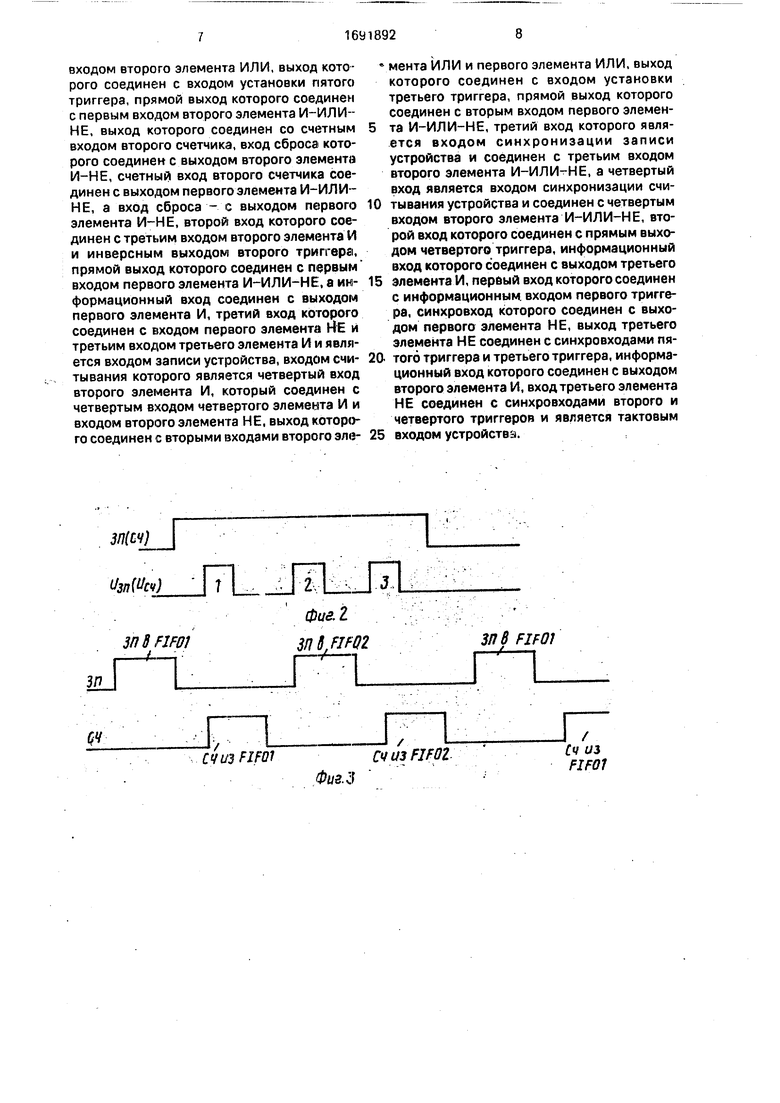

На фиг. 1 представлена структурная схема буферного запоминающего устройства; на фиг. 2-5 - временные диаграммы его работы.

Буферное запоминающее устройство содержит элементы НЕ 1,2, триггер 3, элементы 1/1 4-7, элемент НЕ 8, триггеры 9-12, элемент 1/1-НЕ 13, элемент ИЛИ 14, элемент И-НЕ 15, элемент ИЛИ 16, элементы И- ИЛИ-НЕ 17, 18, счетчики 19, 20 (адреса), группы коммутаторов 21, 22, накопители 23, 24, группы магистральных усилителей 25, 26. Пары элементов 19, 23 и 20, 24 образуют блоки памяти,

На фиг. 1 обозначены также информационные входы 27 и выходы 28 устройства, вход 29 записи, вход 30 считывания, вход 31 синхронизации записи, вход 32 синхронизации считывания и тактовый вход 33 устройства.

Запоминающее устройство (ЗУ) представляет собой двухпортовую память типа FIFO, причем по одному порту осуществляется только запись данных, а по другому - только считывание. Объем информации, передаваемой за один цикл обмена в режимах записи и считывания, одинаков и определяется принятой в вычислительной системе (ВС) длиной пакета. Особенностью работы устройства в составе ВС является то, что в зависимости от обстановки темп записи/считывания информации меняется и практически не привязан к темпу работы ЭВМ (или процессоров) системы. При таком обмене буферное ЗУ должно обладать следующими свойствами:

возможностью одновременной записи и считывания пакетной информации, в том числе не иметь ограничений на временное расположение циклов записи и считывания и их длительность;

возможностью многократного считывания старой информации, если не пришла новая (т.е. не должно быть ограничений на правильность последовательности циклов записи и считывания).

Буферное ЗУ работает следующим образом.

В исходном состоянии (нулевые сигналы на входе 29 записи и входе 30 считывания) триггеры 9-12 сигналами тактовой частоты (прямыми на входе 33 и инверсными с выхода элемента НЕ 8) устанавливаются в состояние логического нуля, причем с инверсных выходов триггеров 9-12 разрешающие единичные сигналы поступают на соответствующие входы элементов И 4-7.

0 На выходах элементов И-НЕ 13,15 устанавливаются сигналы логического нуля, сбрасывающие счетчики 19, 20 адреса в нулевое состояние. На выходах элементов И-ИЛИ- НЕ 17,18-логические единицы, коммутато5 ры 21, 22 и магистральные усилители 25, 26 отключены сигналами с инверсных выходов триггеров 9, 11, 10, 12 соответственно. Начальное состояние триггера 3 не имеет значения (для определенности примем его

0 нулевым).

При поступлении на вход 29 единичного сигнала записи (фиг. 3) переключается в Г элемент И 6, по переднему фронту очередного тактового сигнала на входе 33 пере5 ключается в единичное состояние триггер

11,разрешая работу счетчика 20 и коммутаторов 22. Одновременно на входе записи/считывания накопителя 24 устанавливается потенциал записи. Далее

0 по каждому импульсу записи (фиг. 2) на входе 31 (количество импульсов определяется длиной передаваемого пакета информации) на выходе элемента И-ИЛИ-НЕ 18 будет формироваться нулевой импульс выборки

5 кристалла для накопителя 24, инициирующий цикл записи данных во второй блок памяти, поступающих на входы 27. По заднему фронту импульса выборки кристалла (т.е. по положительному перепаду напряже0 ния) переключается счетчик 20 адреса.

По окончании сигнала записи на входе 29 переключается триггер 3, а выход элемента И 6 переключается в состояние логического нуля. Очередным импульсом

5 тактовой частоты триггер 11 обнуляется, переключая выход элемента И-НЕ 15 в О, который сбрасывает счетчик 20.

При поступлении на вход 30 единичного сигнала считывания (фиг. 3) переключается

0 в 1 элемент И 7, по заднему фронту очередного тактового сигнала на входе 33 переключается в единичное состояние триггер

12,разрешая работу счетчика 20 и магистральных усилителей 26. Далее по каждому

5 импульсу считывания (фиг. 2) на входе 32 (количество импульсов определяется длиной пакета информации) на выходе элемента И-ИЛИ-НЕ 18 будет формироваться нулевой импульс выборки кристалла для накопителя 24, инициирующий цикл считывания данных, поступающих на выход 28. По заднему фронту импульса выборки кристалла переключается счетчик 20 адреса.

По окончании сигнала считывания на входе 30 выход элемента И 7 переключается в О, разрешая переключение триггера 12 в О по заднему фронту очеред юго тактового сигнала на входе 33 и далее сброс счетчика 20 нулевым выходом элемента И-НЕ 15.

При поступлении следующего сигнала записи на вход 29 запись пакета информации в соответствии с состоянием триггера 3 будет проводиться аналогично описанному, но в первый блок памяти.

Пусть темп записи будет меньше, чем темп считывания, и за время одного запроса на запись возникает несколько запросов на считывание (фиг. 4), расположенных относи тельно записи произвольно. Рассмотрим этот режим.

По сигналу записи на входе 29 и импульсу на входе 33 переключается триггер 9, разрешая запись в первый блок памяти. В момент прихода первого сигнала считывания на вход 30 переключается элемент И 7 и далее по сигналу с выхода элемента НЕ 8 - триггер 12, разрешая считывание старой информации из второго блока памяти. По окончании считывания триггер 12 возвращается в состояние О. Очередной сиг- нал считывания на входе 30 вновь инициирует считывание из второго блока памяти.

Если во время действия второго сигнала считывания сигнал записи заканчивается (фиг. 4), то триггер 3 переключается в О, запирая элемент И 7. Однако сброс триггера 12 по тактовому сигналу не происходит, так как на его входе установки присутствует сигнал логического нуля с выхода элемента ИЛИ 16, который снимается вместе с сигналом считывания на входе 30. Следующий запрос на считывание свежей информации будет уже адресован к первому блоку памяти и т.д.

Если во время считывания -, первого блока памяти приходит запрос на запись (фиг. 5), то устанавливается в 1 триггер 11, инициируя цикл записи новой информации во второй блок памяти. По окончании сигна- ла записи на входе 29 перебрасывается в 1 триггер 3, однако сброс триггера 10 из-за переключения в О выхода элемента И 5 не происходит, так как на входе установки триггера 10 присутствует логический нуль. Одновременно с переключением в О триггера 11 на выходе элемента И-НЕ 15 устанавливается логический нуль, который сбрасывает счетчик 20 адреса. Если к моменту прихода следующего сигнала записи

считывание из первого блока памяти еще не закончено (фиг. 5), то запись свежей информации осуществляется во второй блок памяти взамен старой.

Формула изобретения

Буферное запоминающее устройство, содержащее два счетчика, первый триггер, четыре элемента И, два элемента ИЛИ, первый и второй накопители, адресные входы которых соединены с выходами первого и второго счетчиков соответственно, счетные входы которых соединены с входами выборки первого и второго накопителей соответственно, прямой выход первого триггера соединен с первыми входами первого и четвертого элементов И, а инверсный выход - с первыми входами второго и третьего элементов И, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения асинхронного бесконфликтного обмена между источником и приемником информации, устройство содержит с второго по пятый триггеры, два элемента И-НЕ, два элемента И-ИЛИ-НЕ, три элемента НЕ, две группы коммутаторов, первую и вторую группы магистральных усилителей, соответствующие выходы которых объединены и являются выходами устройства, информационные входы соединены с выходами первого и второго накопителей соответственно, входы выборки магистральных усилителей первой группы соединены с вторыми входами первого и четвертого элементов И, инверсным выходом третьего триггера, первыми входами первых элементов ИЛИ и И-НЕ, входом записи первого накопителя, входами выборки коммутаторов первой группы, выходы которых соединены с соответствующими инфор- мационными входами первого накопителя, а информационные входы являются информационными входами устройства и соединены с соответствующими информационными входами коммутаторов второй группы, выходы которых соединены с соответствующими информационными входами второго накопителя, вход записи которого соединен с инверсным выходом четвертого триггера, первым входом второго элемента И-НЕ, входами выборки коммутаторов второй группы, третьим входом четвертого элемента И, выход.которого соединен с информационным входом пятого триггера, инверсный выход которого соединен с вторыми входами второго и третьего элементов И, вторым входом второго элемента И-НЕ, входами выборки магистральных усилителей второй группы, первым

входом второго элемента ИЛИ, выход которого соединен с входом установки пятого триггера, прямой выход которого соединен с первым входом второго элемента И-ИЛИ- НЕ, выход которого соединен со счетным входом второго счетчика, вход сброса которого соединен с выходом второго элемента И-НЕ, счетный вход второго счетчика соединен с выходом первого элемента И-ИЛИ- НЕ, а вход сброса - с выходом первого элемента И-НЕ, второй вход которого соединен с третьим входом второго элемента И и инверсным выходом второго триггера, прямой выход которого соединен с первым входом первого элемента И-ИЛИ-НЕ, а информационный вход соединен с выходом первого элемента И, третий вход которого соединен с входом первого элемента ЙЕ и третьим входом третьего элемента И и является входом записи устройства, входом считывания которого является четвертый вход второго элемента И, который соединен с четвертым входом четвертого элемента И и входом второго элемента НЕ, выход которого соединен с вторыми входами второго элемента ИЛИ и первого элемента ИЛИ, выход которого соединен с входом установки третьего триггера, прямой выход которого соединен с вторым входом первого элемента И-ИЛИ-НЕ, третий вход которого является входом синхронизации записи устройства и соединен с третьим входом второго элемента И-ИЛИ-НЕ, а четвертый вход является входом синхронизации считывания устройства и соединен с четвертым входом второго элемента И-ИЛИ-НЕ, второй вход которого соединен с прямым выходом четвертого триггера, информационный вход которого соединен с выходом третьего

элемента И, первый вход которого соединен с информационным, входом первого триггера, синхровход которого соединен с выходом первого элемента НЕ, выход третьего элемента НЕ соединен с синхровходами пятого триггера и третьего триггера, информационный вход которого соединен с выходом второго элемента И, вход третьего элемента НЕ соединен с синхровходами второго и четвертого триггеров и является тактовым

входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для контроля оперативной памяти | 1986 |

|

SU1401520A2 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1226528A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Динамическое запоминающее устройство | 1987 |

|

SU1474739A1 |

| Динамическое запоминающее устройство с восстановлением информации | 1989 |

|

SU1689990A1 |

| Устройство для контроля оперативной памяти | 1984 |

|

SU1226535A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

Изобретение относится к вычислительной технике и может быть использовано для организации межпроцессорного обмена в многопроцессорных вычислительных системах, а также для асинхронной связи приемника (передатчика) информации с ЭВМ. Целью изобретения является расширение области применения устройства за счет обеспечения асинхронного бесконфликтного обмена между источником и приемником информации. Буферное запоминающее устройство содержит триггеры 9-12, элементы И-НЕ 13, 15, элементы И-ИЛИ-НЕ 17. 18, элементы НЕ 1, 2, 8, группы коммутаторов 21, 22, группы магистральных усилителей 25, 26 с соответствующими связями. В устройстве осуществляется одновременная запись и считывание пакетной информации без ограничений на временное расположение циклов записи и считывания, а также многократное считывание старой информации, если не пришла новая, без ограничений на правильность последовательности циклов записи и считывания. 5 ил. С/1 С о о 00 ю

3HSFIFOJ

4

фиг. 2. M&,flFQ2

ЗПв FIF01

зп

FIF01

J

FIFOZ

фигА

Фиг. 5

| СПОСОБ ВЫРАБОТКИ КОНСЕРВОВ "КАЛЬМАР, ФАРШИРОВАННЫЙ ДЕКОРАТИВНОЙ КАПУСТОЙ, ЛУКОМ И ЯЙЦОМ" | 2015 |

|

RU2578337C1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| Устройство буферной памяти | 1987 |

|

SU1418723A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-11-15—Публикация

1990-01-03—Подача