Изобретение относится к вычислительной технике, а именно к структурам цифровых вычислительных систем, и может быть использовано при построении многомашинных систем, работающих в масштабе реального времени

Цель изобретения - повышение быстродействия и упрощение устройства для сопряжения за счет автоматического управления установлением связи ЭВМ с данным устройством рабочими циклами ЭВМ при обращении к буферной памяти устройства.

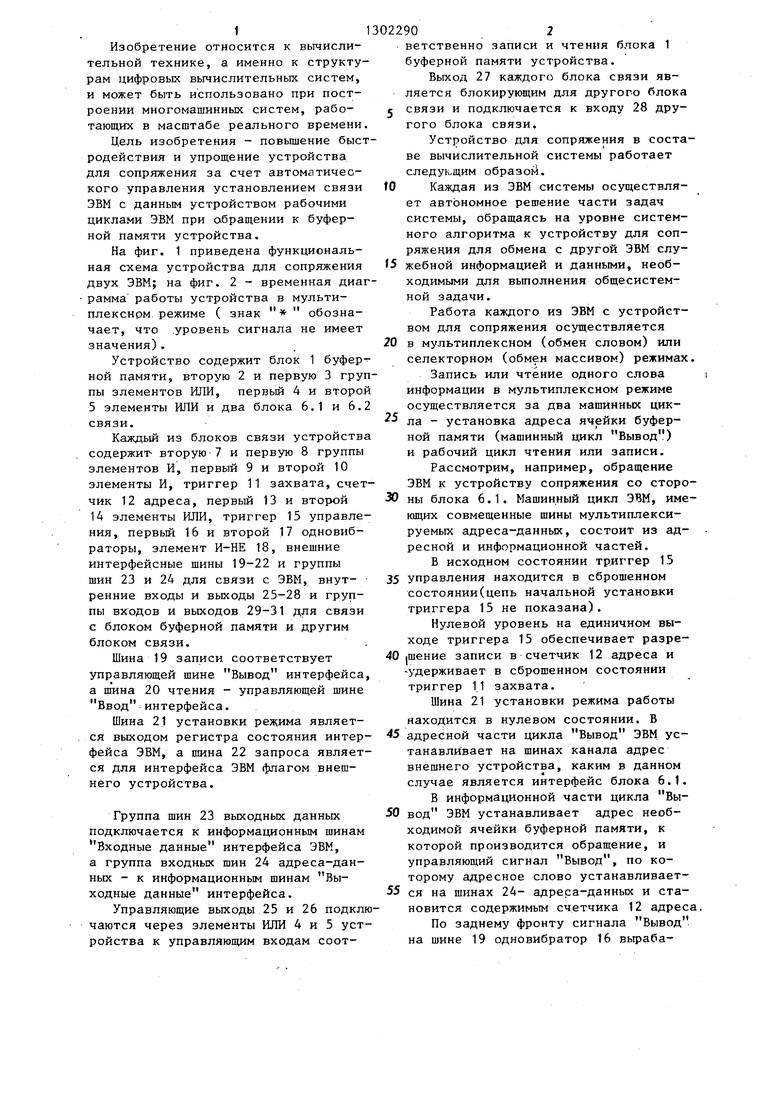

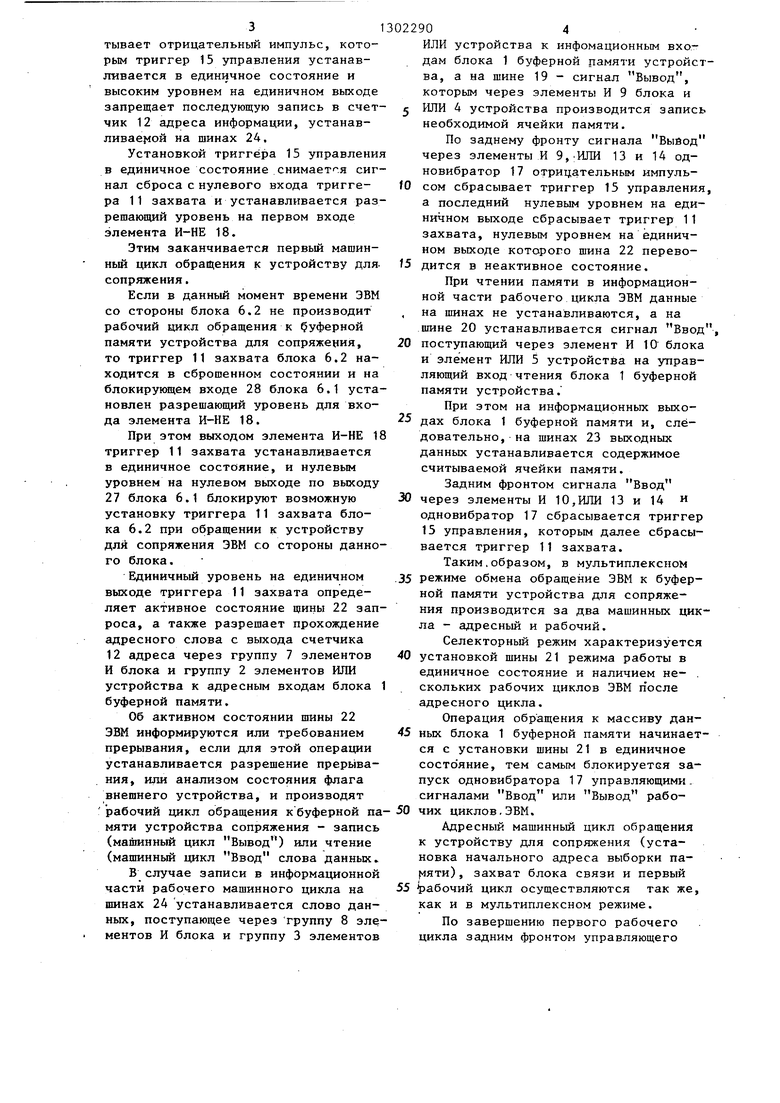

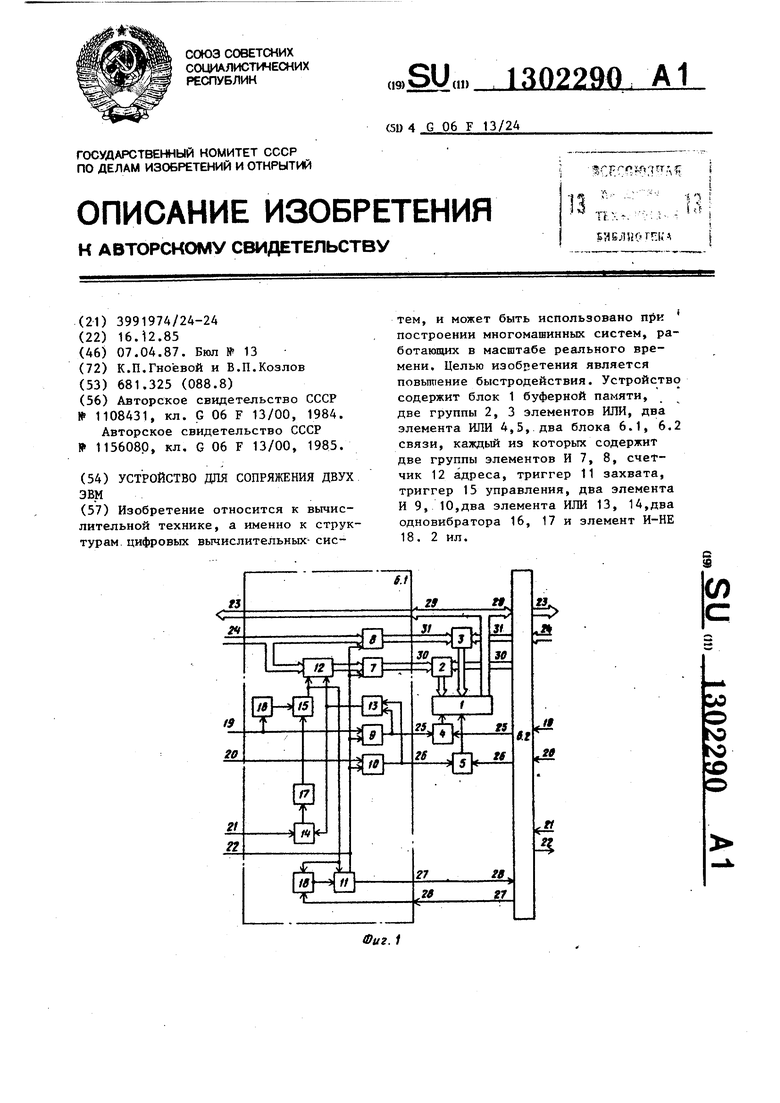

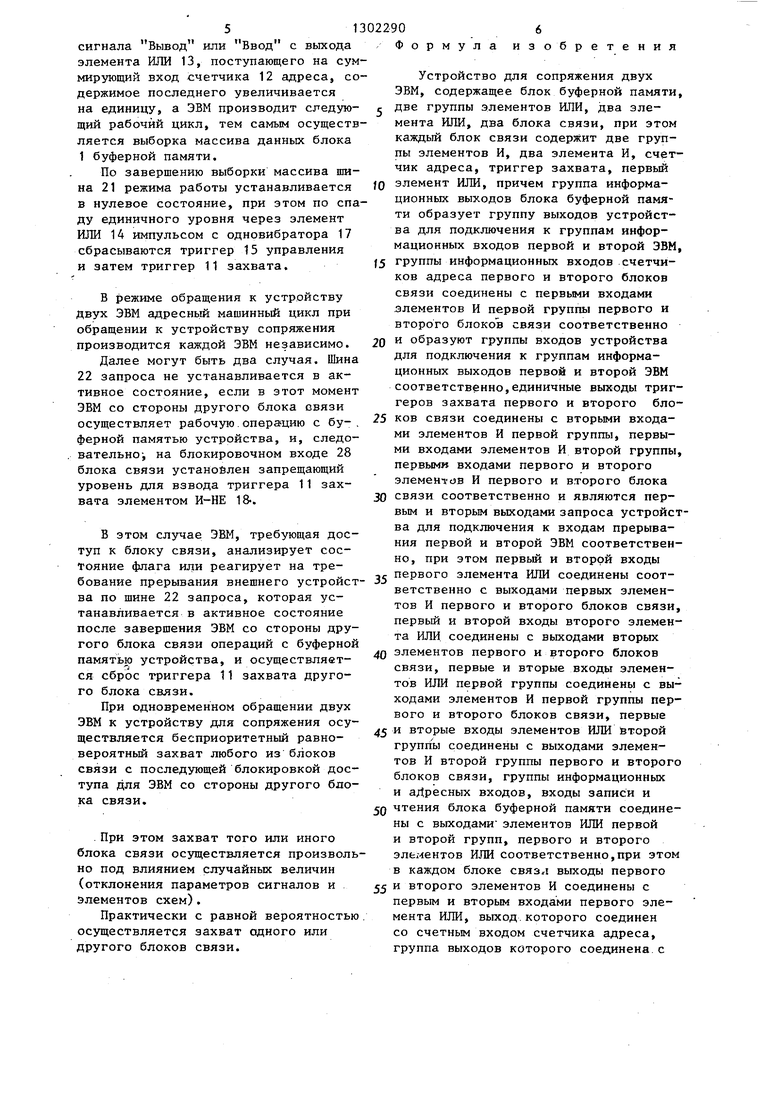

На фиг. 1 приведена функциональная схема устройства для сопряжения двух ЭВМ; на фиг. 2 - временная диаграмма работы устройства в мульти- плекснрм режиме ( знак обозначает, что .уровень сигнала не имеет значения).

Устройство содержит блок 1 буферной памяти, вторую 2 и первую 3 группы элементов ИЛИ, первый 4 и второй 5 элементы ИЛИ и два блока 6.1 и 6.2 связи.

Каждый из блоков связи устройства содержит- вторую 7 и первую 8 группы элементов И, первый 9 и второй 10 элементы И, триггер 11 захвата, счетчик 12 адреса, первый 13 и второй 14 элементы ИЛИ, триггер 15 управления, первый 16 и второй 17 одновиб- раторы, элемент И-НЕ 18, внешние интерфейсные шины 19-22 и группы шин 23 и 24 для связи с ЭВМ, внутренние входы и выходы 25-28 и группы входов и выходов 29-31 для связи с блоком буферной памяти и другим блоком связи.

Шина 19 записи соответствует упр авляющей шине Вывод интерфейса, а шина 20 чтения - управляющей шине Ввод интерфейса.

Шина 21 установки режима является выходом регистра состояния интерфейса ЭВМ, а шина 22 запроса является для интерфейса ЭВМ флагом внешнего устройства.

Группа шин 23 выходных данных подключается к информационным шинам Входные данные интерфейса ЭВМ, а группа входных шин 24 адреса-дан- ных - к информационным шинам Выходные данные интерфейса.

Управляющие выходы 25 и 26 подключаются через элементы ШШ 4 и 5 устройства к управляющим входам соответственно записи и чтения блока 1 буферной памяти устройства.

Выход 27 каждого блока связи является блокирующим для другого блока связи и подключается к входу 28 другого блока связи.

Устройство для сопряжения в составе вычислительной системы работает следующим образом.

Каждая из ЭВМ системы осуществляет автономное решение части задач системы, обращаясь на уровне системного алгоритма к устройству для сопряжения для обмена с другой ЭВМ слу- жебной информацией и данными, необходимыми для вьтолнения общесистемной задачи.

Работа каждого из ЭВМ с устройством для сопряжения осуществляется в мультиплексном (обмен словом) или селекторном (обмен массивом) режимах.

Запись или чтение одного слова информации в мультиплексном режиме осуществляется за два машинных цик- ла - установка адреса ячейки буферной памяти (машинный цикл Вывод) и рабочий цикл чтения или записи.

Рассмотрим, например, обращение ЭВМ к устройству сопряжения со сторо- ны блока 6.1. Машинный цикл ЭВМ, имеющих совмещенные шины мультиплексируемых адреса-данных, состоит из адресной и информационной частей.

В исходном состоянии триггер 15 управления находится в сброшенном состоянии(цепь начальной установки триггера 15 не показана).

Нулевой уровень на единичном выходе триггера 15 обеспечивает разре- |шение записи в счетчик 12 адреса и удерживает в сброшенном состоянии триггер 11 захвата.

Шина 21 установки режима работы

находится в нулевом состоянии. В адресной части цикла Вывод ЭВМ устанавливает на шинах канала адрес внешнего устройства, каким в данном случае является интерфейс блока 6.1. В информационной части цикла Вы- вод ЭВМ устанавливает адрес необходимой ячейки буферной памяти, к которой производится обращение, и управляющий сигнал Вывод, по которому адресное слово устанавливает- ся на шинах 24- адреса-данных и становится содержимым счетчика 12 адреса.

По заднему фронту сигнала Вывод на шине 19 одновибратор 16 вырабатывает отрицательный импульс, которым триггер 15 управления устанавливается в единичное состояние и высоким уровнем на единичном выходе запрещает последующую запись в счетчик 12 адреса информации, устанав- ливаеной на шинах 24.

Установкой триггера 15 управления в единичное состояние снимается сигнал сброса с нулевого входа триггера 11 захвата и устанавливается раз- решакндий уровень на первом входе элемента И-НЕ 18.

Этим заканчивается первый машинный цикл обращения к устройству для- сопряжения.

Если в данный момент времени ЭВМ со стороны блока 6.2 не производит рабочий цикл обращения к буферной памяти устройства для сопряжения, то триггер 11 захвата блока 6.2 находится в сброшенном состоянии и на блокирующем входе 28 блока 6.1 установлен разрешающий уровень для входа элемента И-НЕ 18.

При этом выходом элемента И-НЕ 1 триггер 11 захвата устанавливается в единичное состояние, и нулевым уровнем на нулевом выходе по выходу 27 блока 6.1 блокируют возможную установку триггера 11 захвата блока 6.2 при обращении к устройству дли сопряжения ЭВМ со стороны данного блока.

Единичный уровень на единичном выходе триггера 11 захвата определяет активное состояние щины 22 запроса, а также разрешает прохождение адресного слова с выхода счетчика 12 адреса через группу 7 элементов И блока и группу 2 элементов ИЛИ устройства к адресным входам блока буферной памяти.

Об активном состоянии шины 22 ЭВМ информируются или требованием прерывания, если для этой операции устанавливается разрешение прерывания, или анализом состояния флага внешнего устройства, и производят

рабочий цикл обращения к буферной па-50 чих циклов.ЭВМ.

мяти устройства сопряжения - запись (машинный цикл Вывод) или чтение (машинный цикл Ввод слова данных. В случае записи в информационной части рабочего машинного цикла на шинах 24 устанавливается слово данных, поступающее через группу 8 элементов И блока и группу 3 элементов

ИЛИ устройства к инфомационным входам блока 1 буферной памяти устройства, а на шине 19 - сигнал Вывод, которым через элементы И 9 блока и

ИЛИ 4 устройства производится запись необходимой ячейки памяти.

По заднему фронту сигнала Выйод через элементы И 9,:ИЛИ 13 и 14 од- новибратор 17 отрицательным импульсом сбрасывает триггер 15 управления, а последний нулевым уровнем на единичном выходе сбрасывает триггер 11 захвата, нулевым уровнем на единичном выходе которого шина 22 переводится в неактивное состояние.

При чтении памяти в информационной части рабочего цикла ЭВМ данные

на шинах не устанавливаются, а на

шине 20 устанавливается сигнал Ввод,

поступающий через элемент И 10 блока и элемент ИЛИ 5 устройства на управляющий вход чтения блока 1 буферной памяти устройства.

При этом на информационных выходах блока 1 буферной памяти и, следовательно, на шинах 23 выходных данных устанавливается содержимое считываемой ячейки памяти.

Задним фронтом сигнала Ввод

через элементы И 10,ИЛИ 13 и 14 и одновибратор 17 сбрасывается триггер 15 управления, которым далее сбрасывается триггер 11 захвата.

Таким,образом, в мультиплексном

режиме обмена обращение ЭВМ к буферной памяти устройства для сопряжения производится за два машинных цикла - адресный и рабочий.

Селекторный режим характеризуется

установкой шины 21 режима работы в единичное состояние и наличием не- . скольких рабочих циклов ЭВМ п осле адресного цикла.

Операция обращения к массиву данных блока 1 буферной памяти начинается с установки шины 21 в единичное состояние, тем самым блокируется запуск одновибратора 17 управляющими. сигналами Ввод или Вывод рабоАдресный машинный цикл обращения к устройству для сопряжения (установка начального адреса выборки памяти) , захват блока связи и первый 55 рабочий цикл осуществляются так же, как и в мультиплексном режиме.

По завершению первого рабочего цикла задним фронтом управляющего

сигнала Вывод или Ввод с выхода элемента ИЛИ 13, поступающего на суммирующий вход счетчика 12 адреса, содержимое последнего увеличивается на единицу, а ЭВМ производит следующий рабочий цикл, тем самым осуществляется выборка массива данных блока 1 буферной памяти.

По завершению выборки массива шина 21 режима работы устанавливается в нулевое состояние, при этом по спаду единичного уровня через элемент ИЛИ 14 импульсом с одновибратора 17 сбрасываются триггер 15 управления и затем триггер 11 захвата.

В режиме обращения к устройству двух ЭВМ адресный машинный цикл при обращении к устройству сопряжения производится каждой ЭВМ независимо.

Далее могут быть два случая. Шина 22 запроса не устанавливается в активное состояние, если в этот момент ЭВМ со стороны другого блока связи осуществляет рабочую.операцию с бу-. ферной памятью устройства, и, следовательно-, на блокировочном входе 28 блока связи установлен запрещающий уровень для взвода триггера 11 захвата элементом И-НЕ 18-.

Устройство для сопряжения двух ЭВМ, содержащее блок буферной памяти две группы элементов ИЛИ, два элемента ИЛИ, два блока связи, при этом каждый блок связи содержит две группы элементов И, два элемента И, счет чик адреса, триггер захвата, первый элемент ИЛИ, причем группа информационных выходов блока буферной памяти образует группу выходов устройства для подключения к группам информационных входов первой и второй ЭВМ 15 группы информационных входов счетчиков адреса первого и второго блоков связи соединены с первыми входами элементов И первой группы первого и второго блоков связи соответственно и образуют группы входов устройства для подключения к группам информационных выходов первой и второй ЭВМ соответственно,единичные выходы триг геров захвата первого и второго бло ков связи соединены с вторыми входами элементов И первой группы, первыми входами элементов И второй группы первыми входами первого и второго элемен1-ов И первого и второго блока связи соответственно и являются первым и вторым выходами запроса устройс ва для подключения к входам прерывания первой и второй ЭВМ соответственВ этом случае ЭВМ, требующая доступ к блоку связи, анализирует состояние флага или реагирует на тре„ эс первого элемента ИЛИ соединены соот- бование прерывания внешнего устроист- J-

но, при этом первый и второй входы

ветственно с выходами первых элементов И первого и второго блоков связи первый и второй входы второго элемента ШШ соединены с выходами вторых

ва по шине 22 запроса, которая устанавливается в активное состояние после завершения ЭВМ со стороны другого блока связи операций с буферной памятью устройства, и осуществляется сброс триггера 11 захвата другого блока свлзи.

При одновременном обращении двух ЭВМ к устройству для сопряжения осуществляется бесприоритетный равновероятный захват любого из блоков связи с последующей блокировкой доступа для ЭВМ со стороны другого блока связи.

. При этом захват того или иного блока связи осзтцествляется произвольно под влиянием случайных величин (отклонения параметров сигналов и элементов схем).

Практически с равной вероятностью. осуществляется захват одного или другого блоков связи.

Формула

6

3 о

бретения

Устройство для сопряжения двух ЭВМ, содержащее блок буферной памяти, две группы элементов ИЛИ, два элемента ИЛИ, два блока связи, при этом каждый блок связи содержит две группы элементов И, два элемента И, счетчик адреса, триггер захвата, первый элемент ИЛИ, причем группа информационных выходов блока буферной памяти образует группу выходов устройства для подключения к группам информационных входов первой и второй ЭВМ, 5 группы информационных входов счетчиков адреса первого и второго блоков связи соединены с первыми входами элементов И первой группы первого и второго блоков связи соответственно и образуют группы входов устройства для подключения к группам информационных выходов первой и второй ЭВМ соответственно,единичные выходы триггеров захвата первого и второго блоков связи соединены с вторыми входами элементов И первой группы, первыми входами элементов И второй группы, первыми входами первого и второго элемен1-ов И первого и второго блока связи соответственно и являются первым и вторым выходами запроса устройства для подключения к входам прерывания первой и второй ЭВМ соответствен0

5

0

но, при этом первый и второй входы

эс первого элемента ИЛИ соединены соот- J-

ветственно с выходами первых элементов И первого и второго блоков связи, первый и второй входы второго элемента ШШ соединены с выходами вторых

0 элементов первого и второго блоков связи, первые и вторые входы элементов ИЛИ первой группы соединены с выходами элементов И первой группы первого и второго блоков связи, первые

j5 и вторые входы элементов ИЛИ второй группы соединены с выходами элементов И второй группы первого и второго блоков связи, группы информационных и а; ресных входов, входы записи и

5Q чтения блока буферной памяти соединены с выходами элементов ИЛИ первой и второй групп, первого и второго элементов ИЛИ соответственно,при этом в каждом блоке связи выходы первого

55 и второго элементов И соединены с первым и вторым входами первого элемента ИЛИ, выход.которого соединен со счетным входом счетчика адреса, группа выходов которого соединена, с

вторыми входами элементов И второй группы, отличающееся тем, что, с цглью повьппения быстродействия, в каждый блок связи устройства введены триггер управления, второй элемент ИЛИ, элемент И-НЕ, два одно- вибратора, при этом вторые входы первых элементов И первого и второго блоков связи соединены с входами первых одновибраторов первого и второго блоков связи и являются первым и вторым входами записи устройства для подключения, к выходам первой и второй ВМ соответственно, вторые входы вторых элементов И первого и второго . блоков связи являются первыми и вторыми входами чтения устройства для подключения к выходам ввода первой и второй ЭВМ соответственно, первые 9ХОДЫ вторых элементов ИЛИ первого и второго блоков связи являются первым и вторым входами установки

и HUM

StM Atpfttf.

режима работы устройства для подключения к управляющим выходам первой и второй ЭВМ соответственно, при этом нулевые выходы триггера захвата первого и второго блоков связи соединены, с первыми входами элементов И-НЕ второго и первого блоков связи соответственно, причем в каждом блоке единичный вход т риггера захвата соединен с выходом элемента И-НЕ, второй вход которого соединен с нулевым входом триггера захвата, входом записи счетчика адреса и выходом триггера управления, нулевой вход которого соединен с выходом второго одновибратора, вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с выходом первого элемента ИЛИ, выход первого одновибратора соединен с единичным входом триггера управления.

1-й цшгп

.

Редактор И.Николайчук

фц.

Составитель С.Пестмал

Техред А.Кравчук Корректор Т.Колб

Заказ 1218/49Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухпортовое устройство сопряжения в вычислительной системе | 1982 |

|

SU1156080A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1987 |

|

SU1439612A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1988 |

|

SU1532939A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1462336A1 |

| Устройство для сопряжения двух электронных вычислительных машин (эвм) | 1984 |

|

SU1187172A1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

Изобретение относится к вычислительной технике, а именно к структурам, цифровых вычислительных- систем, и может быть использовано при построении многомашинных систем, работающих в масштабе реального времени. Целью изобретения является повышение быстродействия. Устройство содержит блок 1 буферной памяти, две группы 2, 3 элементов ИЛИ, два элемента ИЛИ 4,5,. два блока 6.1, 6.2 связи, каждый из которых содержит две группы элементов И 7, 8, счеТ- чик 12 адреса, триггер 11 захвата, триггер 15 управления, два элемента И 9, 10,два элемента ИЛИ 13, 14,два одновибратора 16, 17 и элемент И-НЕ 18. 2 ил. (Л

| Устройство для сопряжения вычислительных машин в многопроцессорной вычислительной системе | 1983 |

|

SU1108431A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Двухпортовое устройство сопряжения в вычислительной системе | 1982 |

|

SU1156080A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-07—Публикация

1985-12-16—Подача