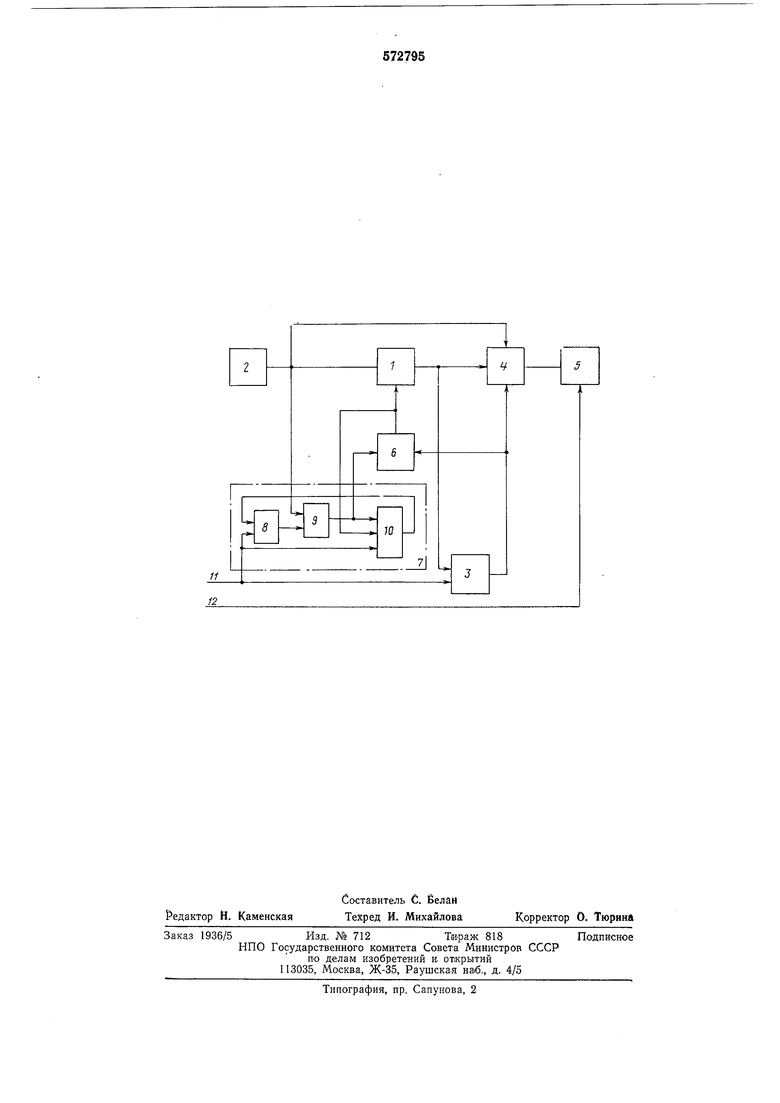

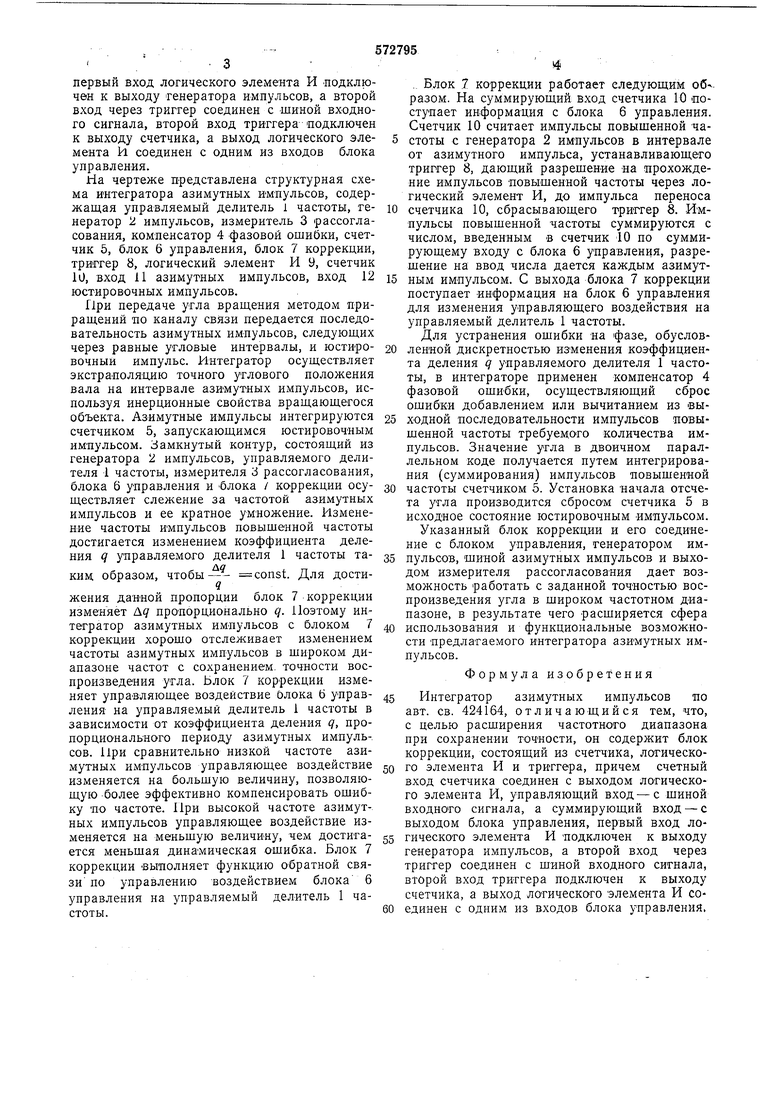

первый вход логического элемента И .подключен к выходу генератора импульсов, а второй вход через триггер соединен с шиной входного сигнала, второй вход триггера подключен к выходу счетчика, а выход логического элемента И соединен с одним из входов блока управления. На чертеже представлена структурная схема интегратора азимутных импульсов, содержащая управляемый делитель 1 частоты, генератор 2 импульсов, измеритель 3 рассогласования, компенсатор 4 фазовой ошибки, счетчик 5, блок 6 управления, блок 7 коррекции, триггер 8, логический элемент И 9, счетчик 10, вход 11 азимутных импульсов, вход 12 юстировочных импульсов. При передаче угла врашения методом приращений по каналу связи передается последовательность азимутных импульсов, следующих через равные угловые интервалы, и юстпровочныи импульс. Интегратор осуществляет экстраполяцию точного углового положения вала на интервале азимутных импульсов, используя инерционные свойства вращающегося объекта. Азимутные импульсы интегрируются счетчиком 5, запускающимся юстировочным импульсом. Замкнутый контур, состоящий из генератора 2 импульсов, управляемого делителя 1 частоты, измерителя 3 рассогласования, блока 6 управления и блока / коррекции осуществляет слежение за частотой азимутных импульсов и ее кратное умножение. Изменение частоты импульсов повышенной частоты достигается изменением коэффициента деления д управляемого делителя 1 частоты таким образом, чтобы- - const. Для достижения данной пропорции блок 7 коррекции изменяет Д пропорционально q. Поэтому интегратор азимутных импульсов с блоком 7 коррекции хорошо отслеживает изменением частоты азимутных импульсов в широком диапазоне частот с сохранением, точности воспроизведения угла. Блок 7 коррекцни изменяет управляющее воздействие Олока 6 управления на управляемый делитель 1 частоты в завпсимости от коэффициента деления q, пропорционального периоду азимутных импульсов. При сравнительно низкой частоте азимутных импульсов управляющее воздействие изменяется на большую величину, позволяющую более эффективно компенсировать ошибку ПО частоте. При высокой частоте азимутных импульсов управляющее воздействие изменяется на меньшую величину, чем достигается меньшая динамическая ошибка. Блок 7 коррекции Выполняет функцию обратной связи по управлению воздействием блока 6 управления на управляемый делитель 1 частоты. . Блок 7 коррекции работает следующим об-разом. На суммирующий вход счетчика 10 поступает информадия с блока 6 управления. Счетчик 10 считает импульсы повышенной частоты с генератора 2 импульсов в интервале от азимутного импульса, устанавливающего триггер 8, дающий разрешение на прохождение импульсов повышенной частоты через логический элемент И, до импульса переноса счетчика 10, сбрасывающего триггер 8. Импульсы повышенной частоты суммируются с числом, введенным в счетчик 10 по суммирующему входу с блока 6 управления, разрешение на ввод числа дается каждым азимутным импульсом. С выхода блока 7 коррекции поступает информация на блок 6 управления для изменения управляющего воздействия на управляемый делитель 1 частоты. Для устранения ошибки на фазе, обусловленной дискретностью изменения коэффициента деления q управляемого делителя 1 частоты, в интеграторе применен компенсатор 4 фазовой ошибки, осуществляющий сброс ошибки добавлением или вычитанием из Выходной последовательности импульсов повышенной частоты требуемого количества импульсов. Значение угла в двоичном параллельном коде получается путем интегрирования (суммирования) импульсов повышенной частоты счетчиком 5. Установка начала отсчета угла производится сбросом счетчика 5 в исходное состояние юстировочным импульсом. Указанный блок коррекции и его соединение с блоком управления, генератором импульсов, шиной азимутных импульсов и выходом измерителя рассогласования дает возможность работать с заданной точностью воспроизведения угла в широком частотном диапазоне, в результате чего расширяется сфера использования и функциональные возможности предлагаемого интегратора азимутных импульсов. Формула изобретения Интегратор азимутных импульсов по авт. св. 424164, отличающийся тем, что, с целью расширения частотного диапазона при сохранении точности, он содержит блок коррекции, состоящий из счетчика, логического элехмента И и триггера, причем счетный вход счетчика соединен с выходом логического элемента И, управляющий вход-с шиной входного сигнала, а суммируюший вход с выходом блока управления, первый вход логического элемента И подключен к выходу генератора импульсов, а второй вход через триггер соединен с шиной входного сигнала, второй вход триггера подключен к выходу счетчика, а выход логического элемента И соединен с одним из входов блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор азимутных импульсов | 1977 |

|

SU691877A2 |

| Интегратор азимутных импульсов | 1977 |

|

SU732907A1 |

| Интегратор азимутных импульсов | 1976 |

|

SU646348A2 |

| Интегратор азимутных импульсов | 1977 |

|

SU736123A2 |

| Интегратор импульсов | 1978 |

|

SU750508A1 |

| Устройство для интегрирования частотно-импульсных сигналов | 1984 |

|

SU1160444A1 |

| Преобразователь угла поворота вала в код | 1976 |

|

SU661589A1 |

| Интегратор импульсов | 1977 |

|

SU714414A1 |

| ИНТЕГРАТОР АЗИМУТНЫХ И/\\ПУЛЬСОВ | 1972 |

|

SU424164A1 |

| Следящий умножитель частоты | 1977 |

|

SU732866A1 |

Авторы

Даты

1977-09-15—Публикация

1975-12-01—Подача