входы сброса первого и второго триггеров соединены соответственно с выходами признаков начала и конца прерывания регистра микрокоманд, выход регистра адреса возврата соединен соответственно с первыми входами элементов И пятой группы, вторы входы которых соединены с вьпсодом признака конца прерывания регистра микрокоманд, выходы элементов И пятой группы соединены соответствен13 но с пятыми входами элементов ИЛИ первой группы, четвертыми входами элементов ИЛИ второй группы и третьими входами элементов ИЛИ третьей группы, выход второго элемента И четвертой группы соединен с вторыми входами элементов И второй группы, выходы последунхцих элементов И четвертой группы соединены с вторыми входами соответствующих элементов И-ИЛИ группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления памятью микрокоманд | 1981 |

|

SU970378A1 |

| Программируемый контроллер | 1988 |

|

SU1612276A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1376084A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1481759A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПАМЯТЬЮ МИКРОКОМАНД, содержащее регистр признаков перехода, регистр кода операций, две группы элементов ИЛИ, две группы элементов И, группу элементов И-ИПИ, регистр микрокоманд, память микрокоманд, выход которой соединен с информационным входом регистра микрокоманд, адресный вьгкод которого соединен с первыми входами элементов И первой группы, выходы которых подключены соответственно к первым входам элементов ИЛИ первой и второй групп, выходы которьгх подключены к первой группе адресных входов памяти микрокоманд, выход регистра признака перехода подключен к первым входам элементов И-ИЖ группы, выходы которых соединены с вторыми входами элементов ИЛИ первой группы, третьи входы которых и вторые входы элементов ИЛИ второй группы соединены соответственно с выходами элементов И второй группы, первые входы кото- рьи соединены с выходом регистра кода операций, счнхровход регистра микрокоманд соединен с входом тактовых импульсов устройства, выход микроопераций регистра микрокоманд :подключен к выходу устройства. отличающееся тем, что, с целью повьшения быстродействия, устройство содержит третью группу элементов ИЛИ, третью, четвертую и пятую группы элементов И, элемент И, два триггера, регистр признаков прерывания, регистр адреса возврата, причем выход регистра признаков прерывания подключен к первым входам элементов И третьей группы, выходы которых соединены соответственно с первыми входами элементов ИЛИ третьей группы, третьими входами элементов ИЛИ второй группы и четвертыми входами элементов ИЛИ первой группы, I вторые входы элементов И третьей /) группы подключены к прямому выходу первого триггера, инверсный выход которого к первым входам элементов И четвертой группы, вторые входы которых подключены соответственно к выходу признаков регистра микрокоманд, выход первого элемента И четвертой группы соединен с вторыми входами элементов И первой группы, С0 4 выходы которых подключены соответственно к вторым входам элементов ИЛИ третьей группы, выходы которых под09 ключены к второй грзшпе адресных входов памяти микрокоманд, адресный выход которой соединен с информационным входом регистра адреса возврата, управляющий вход которого сое динен с выходом элемента И, первый вход которого соединен с входом тактовых импульсов устройетв-а и с синхро- входами первого и второго триггеров, единичные входы которых соединены с : запроса прерывания устройства, второй вход элемента И соединен с инверсным выходом второго триггера.

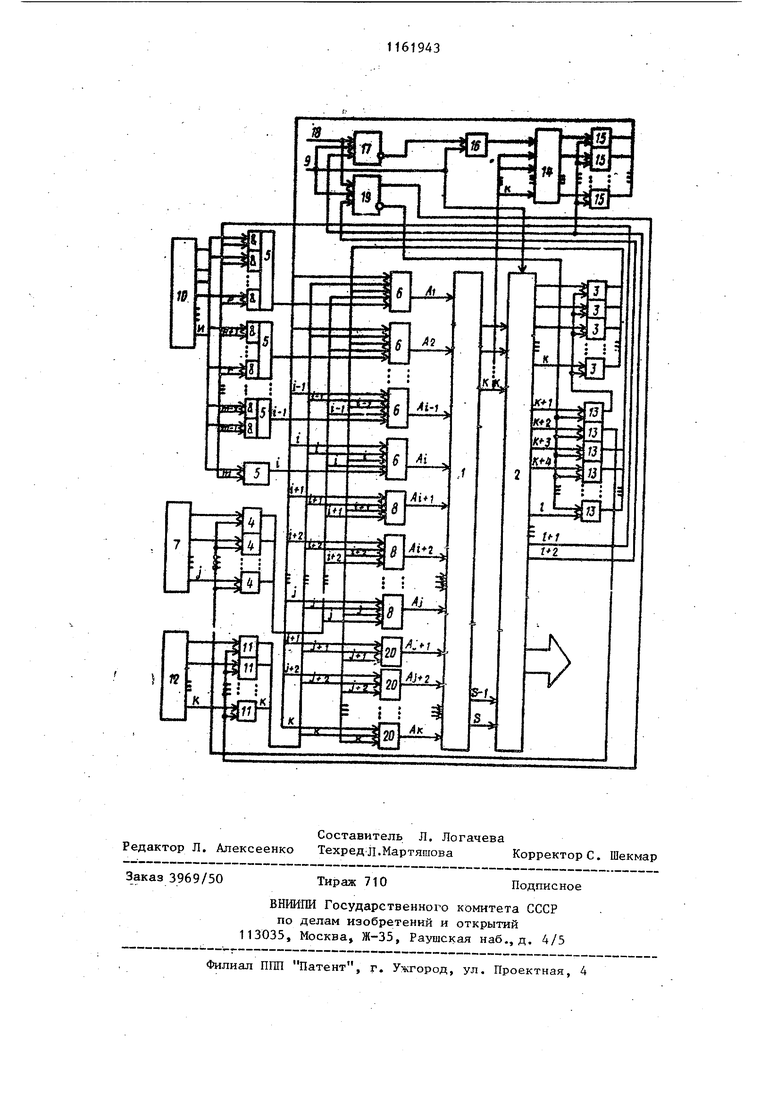

Изобретение относится к цифровой вычислительной технике и может быть использовано в устройствах управлени памятью микрокоманд. Цель изобретения - повышение быстродействия.На чертеже представлена структурная схема предлагаемого устройства. Устройство содержит память 1 микрокоманд, регистр 2 микрокоманд, первую и вторую группы элементов И 3 и 4, группу элементов И-ИЖ 5, первую группу элементов 11ПИ 6,регистр 7 кода операций, вторую группу элементов ИЛИ 8, вход 9 тактовых импуль сов устройства, регистр 10 признаков перехода, третью группу элементов И 11, регистр 12 признаков прерывания, четвертую группу элементов И 13, регистр 14 адреса возврата, пятую группу элементов И 15, элемент И 16 триггер 17, вход 18 запроса прерывания устройства, .триггер t9, третьи группу элементов ИЛИ 20. Предлагаемое устройство может работать в следующих режимах: естественная адресация; ветвление по отдельным признакам; ветвление по группе признаков; выход на код опера ции; повторный выход на код операции Каждый из указанных режимов может прерываться на уровне микрокоманд с запоминанием адреса прерванной МК текущей программы и восстановлением его после обслуярпвания прерывания. При естественной адресации адрес следующей МК в явном виде записан в преДьщущей Это не означает, что он формируется по какому-то закону. например, добавлением единицы к адресу предыдущих МК, он Может быть произвольнь1м и задается первыми разрядами МК. Для этого режима необходимо, чтобы (К+1)-й разряд Ж принял значение,, равное единице, а остальные управляющие разряды с (К+2) до Е-ГО значения, равные нулю. Данное условие задается при программировании. При помощи режима естественной . адресации задаются адреса большинства МК, т.е. это наиболее часто встречающийся режим. При работе в режиме ветвления по отдельным признакам младший разряд следующей МК определяется выбранным признаком из регистра 10 признаков, снимаемым при помощи единицы в одном из Р управляющих разрядов, подаваемым на входы первого элемента И-ИЛИ 5 группы. Остальные разряды адреса следующей МК задаются при помощи К разрядов предыдущей МК, как и при работе в режиме естественной адресации. При этом первый разряд МК должен быть равным нулю, . чтобы он не маскировал собой обрабатьшающий признак, (К+1)-й разряд равен единице, а остальные управляющие разряды, т.е. от (К+2) до С-го должны быть равны нулю, кроме одного из них, который определяет обрабатываемый признак. При этом адреса ветвей, на которые выходит микропрограмма (МП), могут находиться на любом месте памяти без каких-либо ограничений, что решает проблему равномерного и полного заполнения 3 блока 1 памяти, т.е. емкость исполь зуется полностью. Ветвление по группе признаков позволяет с одной МК выходить на несколько ветвей МП, что значительно ускоряет процесс вычислений, так как позволяет обрабатьшать сразу несколько признаков при помощи всег одной МК. При отсутствии такого реж ма пришлось бы обрабатывать каждый признак в отдельности, что привело бы к потерям времени и удлинению МП Обработка нескольких признаков необходима при выполнении многих задач, в частности задачи выработки адреса операнда при обращении к оперативному запоминающему устройст ву (ОЗУ). Обычно адрес операнда вычисляется как сумма адресного сме щения, задаваемого по команде и содержимого одного или нескольких индексных регистров. Широкое внедре ние индексных регистров в ЭВМ тре-. бует задан};е их номеров в команде при помощи кода признаков. В предла гаемом устройстве выход на МП, обра ботка требуемого индексного регистр из некоторого их числа .осуществляет в один прием, что резко повышает скорость вычислений, т.е. в конечном счете производительность всей ЭВМ, в которой применяется данное устройство. Большая гибкость указанного режи позволяет применять его в различных устройствах и решать разнообразные задачи без изменения схем. Например указанный режим оказьш ется весьма эффективным при выпол,.:ении команд типа условного перехода, в которьк кроме кода операции используется большое поле дрполнительных признаков, определякщих тип условного перехода. .Режим ветвления по группам признаков осуществляется подачей соответствующих признаков на вход адрес памяти МК в качестве адресньгх разрядов. Признаки поступают на вход блока 1 памяти через элементы И-ИЛИ при появлении единиц в соответствукщих управляющих разрядах (К+2) до -го МК. При этом поле кода признаков может быть переменным от i разрядов до одного. Остальные разряды адреса блока 1 памяти МК при этом можно задавать произвольно при 434 помощи первых К разрядов МК, причем (К+1 )-й разряд МК должен быть равным единице. Выбранный метод адресации, кроме увеличения быстродействия, значительно упрощает программирование, что, в конечном итоге, ускоряет разработку матобеспечения. Режим вьссода на код операции служит для выхода на МК обработки команд и не требует особых пояснений. Необходимо только указать, что в этом случае первые j разрядов адреса равны коду операции команд-ы, а осталь ные - нулю. В режиме повторного выхода на код операции разряды адреса МК от (J+1) до К-го определяется соответствующими разрядами МК. Указанный режим необходим для перехода от частей МП, общих для нескольких команд, к частям индивидуальным для каждой команды. В исходном состоянии устройство работает в одном из перечисленных режимов. Триггеры 17 и 19 находятся в нулевых состояниях, на регистре 14 записывается текущий возвратный . К-разрядный адрес Ж. Однако его содержание не проходит на элементы ИЛИ через закрытые элементы И 15. Содержание регистра 12 также не проходит на сборку через закрытые элементы ИГ. Адресные разряды от А до Ац-го формируются сборкой от элементов ИЗ, 4, 5 и 13. Микропрограммные (L+D и (+2)-й разряды записаны в МП нулями, а (К+О-й разряд - единицей. Поступивший на шину 18 запрос прерьшания совместно с тактовым сигналом 9 перебрасывает J-К-триггеры 17 и 19 в единичные состояния, после чего инверсный выход триггера 17 запрещает прохождение сигнала 9 через элемент И 16 на разрешающий вход регистра 14. При этом в нем остается возвратный адрес Ж, по которому необходимо возвратиться к исполнению MIC после обслуживания прерывания.г, Инверсный выход триггера 19, находящийся в нулевом состоянии, снимает ра,зрешение с элементов И 13. При этом выходные разряды регистра 2 МК от 1 до (К+4)-го и выходные разряды регистра 7 не поступают на злементы ИЛИ 6, 3 и 20. 51 npHitoft выход триггера 19, находящийся в единичном состоянии, разрешает прохоадение содержимого регистра 12 признаков прерывания через элементы И 11, ИЛИ 20 на вход блока 1 памяти, которые являются начальным адресатом МК обслуживания прерывания. (1+1)-и разряд регистра 2 в пер вой МК обслуживания прерывания, назначенный программой равным единице, совместно с сигналом 9 устанавливает триггер 19 в исходное нулевое состояние по заданному фронту. При этом с второй МК обслуживания преры вания на элементы ИЛИ 6, 8 и 20 раз решается прохождение содержимых ре3бгистров 7 и 10, отключаются выходы регистра 12. Далее выполняются МК обслуживания прерьгаания. В заключительной МК во всех разрядах МК программно записываются нули, кроме (f+2)-ro разряда, в который записывается единица. Единица (t+2)ro разряда открывает элементы И 15. При этом адрес МК прерванной микропрограммы, записанный ранее в регистре 14, поступает на вход блока 1 памяти через элементы ИШ 6,8, 20 (нулевые выходы разрядов от 1 до (+1)-го последней Ж не оказывают влияния на вход блока 1 памяти). Далее продолжается прерванная работа.

| Процессор | 1974 |

|

SU526902A1 |

| Устройство для управления памятью микрокоманд | 1981 |

|

SU970378A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-15—Публикация

1984-01-04—Подача