Изобретение относится к цифровой вычислительной технике и может быть использовано в устройствах для управ ления памятью в цифровых вычислитель ных управляющих системах. Известны устройства для управления памятью команд, расположенных в постоянных запоминающих блоках цифро вых вычислительных управляющих ма шин l . Это устройство содержит постоянный блок памяти и блок полупостоянной памяти. На этапе отладки програм блок полупостояниой памяти замещает один из блоков постоянной памяти, т.е. информация, записанная в блоке постоянной памяти в определенном положении коммутатора замещается содер жимым блока полупостоянной памяти. Точность указания массивов замещения в данном устройстве определяется рагз рядностью регистра и, в ряде случаев является недостаточной. Наиболее близким по технической сущности является устройство отладки программ для постоянного запоминающего устройства, содержащее запоминающий блок без разрушения информации, первые входы которого подключены к выходам распределителя, первый вход которого через блок управления соединен с шиной обращения, подключенной на вход постоянного блока памяти, вторые входы которого связаны со вторыми входами запоминающего блока без разрушения информации и через блок , формирования адреса - с адресными шинами, подключенными через блок формирования адреса участка - со вторыми входами распределителя, третьи входы которого соединены с блоком регистров установки (РУ). Кроме того, устройство содержит блок ввода вывода связанный с выходами постоянного блока памяти, блока памяти без разрушения информации. В данном устройстве выбор массивов замещения, т.е.

точность указания массивов информации за счет применения блока регистг ров установки повышается, поскольку массив запоминающего блока без разрушения информации разбивается на участки по количеству регистров установки и каждый участок адресуется самостоятельно.

Однако при отладке программ задач ЭВМ точность указания массивов информации, обеспечиваемая данным устроит стеом, является недостаточной. Процесс записи информации в запоминающий блок памяти без разрушения информации осуществляется в два этапа. На первом этапе производится его заполнение массивами исходной информации. На втором этапе выполняется корректировка записанной информации. Учитывая то, что на заключительном этапе отладки программ корректуры носят одиночный характер на фоне массивов отлаженной информации, замещение информации большими массивами является нецелесообразным.

Целью изобретения является повышение точности подмены зон блоков постоянной памяти зонами Запоминающего блока разрушения информации.

Поставленная цель достигается тем что в устройство для уп| авления памятью, содержащее блок сравнения, блок постоянной памяти, первь1й и второй блоки фориирования адреса регистр и блок вывода, причем вь1ход блока вывода является выходом устройства, адресный вход устройства соединен со входами первого и второго блоков формирования адреса, выход первого блока формирования адреса соединен С первыми входами памяти и блока постоянной памяти, управляющий вход устройства соединен со вторым входом блока постоянной памяти и с первым входом блока сравнения, выход которого соединен со вторым входом памяти, выход второго блока формирования адреса соединен с третьим входом блока постоянной памяти и со вторым входом блока сравнения, третий вход которого соединен с выходом регистра, введены первый, второй, третий и четвертый элементы И, триггер, одноразрядный блок памяти и элемент задержки, причем выход первого блока формирования адреса и выход блока сравнения соединены соответственно с первым |и вторым входами одноразрядного бло173 памяти, выход которого соединен с первым входом триггера, выход памяти соединен с первыми входами первого элемента И, выход которого соединен с первым входом блока вывода, второй вход которого соединен с выходом второго элемента И, выход блока постоянной памяти соединен с первым входом второго элемента И, второй вход КОТОРОГО соединен с выходом третьего элемента И,тактовый вход устройства соединен с первыми входам и треть его и четвертого элементов И, и со входом элемента задержки, выхо которого соединен со вторым входом триггерапервый и второй выходы которого соединены соответственно со, вторыми входами третьего и четвертого элементов И, выход четвертого элемента И соединен со вторым входом первого элемента И.

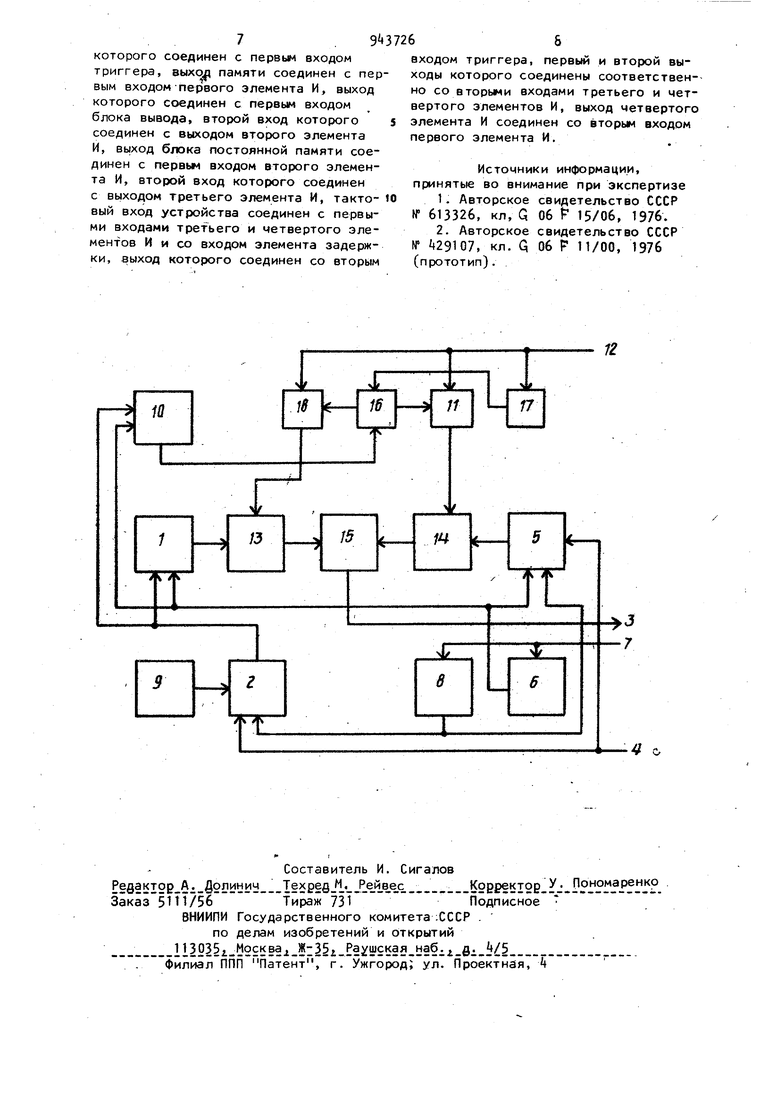

Блок-схема устройства для управления памятью представлена на чертеже.

Устройство содерекит память 1, вторые входы которой подключены к выходу блока сравнения 2, выход 3 устройства, вход блока 2 сравнения соединен с управляющим входом устройства и со вторым входом блока 5 постоянной памяти, второй вход которого связан со вторыми входами памяти 1 и через блок 6 формирования адреса - с адресным входом 7 устройства, подключенным через второй блок 8 формирования адреса - с вторыми входами блока 2 ера-, внеНия, третьи входы которого соединены с выходом регистра 9- Первые и вторые входы одноразрядного блока 10 памяти соединены с соответствующими входами памяти 1, третий элемент И 11 первый вход которого соединен с тактовым входом 12 устройства, первый и второй элементы И 13 и 1f соответстт венно, причем первый вход первого злемента И13 подключен к выходам памяти 1, а выход - к первому входу блока 15 выхода.Первый вход второго э91емента И 1 связан с выходом блока 5, а выход второго элемента И 1 - со вторым входом блока 15. Выход одноразрядного блока памяти 10 соединен с первым входом триггера 16, второй вход которого соединен с выходом элемента 17 задержки, четвертого элемен та И 18. Вход элемента 17, первые входы третьего элемента И 11 и четвертого элемента И 18 связаны с тактовым входом устройства.

Устройство работает следующим обра зом. Ha адресном входе 7 устройства из ЭВМ в блок 6 и блок 8 поступает код адреса, который фиксируется в этих блоках С выхода блока 6 код адреса поступает на входы памяти 1, одноразрядного блока 10 памяти и бло ка 5- С выхода блока 8 старшие разря ды адреса поступают в блок 5 и в бло 2 сравнения, где они сравниваются с кодами, установленными на рег истре 9- При появлении на управляющем входе устройства 4 сигнала опроса блок 5 произведет считывание информации, которая в виде потенциального кода поступает на входы второго элемента И It. Если код, установленный в блоке 8, не совпадает с содержимым из регистра 9 то сигнал, поступающий на вход блока 2 с входа j, не проходит на выход блока 2. Таким образом обращение к памяти 1 и одноразрядному блоку 10 не производится, исходно (нулевое) состояние триггера 16 не меняется. В этом случае тактовый импульс, поступающий по тактовому входу 12 проходит через третий элемент И 17 на опрос второго элемента И 14. Через элемент И 18 тактовый импульс не проходит. В результате этого, информация, -считанная, из блока 5 поступает через элемент И 14 и блок 15 на выход 3 устройства. Если код, установленный в блоке 8 совпадает с содержимым регистра 9 то вместе с опросом блока 5 происходит опрос памяти 1 и одноразрядного блока 10 памяти. Информация, считанная -из памяти 1 поступает на вход эл мента 13 в виде потенциального кода Одноразрядный блок 10 памяти представляет собой одноразрядное запоминающее устройство, где хранится информация, управляющая работой триггера 16. Если по опрошенному здресу на блоке 10 записан О, то триггер 16 не изменяет своего состояния. В этом случае тактовый импульс со входа 12 через элемент И 11 поступает в элемент И 14 и на выходе 3 также появляется информация, считанная из блока 5. Если при опросе второго блока 10 считан сигнал 1, то триггер 16 перейдет в единичное состояние. В результате этого, тактовый импульс со входа 12 через элемент И 18 пе.рейдет в элемент 13 и на выходе 3 через элемент И 13 и блок 15 поступает информация, считанная из памяти 9 6 Спустя некоторое , определяемое ременем прохождения тактового сигнала через элемент задержки 17 триггер 16 устанавливается в исходное состояние. Таким образом, в данном устройг стве с помощью регистра 9 и блока 2 сравнения указываются массивы, в которых производится замещение информации блока 5 информацией, записанной в памяти 1 ,а содержимое блока 1 О указывает по какнм именно адресам будет произведено замещение. Следовательно, в данном устройстве указание информации осуществляется с точностью до одного адреса. Предлагаемое устройство по сравнению с известными повышает эффективность использования запоминающих блоков без разрушения информации, что приводит к сокращению необходимых при отладке объемов памяти данного типа. Кроме того, сокращается суммарное время записи информации в памяти 1, что приводит к повышению производительности и сокращению сроков отладочных работ. формула изобретения Устройство для управления памятью, содержащее блок сравнения, блок постоянной памяти, первый и второй,блоки формирования адреса, регистр и блок вывода, примем выход блока вывода является выходом устройства, адресный вход устройства соединен со входами первого и второго блоков формирования адреса, выход первого блока формирот вания адреса соединен с первыми входами памяти и блока постоянной памяти, управляющий вход устройства соединен со вторым входом блока постоянной памяти и с первым входом блока сравнения, выход которого соединен со вторым входом памяти, выход второго блока формирования адреса соединен с третьим входом блока постоянной памяти и с вторым входом блока сравнения, третий выход которого соединен с выходом регистра, отличающеес я тем, что, с целью повышения точт ности, устройство содержит первый, второй, третий и четвертый элементы И, триггер, одноразрядный блок памяти и элемент задержки, причем выход первого блока формирования адреса и выход блока сравнения соединены соответственно с первым и вторым входами одноразрядного блока памяти, выход

которого соединен с первым входом триггера, выхо памяти соединен с первым входом первого элемента И, выход которого соединен с первым входом блока вывода, второй вход которого соединен с выходом второго элемента И, выход блока постоянной памяти соединен с первым входом второго элемента И, второй вход которого соединен с выходом третьего элемента И, тактовый вход устройства соединен с первыми входами Tpefbero и четвертого элементов И и со входом элемента задержки, еыход которого соединен со вторым

входом триггера, первый и второй выходы которого соединены соответственно со вторыми входами третьего и четвертого элементов И, выход четвертого элемента И соединен со вторым входом первого элемента И,

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 613326, кл, G 06 Р 15/06, 1976.

2.Авторское свидетельство СССР № 29107, кл. Q Об Р П/00, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для откладки программ | 1987 |

|

SU1474656A1 |

| Устройство для управления обращением к памяти при отладке программ | 1981 |

|

SU1001099A1 |

| Устройство для модификации адреса зон памяти при отладке программ | 1983 |

|

SU1161944A1 |

| Устройство для отладки программ | 1983 |

|

SU1104521A1 |

| Устройство для формирования сигналов прерывания при отладке программ | 1986 |

|

SU1348841A1 |

| Устройство для отладки программ | 1985 |

|

SU1251087A1 |

| Устройство для генерирования кодов заданного веса | 1985 |

|

SU1275413A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

| Устройство для микропрограммного управления | 1983 |

|

SU1188742A1 |

| Устройство для формирования сигналов прерывания при отладке программ | 1986 |

|

SU1411755A2 |

Авторы

Даты

1982-07-15—Публикация

1979-02-07—Подача