15

20

, Изобретение относится к цифровой

: вычислительной технике и может быть

I использовано при отладке программ специализированньк цифровых вычисли- тельнык систем (СЦВС).5

Цель изобретения - расширение -функциональных возможностей устройства за счет обеспечения отслеживания

;(запоминания) в соответствующей зоне отладочной памяти информации, поступающей в реальньй абонент в режиме отладки с реальным абонентом,

Кроме этого, информация, фиксируемая параллельно в зоне отладочной памяти в режиме работы с реальным абонентом, может использоваться как диагоностическая информация о теку- щем состоянии абонента в процессе отлад1ш программ СЦВС в реальном масштабе время,

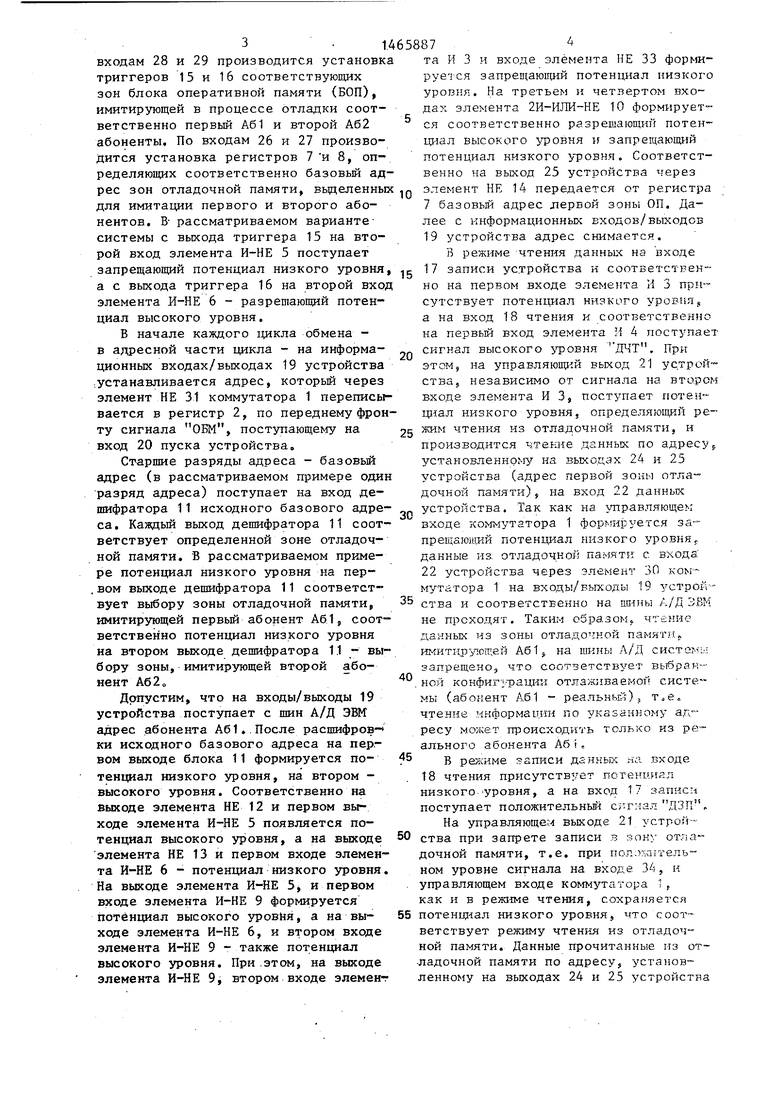

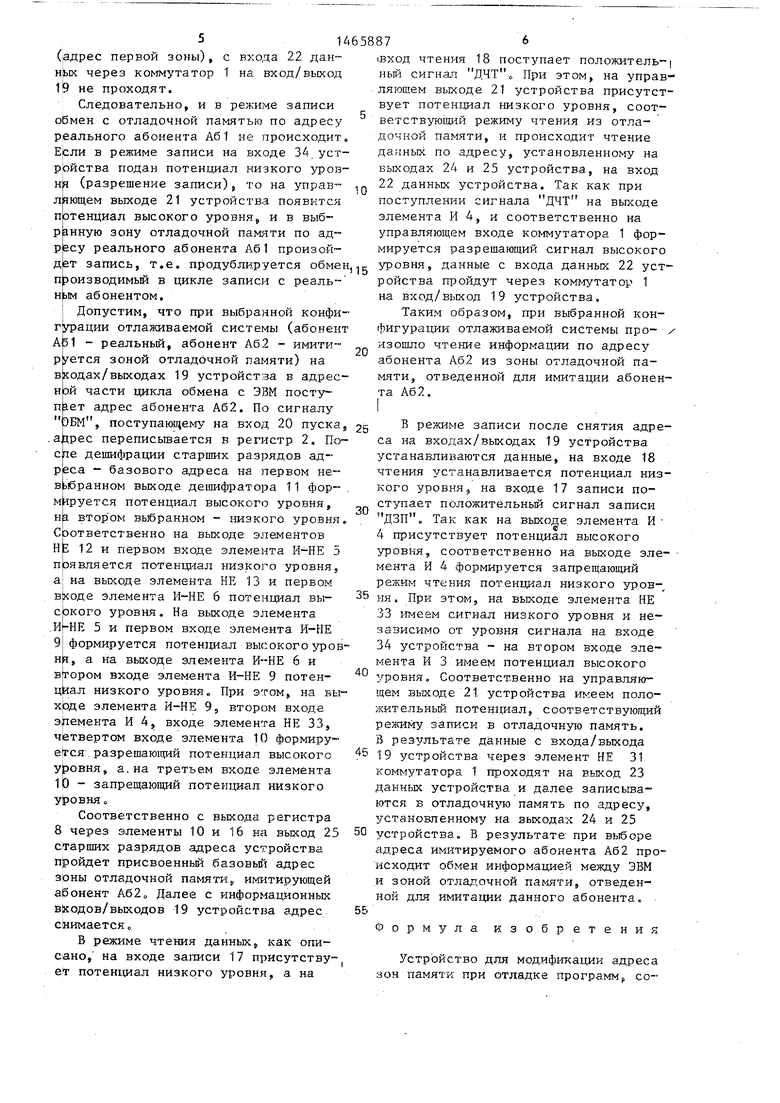

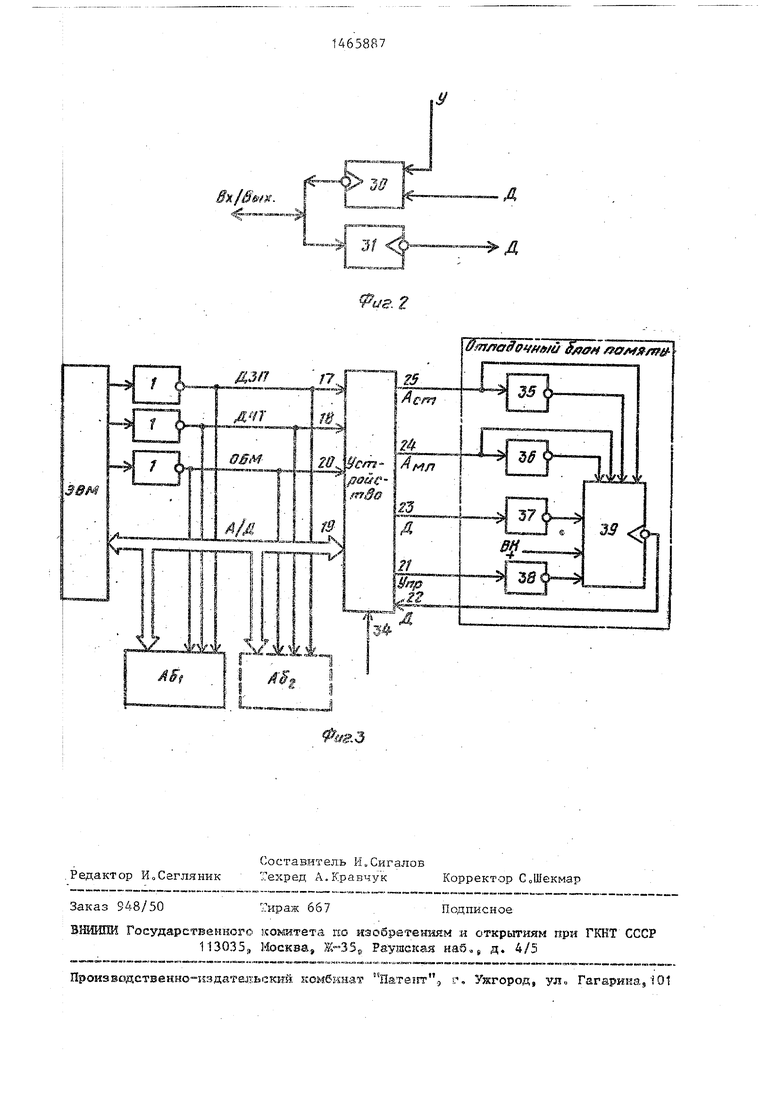

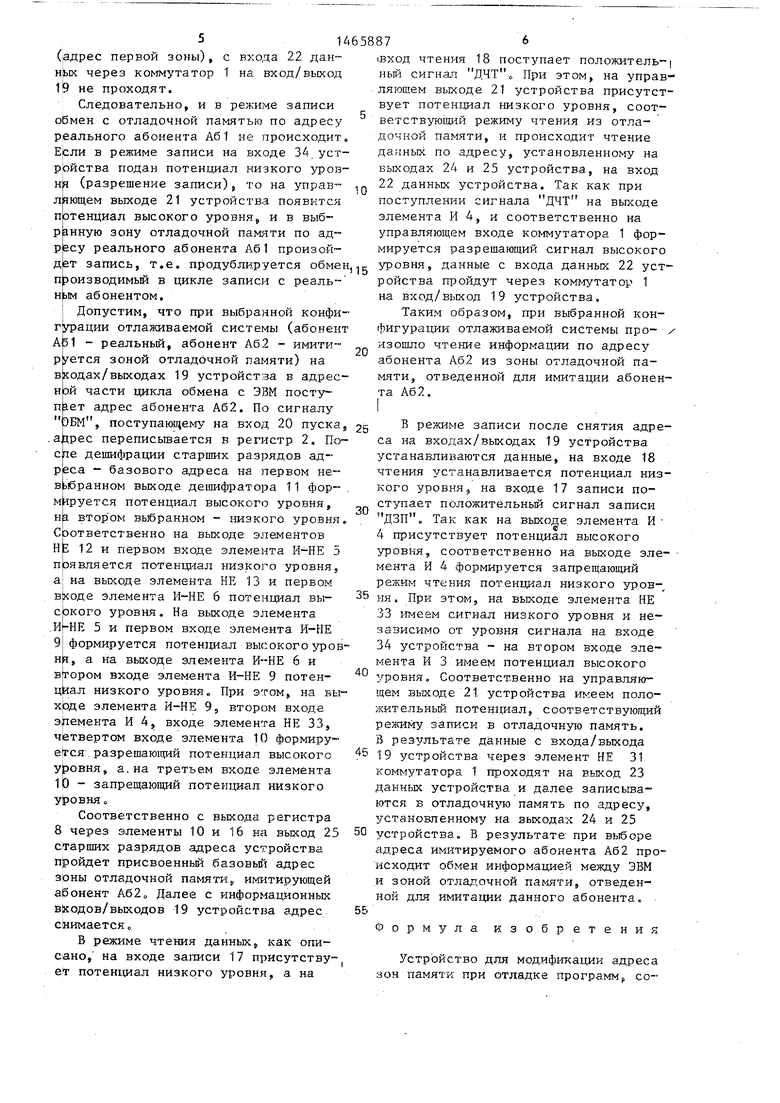

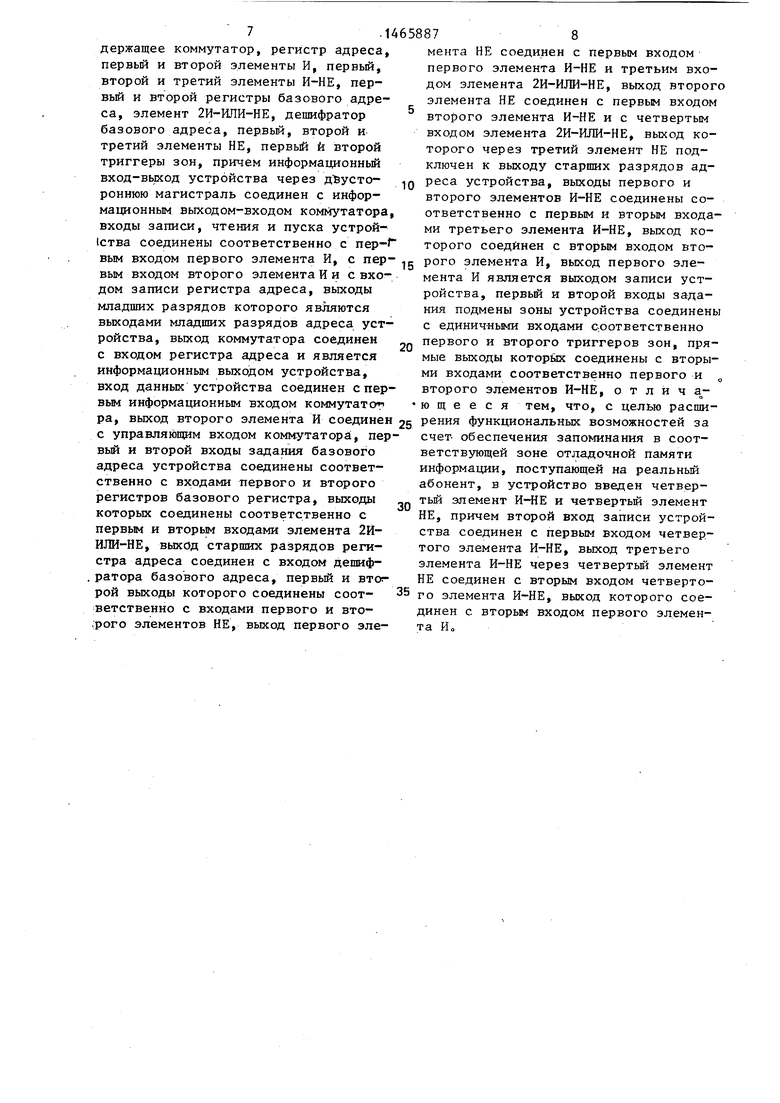

На фиг.1 представлена блок-схема устройства} на фиг.2 - функциональная схема коммутатора} на фиг.З - блок ТотпТ отлаживаемой системы. 35 соединен с управляющим входом отла- I Устройство содержит коммутатор 1, дочной памяти. Вход 22 данных и ин- регистр 2 адреса, первый 3 и второй формационньй выход 23 данньГустрой элем нтГи HF . - -единены соответстве о с элементы И-НЕ, первьй 7 и второй В

регистры базового адреса, третий эле- |мент И-НЕ 9, элемент 2И--ИЛИ-НЕ 10, |дешифратор 11 базового адреса, первый |12, второй 13, третий 14 элементы IHE, первый 15 и второй 16 триггеры |зон вход 17 записи устройства, вход 18 чтения устройства информационные |входы-выходы 19 устройства, вход 20 пускд устройства, выход 21 записи |устройства, вход 22 данных и информа- 1ЦИОННЫЙ выход 23 устройства, выход i24 млад1 1их разрядов адреса устройст- |ва, выход 25 старших разрядов адреса устройства (базовьй адрес), первый :26, второй 27, входы задания базового адреса, первый 28, второй 29 входы зада- а|ния зоны подмены устройства, элемент Й-НЕ 30, элементы НЕ 31, входящие в состав коммутатора (фиг.2), четвертьй элемент И-ИЕ 32, четвертьй элемент НЕ 33, вход 34 записи устройства. Блок

иГ лементГ ч.Зя « - наемой системы отсу;ств;ёт элемент памя- второй абонент А62, т.е. к ЭВМ полти (ЭП) 39, вьшапненный на ШС 185 РУ5. - Управляющий вход ЭП 39 через первьй элемент НЕ 36 соединен с управляю- Ощм входом ОП, вход данных ЭП через

реса ОП соединен с прямым входом старшего разряда адреса и через третий элемент НЕ 35 - с инверсным входом данного разряда ЭП, вход младших разрядов адреса ОП соединен с прямым входом младшего разряда адреса и через четвертьй элемент НЕ 36 с инверс ным входом данного разряда ЭП Вход ВК элемента ЭП подключен к шине потенциала высокого уровня.

Рассмотрим работу устройства на примере отладки СЦВС (фиг.З), содержащей микро-ЭВМ Электроника Б,имеющей интерфейс по ОСТ 11.305-903-80 и, например, два абонента А61 и А62. При этом входы (выходы 19 устройства с:оединены с двунаправленной шиной адреса) данные ЭВМ, вход записи 17, вход 18 чтения и вход 20 пуска соединены соответственно с пинами записи (ДЗП), чтения (ДЧТ) и пуска (ОБМ) через согласующие элементы НЕ. Управляющий выход 21 записи устройства

дом и входом данных отладочной памяти, выход 25 старших разрядов адреса и выход 24 младших разрядов адреса устройства соединены соответственно с адресными входами старших и млад- |ших разрядов блока отладочной памяти. Потентдиал высокого уровня на вы- 5 ходе 21 устройства соответствует режиму записи данных в блок отладочной памяти, потенциал низкого уровня - режиму чтения из блока отладочной памяти.

Вход 34 записи устройства соединен, например, с тумблером на панели управления устройства. Потенциал низкого уровня на входе 34 устройства соответствует разрешению записи в

30

40

45

выбранную зону блока отладочной памяти, а потенциал высокого уровня - зайрету записи в данную зону блока отладочной памяти.

Допустим, что в данной конфигуравторой элемент НЕ 37. - с входом дан- Иых ОП, выход данных ЭП - с выходом данных ОП, вход старшего разряда адключен реальньй абонент А61 и вместо второго абонента А62 подключается зона блока отладочной памяти и опреде- 55 ляемая базовьм адресом, установленным на регистре 8.

В начале работы в зависимости от конфигурации отлаживаемой системы по

5

0

5

5 соединен с управляющим входом отла- дочной памяти. Вход 22 данных и ин- формационньй выход 23 данньГустройреса ОП соединен с прямым входом старшего разряда адреса и через третий элемент НЕ 35 - с инверсным входом данного разряда ЭП, вход младших разрядов адреса ОП соединен с прямым входом младшего разряда адреса и через четвертьй элемент НЕ 36 с инверсным входом данного разряда ЭП Вход ВК элемента ЭП подключен к шине потенциала высокого уровня.

Рассмотрим работу устройства на примере отладки СЦВС (фиг.З), содержащей микро-ЭВМ Электроника Б,имеющей интерфейс по ОСТ 11.305-903-80 и, например, два абонента А61 и А62. При этом входы (выходы 19 устройства с:оединены с двунаправленной шиной адреса) данные ЭВМ, вход записи 17, вход 18 чтения и вход 20 пуска соединены соответственно с пинами записи (ДЗП), чтения (ДЧТ) и пуска (ОБМ) через согласующие элементы НЕ. Управляющий выход 21 записи устройства

- -единены соответстве о с

° « - наемой системы отсу;ств;ёт второй абонент А62, т.е. к ЭВМ полдом и входом данных отладочной памяти, выход 25 старших разрядов адреса и выход 24 младших разрядов адреса устройства соединены соответственно с адресными входами старших и млад- |ших разрядов блока отладочной памяти. Потентдиал высокого уровня на вы- 5 ходе 21 устройства соответствует режиму записи данных в блок отладочной памяти, потенциал низкого уровня - режиму чтения из блока отладочной памяти.

Вход 34 записи устройства соединен, например, с тумблером на панели управления устройства. Потенциал низкого уровня на входе 34 устройства соответствует разрешению записи в

30

0

5

выбранную зону блока отладочной памяти, а потенциал высокого уровня - зайрету записи в данную зону блока отладочной памяти.

Допустим, что в данной конфигура « - наемой системы отсу;ств;ёт второй абонент А62, т.е. к ЭВМ пол-

ключен реальньй абонент А61 и вместо второго абонента А62 подключается зона блока отладочной памяти и опреде- ляемая базовьм адресом, установленным на регистре 8.

В начале работы в зависимости от конфигурации отлаживаемой системы по

3 . 1.465887

входам 28 и 29 производится установка та И 3и входе элемента НЕ 33 форьшруе сязапрещаюищй потенциал низкого уровня

20

30

триггеров 15 и 16 соответствующих зон блока оперативной памяти (БОП), имитирующей в процессе отладки соответственно первый А61 и второй Аб2 абоненты. По входам 26 и 27 производится установка регистров 7 и 8, определяющих соответственно базовьй адрес зон отладочной памяти, вьщеленных Q для имитации первого и второго абонентов, В- рассматриваемом варианте- системы с вькода триггера 15 на второй вход элемента И-НЕ 5 поступает запрещающий потенциал низкого уровня, g а с выхода триггера 16 на второй вход элемента И-НЕ 6 - разрешающий потенциал высокого уровня.

В начале каждого 11;икла обмена - в адресной части цикла - на информационных входах/выходах 19 устройства .устанавливается адрес, которьй через элемент НЕ 31 коммутатора 1 переписывается в регистр 2, по переднему фронту сигнала ОБМ, поступающему на вход 20 пуска устройства,

Старщие разряды адреса - базовьй адрес (в рассматриваемом примере один разряд адреса) поступает на вход дешифратора 11 исходного базового адреса. Кавдый выход дешифратора 11 соответствует определенной зоне отладочной памяти. В рассматриваемом примере потенциал низкого уровня на пер- ,вон выходе дещифратора 11 соответствует выбору зоны отладочной памяти, имитирующей первьй абонент А61, соответственно потенциал низкого уровня на втором выходе дещифратора 11 - выбору зоны, имитирующей второй абонент Аб 2 о

Допустим, что на входы/выходы 19 устройства поступает с щин А/Д ЭШ адрес абонента А61.. После расщифрозв- ки исходного базового адреса на первом выходе блока 11 формируется потенциал низкого уровня, на втором - высокого уровня. Соответственно на выходе элемента НЕ 12 и первом выходе элемента И-НЕ 5 появляется потенциал высокого уровня, а на выходе элемента НЕ 13 и первом входе элемента И-НЕ 6 - потенциал низкого уровня. На выходе элемента И-НЕ 5j и первом входе элемента И-НЕ 9 формируется потенциал высокого уровйя, а на выходе элемента И-НЕ 6, и втором входе элемента И-НЕ 9 - также потенциал высокого уровня. При .этом, на выходе элемента И-НЕ 9, втором входе элементНа третьем и четвертом входах элемента 2И-ИЛИ-НЕ 10 формируется соответственно разреша ощий потенциал высокого уровня и запрещающий потенциал низкого уровн.ч. Соответственно на выход 25 устройства через элемент НЕ 14 передается от регистра 7 базовьй адрес лервой зоны ОП. Далее с информационных входов/выходов 19 устройства адрес снимается.

В режиме чтения .данных на входе

17записи ус.тройства и соотБетст)зен- но на первом входе элемента И 3 присутствует потен1щал низкого ypoBisn.,

а на вход 18 чтения и соответственно на первьй вход элемента li 4 поступает сигнал высокого фовня ДЧТ. При этом, на управляющ1-1й вькод 21 ус.тройства, независимо от сигнала на вто.ром входе элемента И 3, поступает потен- низкого уровня, определяющий ре

рп жим чтения из отладочной памяти, и производится чтение данных по адресу установленном - на выходах 24 и 25 устройства (адрес первой зоны отладочной памяти)5 на вход 22 данных устройства. Так как на. управляющем входе коммутатора 1 форГ .гируется запрещающий потенциал низкого уровня,, данные из. отладочной памяти с входа 22 устройства через 30 коммутатора 1 на входы/выходы 19 устрой-- ства и соответственно на ашны А/Д ЗВМ не проходят. Таким образом, чтение данных из зоны отладочной памяти,, имитир огг,ей Аб на шкны Л/Д системы запрещено, что соотзетствует выбрак. ной конфиг-урации отлаживаемой системы (абонент А61 - реальньй). т.е., чтение информации по указанному ад-- ресу может происходить только из реального абонента Аб «

В режиме записи данных на .входе

18чтения присутствует потенциал низкого УРОВНЯ, а на вход 17 записи поступает положительный сигнал ДЗП Ч

На управляюще;- вькоде 21 устройства при запрете записи .в зону отладочной памяти, т.е. при п о. тельном уровне сигнала на входе 34, н . управляющем входе коммутатора t

как и в режиме чтения, сохраняется 55 потенциал низкого уровня, что соответствует режиму чтения из отладочной памяти. Данные прочитанные из отладочной памяти по адресу, установленному на выходах 24 и 25 устройства

35

45

50

руе сязапрещаюищй потенциал низкого уровня

20

30

Q g

На третьем и четвертом входах элемента 2И-ИЛИ-НЕ 10 формируется соответственно разреша ощий потенциал высокого уровня и запрещающий потенциал низкого уровн.ч. Соответственно на выход 25 устройства через элемент НЕ 14 передается от регистра 7 базовьй адрес лервой зоны ОП. Далее с информационных входов/выходов 19 устройства адрес снимается.

В режиме чтения .данных на входе

17записи ус.тройства и соотБетст)зен- но на первом входе элемента И 3 присутствует потен1щал низкого ypoBisn.,

а на вход 18 чтения и соответственно на первьй вход элемента li 4 поступает сигнал высокого фовня ДЧТ. При этом, на управляющ1-1й вькод 21 ус.тройства, независимо от сигнала на вто.ром входе элемента И 3, поступает потен- низкого уровня, определяющий ре

рп жим чтения из отладочной памяти, и производится чтение данных по адресу установленном - на выходах 24 и 25 устройства (адрес первой зоны отладочной памяти)5 на вход 22 данных устройства. Так как на. управляющем входе коммутатора 1 форГ .гируется запрещающий потенциал низкого уровня,, данные из. отладочной памяти с входа 22 устройства через 30 коммутатора 1 на входы/выходы 19 устрой-- ства и соответственно на ашны А/Д ЗВМ не проходят. Таким образом, чтение данных из зоны отладочной памяти,, имитир огг,ей Аб на шкны Л/Д системы запрещено, что соотзетствует выбрак. ной конфиг-урации отлаживаемой системы (абонент А61 - реальньй). т.е., чтение информации по указанному ад-- ресу может происходить только из реального абонента Аб «

В режиме записи данных на .входе

18чтения присутствует потенциал низкого УРОВНЯ, а на вход 17 записи поступает положительный сигнал ДЗП Ч

На управляюще;- вькоде 21 устройства при запрете записи .в зону отладочной памяти, т.е. при п о. тельном уровне сигнала на входе 34, н . управляющем входе коммутатора t

как и в режиме чтения, сохраняется 5 потенциал низкого уровня, что соответствует режиму чтения из отладочной памяти. Данные прочитанные из отладочной памяти по адресу, установленному на выходах 24 и 25 устройства

35

5

0

(|адрес первой зоны), с входа 22 дан- через коммутатор 1 на вход/выход 19 не проходят.

Следовательно, и в режиме записи обмен с отладочной памятью по адресу реального абонента Аб1 не происходит, в режиме записи на входе 34.уст- р йства подан потенциал низкого уров- н (разрешение записи), то на управляющем выходе 21 устройства появится потенциал высокого уровня и в выбранную зону отладочной памяти по ад- рвсу реального абонента А61 произойдет запись

10

20

производимый в цикле записи с реальным абонентом.

I Допустим, что при выбранной конфи- гКфации отлаживаемой системы (абонент А31 - реальньй, абонент Аб2 - имити- р/ется зоной отладочной памяти) на вкодах/выходах 19 устройства в адресной части цикла обмена с ЭВМ поступает адрес абонента А62. По сигналу ОБМ, поступающему на вход 20 пуска, 25

.адрес переписьтается в регистр 2. U(.y сле дешифрации старших разрядов адреса - базового адреса на первом не-- вьйранном выходе дешифратора 11 формируется потенциал высокого уровня, на втор ом выбранном - низкого уровня. Соответственно на выходе элементов НЕ 12 и первом входе элемента И-НЕ 5 появляется потенциал низкого уровняj а| на выходе элемента НЕ 13 и первом в|ходе элемента И-НЕ 6 потенциал вы- сЬкого уровня. На выходе элемента

.И|-НЕ 5 и первом входе элемента И-НЕ 9| формируется потенциал высокого уров- н|н, а на выходе элемента И--НЕ 6 и в|гором входе элемента И-НЕ 9 потен- низкого уровня. При этом на вы1ВХОД чтения 18 поступает положите ньй сигнал При этом, на уп ляющем выходе 21 устройства прису вует потенциал шзкого уровня, со ветствующий режиму чтения из отла дочной памяти, и происходит чтени данных по адресу, установленному выходах 24 и 25 устройства, на вх 22 данных устройства. Так как при поступлении сигнала ДЧТ на вько элемента И 4, и соответственно на управляющем входе коммутатора 1 ф мируется разрешающий сигнал высок

, т.е. продублируется обмен, g -уровня, данные с входа данных 22

30

роиства щэоидут через коммутатор на вход/выход 19 устройства.

Таким образом, при выбранной к Фигурации отлаживаемой системы пр изошло чтение информации по адрес абонента Аб2 из зоны отладочной п мяти, отведенной для имитации або та А62.

В режиме записи после снятия а са на входах/выходах 19 устройств устанавливаются данные, на входе чтения устанавливается потенциал кого уровня, на входе 17 записи п ступает положительньй сигнал запи ДЗП. Так как на выходе, элемента 4 присутствует потенциал высокого уровня, соответственно на выходе мента И 4 формщ)уется запрещающий режим чтения потенциал низкого ур 35 ыя. При этом, на выходе элемента

33имеем сигнал низкого уровня и зависимо от уровня сигнала на вхо

34устройства - на втором входе э мента И 3 имеем потенциал высоког уровня. Соответственно на управля щем выходе 21. устройства имеем по жительный потенциал, соответствую режиму записи в отладочную память

хрде элемента И-НЕ 9, втором входе э|аемента И 4, входе элемента НЕ 33, четвертом входе элемента 10 формиру™ е1гся-. разрешающий потенциал высокого уровня, а.на третьем входе элемента 10 - запрещающий потенциал низкого уровня

Соответственно с выхода регистра 8 через элементы 10 и 16 на выход 25 старших разрядов адреса устройства пройдет присвоенньй базовьй адрес зоны отладочной памяти,, имитирующей абонент А62. Далее с информационных в)кодов/выходов 19 устройства адрес сиимаетсяс

В режиме чтения данных,, как описано, на входе записи 17 присутствует потенциал низкого уровня, а на

1ВХОД чтения 18 поступает положитель-| ньй сигнал При этом, на управляющем выходе 21 устройства присутствует потенциал шзкого уровня, соответствующий режиму чтения из отладочной памяти, и происходит чтение данных по адресу, установленному на выходах 24 и 25 устройства, на вход 22 данных устройства. Так как при поступлении сигнала ДЧТ на вькоде элемента И 4, и соответственно на управляющем входе коммутатора 1 формируется разрешающий сигнал высокого

уст- 1

-уровня, данные с входа данных 22

роиства щэоидут через коммутатор на вход/выход 19 устройства.

Таким образом, при выбранной кон- Фигурации отлаживаемой системы про- / изошло чтение информации по адресу абонента Аб2 из зоны отладочной памяти, отведенной для имитации абонента А62.

5

0

0

Б

В режиме записи после снятия адреса на входах/выходах 19 устройства устанавливаются данные, на входе 18 чтения устанавливается потенциал низкого уровня, на входе 17 записи поступает положительньй сигнал записи ДЗП. Так как на выходе, элемента И 4 присутствует потенциал высокого уровня, соответственно на выходе элемента И 4 формщ)уется запрещающий режим чтения потенциал низкого уров-, 5 ыя. При этом, на выходе элемента НЕ

33имеем сигнал низкого уровня и независимо от уровня сигнала на входе

34устройства - на втором входе элемента И 3 имеем потенциал высокого уровня. Соответственно на управляющем выходе 21. устройства имеем положительный потенциал, соответствующий режиму записи в отладочную память.

В результате данные с входа/выхода 5 19 устройства через элемент НЕ 31 коммутатора 1 проходят на выход 23 данных устройства и далее записываются в отладочную память по адресу, установленному на выходах 24 и 25 устройства. В результате- при выборе адреса имитируемого абонента Аб2 происходит обмен информацией между ЭВМ зоной oтлa ;oчнoй памяти, отведени

ной для имитации данного абонента.

Формула изобретения

Устройство для модифшсации адреса зон памяти при отладке программ со10

держащее коммутатор, регистр адреса, первый и второй элементы И, первый, второй и третий элементы И-НЕ, пер- вьй и второй регистры базового адреса, элемент 2Й-ИЛИ-НЕ, дешифратор базового адреса, пер.вьй, второй и третий элементы НЕ, первьй и второй триггеры зон, причем информационный вход-вькод устройства через двустороннюю магистраль соединен с информационным выходом-входом KOMisiyTaTOpa, входы записи, чтения и пуска устрой- 1ства соединены соответственно с nep-f вым входом первого элемента И, с пер- - вым входом второго элемента И и с вхо- дом записи регистра адреса, выходы младших разрядов которого являются выходами младших разрядов адреса устройства, выход коммутатора соединен с входом регистра адреса и является информационным выходом устройства, вход данных устройства соединен с первым информационным входом коммутатог ра, выход второго элемента И соединен JK с управляющим входом коммутатора, первьй и второй входы задания базового адреса устройства соединены соответственно с входами первого и второго регистров базового регистра, выходы которых соединены соответственно с первьм и вторьм входами элемента 2Й- ИЛИ-НЕ, выход старших разрядов регистра адреса соединен с входом дешиф- ратора базового адреса, первьй и вто:- рой выходы которого соединены соответственно с входами первого и вто- рого элементов НЕ, выход первого эле35

20

30

10

- JK мента НЕ соединен с первым входом первого элемента И-НЕ и третьим входом элемента 2И-ИЛИ-НЕ, выход второго элемента НЕ соединен с первым входом второго элемента И-НЕ и с четвертым входом элемента 2И-ИЛИ-НЕ, выход которого через третий элемент НЕ подключен к выходу старших разрядов адреса устройства, выходы первого и второго элементов И-НЕ соединены соответственно с первым и вторым входами третьего элемента И-НЕ, выход которого соединен с вторым входом второго элемента И, выход первого элемента И является выходом записи устройства, первьй и второй входы задания подмены зоны устройства соединены с единичньми входами с-оответственно первого и второго триггеров зон, прямые выходы которьк соединены с вторыми входами соответственно первого и второго элементов И-НЕ, о т л и ч ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет- обеспечения запоминания в соответствующей зоне отладочной памяти информации, поступающей на реальньй абонент, в устройство введен четвер- тьй элемент И-НЕ и четвертьй элемент НЕ, причем второй вход записи устройства соединен с первым входом четвертого элемента И-НЕ, выход третьего элемента И-НЕ через четвертьй элемент НЕ соединен с вторым входом четверто- 5 го элемента И-НЕ, выход которого соединен с вторым входом первого элемента И

20

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для модификации адреса зон памяти при отладке программ | 1985 |

|

SU1282140A1 |

| Устройство для отладки программ | 1989 |

|

SU1674135A1 |

| Устройство для модификации адреса зон памяти при отладке программ | 1983 |

|

SU1161944A1 |

| Устройство для отладки программ | 1988 |

|

SU1608673A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для отладки программ | 1982 |

|

SU1100627A1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Устройство для отладки программ | 1984 |

|

SU1238086A1 |

| Устройство для отладки программ | 1987 |

|

SU1425687A1 |

Изобретение относится к области цифровой вь числительной техники и может быть использовано при отладке программ специализированных вычислительных систем. Целью изобретения ЯВ ляется расширение функциональных воз можностёй за счет обеспечения фикси/7 f. рования в соответствующей зоне отладочной памяти информации, поступающей в реальньй абонент в режиме обмена, что позволяет постоянно иметь диагностическую информацию о текущем состоянии объекта. С этой целью, кроме коммутатора 1, регистра адреса 2, первого 3, второго 4 элементов И, первого 5, второго 6 и третьего 9 элементов И-НЕ, первого 7 и второго 8 регистров присвоенного базового адреса, элемента 2И-ШШ-НЕ 10, дешифратора 11 исходного базового адреса, первого 12, второго 13 и третьего 14 элементов НЕ, первого 15 и второго 16 триггеров зон устройство содер- Q жит четвертьй элемент НЕ 33 и четвер- тьй элемент И-НЕ 32 с соответствующими связями 3 ил. Q1 О) и Фуе.

.Редактор ИоСегляник

Составитель И.Сигалов

Техред А.Кравчук Корректор С„Шекмар

Заказ 948/50

Тираж 667

ВНШШИ Государственного :сомитета ко иэобрететмм и открытиям при ГКНТ СССР 113035,, Москва, Ж.-35 Раушскал наб д. 4/5

Производственно-издательский комбинат Пателгг, г, Ужгород, ул, Гагарика Ю

Подписное

| Устройство для модификации адреса зон памяти при отладке программ | 1983 |

|

SU1161944A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для модификации адреса зон памяти при отладке программ | 1985 |

|

SU1282140A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-03-15—Публикация

1987-03-09—Подача