(54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1580442A1 |

| Устройство для отображения информации | 1987 |

|

SU1474634A1 |

| Оперативное запоминающее устройство | 1982 |

|

SU1088066A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Устройство для управления полупровод-НиКОВыМ НАКОпиТЕлЕМ | 1979 |

|

SU842811A1 |

| Динамическое оперативное запоминающее устройство | 1981 |

|

SU1003142A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1986 |

|

SU1327174A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

t

Изобретение относится к запоминающим устройствам.

Известно оперативное запоминаёощее устройство, содержавдее накопители, построенгале на базе больших интегральных схем с структурой металл-окисел-полупроводник (БИС МОП) динамического типа, кото1«е в процессе работы требуют регенерации содержимого накопителя оперативного запоминаклцего устройства ij .

Недостаток этого устройства - выполнение фиктивных циклов считывания для регенерации содержимого накопителя, что снижает быстродействие устрой ства.

Наиболее близким техническим рвением к предлагаемому изобретению является устройство, содержащее накопи ель, приемный регистр адреса, формирователь команды обращения, мультиплексор адреса, таймер регенерации, триггер регенерации/ схему ИЛИ, схему И, счетчик адреса регенерации ЗД

Адресные шины устройства подключены к входс1м приемного регистра адреса с выхода которого адреса столбцов (М шин) подключены к адресным входам накопителя,а адреса строк (Мшин) подкяючены к одному из входов мультиплек

сора адреса, ко второму входу которого подключены входы N-разрядного счетчика адреса регенергщии. Выходы мультиплексора подключены к остальным адресным входам накопителя. TediMep регенерации подключен к установочному входу триггера регенерации, вход Сброс которого подключен к выходу N+1 счетчика адреса. Выход триггера регенерации подключен к входу схемд И, входу Сброс счетчика и к управляющему входу мультиплексора адреса. Вход схемы ИЛИ подключен к управляющей шине оперативного запоминающего устройства, а выход ее через формирователь команды обращения - к управляющему входу накопителя. Второй вход схемл И подключен к тактовой шине устройства, а выход ее - к суммирующему входу счетчика адреса регенерации.

Однако в известном устройстве необходимо блокировать прием обращений к оперативному запоминающему устройству на время регенергщии, что снижает быстродействие устройства.

Цель изобретения - повыление быстродействия устройства.

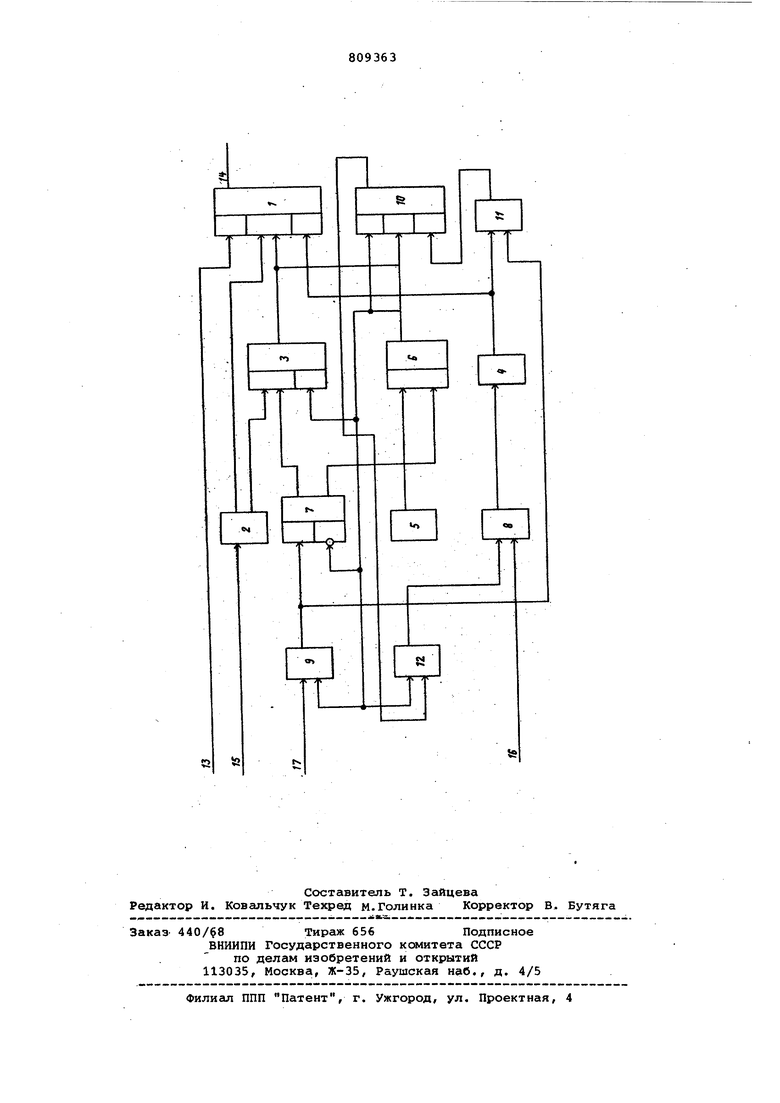

Поставленная цель достигается тем, что в оперативное запоминающее устройство, содержащее регистр гщреса, мультиплексор адреса, формирователь сигналов обращения, генератор сигналов регистрации, триггер, счетчик, первый элемент ИЛИ, первый элемент И и первый накопитель, первый вход и выход которого соединены соответственней с информационным входом и выходом устройства, второй вход - с первым выходом регистра адреса, вход которого , подключен .к адресной шине устройства, а второй выход - к первому входу МУЛЬ типлексора адреса, второй вход которо го соединен с выходом младших разрядов счетчика, а выход. - с адресным входом первого накопителя, управляющий вход которого подключен к выходу формирователя сигналов обращения, вход которого соединен с выходом первого элемента ИЛИ, один из входов которого подключен к управляющей шине устройства, первый и второй входы первого элемента И соединены соответственно с шиной тактовых сигналов и с установочным входом счетчика, управ ляющим входом мультиплексора адреса и выходом триггера, установочный вход которого подключен к выходу генератора сигналов регенерации, а другой вход - к выходу старших разрядов счет чика, счетный вход которого соединен с выходом первого элемента И, введены вторые накопитель, элемент ИЛИ и элемент И, выход которого соединен с другим входом первого .элемента ИЛИ, один из входов - со вторым входом первого элемента И, а другой вход с выходом второго накопителя, адресный и информационный входы которого подключены соответственно к адресному входу первого накопителя и к выходу триггера, вход Запись - к выходу второго элемента ИЛИ, первый вход которого соединен с выходом первого эле мента И, а второй вход - к выходу фор мирователя сигналов обращения. На чертеже изображена принципиальная схема предлагаемого устройства. Устройство содержит первый накопитель 1, регистр 2 адреса, мультиплексор 3 адреса, форг/шрователь 4 сигналов обращения, генератор 5 сигналов регенерации, триггер 6, счетчик 7, первый элемент ИЛИ 8, первый элемент И 9, -вторые накопитель 10, элемент ИЛИ 11 jfi элемент И 12, информационный вход 13, выход 14, адресную 15 и упра1 ляющую 16 шины, шину 17 тактовых; сигналов. Первый вход и выход первог накопителя 1 соединены соответственно с информационнЕлм входом 13 и выходом 14 устройства, второй вход - с первым выходом регистра 2 адреса, вход которого подключен к адресной шине 15 устройства. Второй выход регистра 2 адреса подключен к первому входу мультиплексора 3 адреса, второ вход которого соединен с выходом младших разрядов счетчика 7, а выход - с адресным входом первого нако пителя 1. Управляющий вход первого накопителя 1 подключен к выходу формирователя 4 сигналов обращения, вход которого соединен с выходом первого элемента ИЛИ 8, один из входов которого подключен к управляющей шине 16 устройства. Первый и второй входы первого элемента И 9 соединены соответственно с шиной 17 тактовых сигналов и с установочным входом счетчика 7, управляющим входом мультиплексора 3 адреса и :выходом триггера 6, установочный вход которого подключен к выходу генератора 5 сигналов регенерации, а другой вход - к выходу старших разрядов счетчика 7. Счетный вход счетчика 7 соединен с выходом первого элемента И 9. Выход второго элемента И 12 соединен с другим входом первого элемента ИЛИ 8, один из входов со вторым входом первого элемента И 9, а другой вход - с выходом второго накопителя 10. Адресный и информационный входы . второго накопителя 10 подключены соответственно к адресному входу первого накопителя 1 и к выходу триггера 6 , а вход Запись - к выходу второго элемента ИЛИ 11. Первый вход второго элемента ИЛИ 11 соединен с выходом первого элемента И 9, а второй вход - с выходом формирователя 4 сигналов обращения. В описываемом варианте устройства первый накопитель выполнен на интегральных схемах ИС МОП, а второй накопитель 10 и другие элементы устройства выпйлнешл на интегральных схемах, с транзисторно-транзисторной логикой. Устройство работает следующим образом. В период между двумя циклами регенерации (рабочий цикл) триггер 6 находится .в состоянии О, при этом мультиплексор 3 адреса подключен к регистру 2 адреса,.счетчик 7, предназначенный для счета адресов регенерации, сброшен, элемент И 9 закрыт, на информационном входе второго накопителя 10 . установлена 1. Устройство воспринимает команды обргицения к нему от внааней системы и обеспечивает оперативный обмен информации. Рассмотрим одно из обращений к оперативному запоминатацему устройству (для определенности - считывание). Система выдает на информационный вход 13 устройства адрес ячейки, из которой должна быть считана информа- . ция и управляющий сигнал, поступающий через первый элемент ИЛИ 8 на вход формирователя 4 сигналов обращения, с выхода которого команда обращения поступает на управляющий вход первого накопителя 1 и одновременно через второй элемент ИЛИ 11 поступает на вход Запись второго накопителя 10. Поскольку на адресных входах второго накопителя 10 установлен адрес Ар, соответ ствующий номеру строки АХ первого накопителя 1, а на информационном вх .да - нуль, то в указанную ячейку вто рого накопителя 10 будет записан нул Следовательно, при любом обращении к устройству во второй накопитель 10 записывается нуль по адресу, соответ ртвующему номеру строки первого нако пителя 1. Одновременно выполняется регенерация всех ячеек этой строки.При срабаты; Ьании генератора 5 сигналов регенерации триггер б устанавливается в 1 и начинается цикл регенерации. Уровень 1 с выхода триггера б открывает эл менты. И 9, И 12, снимает сброс со счетчика 7 и поступает на информационный вход второго накопителя 10. В начале цикла регенерации содержимое счетчика 7 . Если по адресу во второй накопитель 10 записан О (это означает, что в предыдущем рабочем цикле было обращение в строку АХ первого накопителя 1) . Элемент И 12 остается закрытым, то регенерирующее обргицение к первому накопителю 1 не выполняется. . Тактовый импульс через открытый первый элемент И 9 прибавит 1 к содержимому счетчика запишет 1 в ячейку с адресом второго накопителя 10. Так будет до тех пор, пока в ячейке с адресом не окажется записанной 1. Это означает, что в соответствующую строку с адресом первого накопителя 1 не было обращения врабочем цикле и ее необходимо регенерировать. Второй элемент И 12 будет открыт, через первый элемент ИЛИ 8 будет запущен формирователь 4 сигналов обращения и осущесо влен цикл обращения к первому накопителю 1 для регенерации содержимого строки с адресом Таким образом, регенерироваться будут строки первого накопителя 1, в котором в данном периоде регенерации не было обраицений, а к концу цикла регенерации по всем адресам второго накопителя 10 будут записаны 1 Таким образом, в предлагаемом устройстве существенно сокращено время выполнения цикла регенерации, что повышает быстродействие устройства. Формула изобретения Оперативное запоминающее устройство, содержащее регистр адреса, мультиплексор адреса, формирователь сигналов обращения, генератор сигналов регенерации, триггер, счетчик, первый элемент ИЛИ, первый элемент И и первый накопитель, первый вход и выход которого соединены соответственно с информационным входом и выходом устройства, второй вход - с первым выходом регистра адреса, вход которого подключен к адресной шине устройства, а второй выход - к первому входу мультиплексора адреса, второй вход которого соединен с выходом младших разрядов счетчика, а выход с адресным входом первого накопителя, управляющий вход которого подключен к выходу формирователя сигналов обращения, вход которого соединен с выходом первого элемента ИЛИ, один из входов которого подключен к управляющей шине устройства, первый и второй входы первого элемента И соединены соответственно с шиной тактовых сигналов и с установочным входом счетчика, управляющим входом мультиплексора адреса и выходом триггера, установочный вход которого подключен к выходу генератора сигналов регенерации, а другой вход - к выходу старших разрядов счетчика, счетный вход которого соединен с выходом первого элемента И, отличающееся тем, что, с целью повышения быстродейг ствйя устройства,оно содержит накопитель,элемент ИЛИ и элемент И, выход которого соединен с другим входом первого элемента ИЛИ, один из входов - со вторым входом первого элемента И, а другой вход - с выходом второго накопителя, адресный и информационный входы которого подключены соответственно к адресному входу первого накопителя- и к выходу триггера, а вход Запись - к выходу второго элемента ИЛИ, первый вход которого соединен с выходом первого элемента И, а второй вход - с выходом формирователя сигналов обращения. Источники информации, принятые во внимание при экспертизе 1.Особенности проектирования систем с динамическими ЗУ. - Электроника, 1973, 3, с. 43-50. 2.Model 26tOA JnteFactfve Display Terminal, Servlse manual, HewlettPackard, 1975, p. 2-15, 2-7, 2-9 (прототип).

Авторы

Даты

1981-02-28—Публикация

1979-05-10—Подача