га, преобразователь параллельного кода в последовательный, четвертый элемент ИЛИ и буферный регистр, входы которого соединены с входами блока управления настройкой, первый выход - с первыми входами пятого элемента ИЛИ и преобразователя параллельного кода в последовательный,

второй выход через последовательно соединенные пятый элемент ИЛИ, преобразователь параллельного кода, в последовательный, регистр сдвига с выходом кольцевого регистра сдвига , выходы которого соединены с выходами блока управления настройкой . ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Квадратор | 1986 |

|

SU1325469A1 |

| Устройство для решения нелинейных краевых задач | 1987 |

|

SU1683028A1 |

| Устройство для формирования адресов табличных функций | 1980 |

|

SU932496A1 |

| Устройство для вычисления стандартных функций | 1980 |

|

SU942032A1 |

| Устройство для преобразованиядВОичНОгО КОдА B избыТОчНыйциКличЕСКий КОд | 1978 |

|

SU798797A1 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления функций в модулярной системе счисления | 1985 |

|

SU1322268A1 |

| Гибридный функциональный преобразователь | 1982 |

|

SU1582190A1 |

| Управляемый генератор случайных чисел | 1981 |

|

SU960812A1 |

1. МНОГОКАСКАдаОЕ РЕЗЕРВИРО. ВАНН(Ж УСТР(, содержащее в каждом i-M каскаде (, ... К) i ре- зервируемых и (N-t) контрольных блоков (N con8t), первую группу из первого и второго элементов И и первого элемента ИШ и блок сравнения, пртой выход которого подключен к первому входу первого элемента И первой rpynnbi данного каскада, инверсный выход - к первому входу второго элемента И первой группы данного каскада, первые входы - к выходам контрольных блоков данного каскада, а вгорие входы - к входам контрольных блоков данного каскада и к шине контрольной {шформации, о т л и ч а ющ е е с я тем, чтл, с целью повьшения надежности и контроля пригодности устройства, оно содержит блок управления настройкой, блок регист- . ров, .селектор мин 4ального кода, блоки деления, третьи элементы И, второй и третий элементы ИЛИ и в каждом i-M каскаде

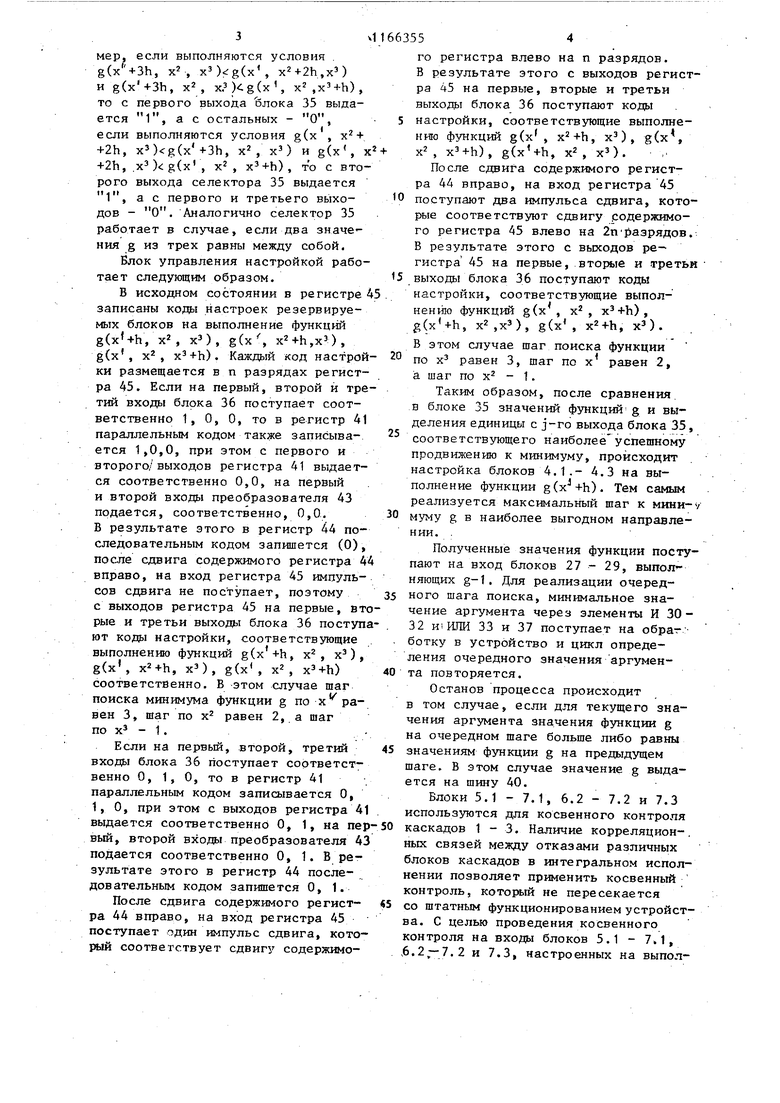

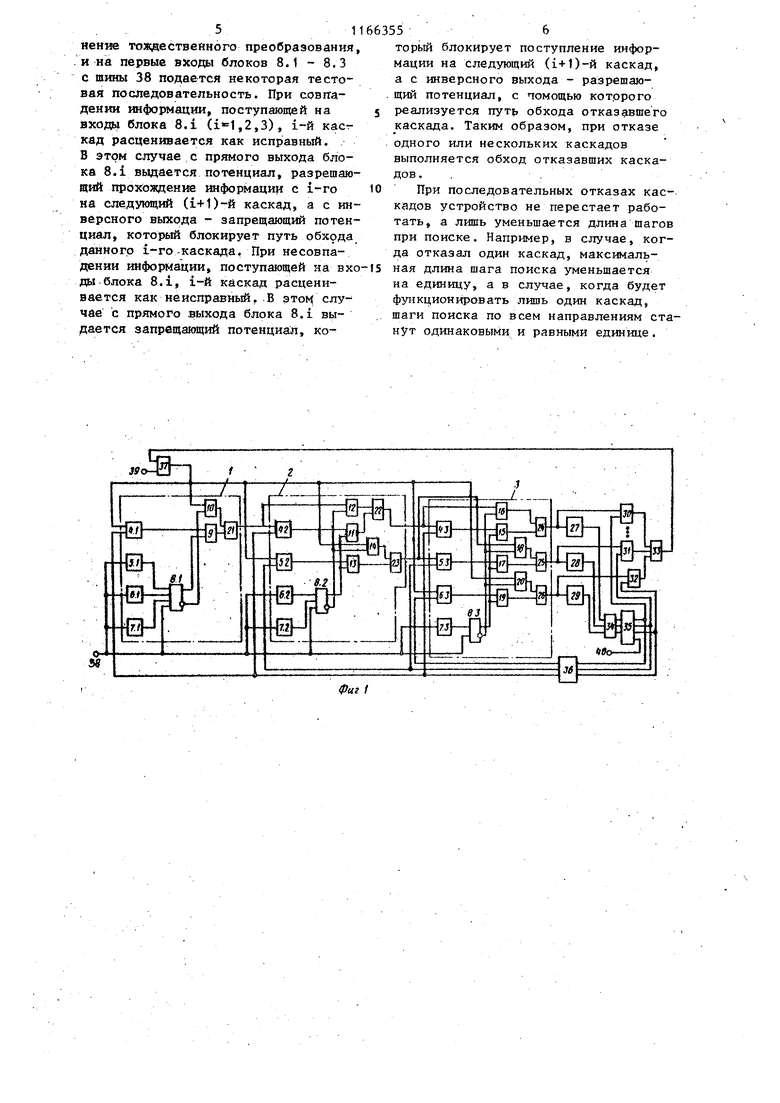

Изобретение относится к вычислительной технике и дискретной автома тике и может быть использовано при построении цифровой аппаратуры повы шенной надежности. Цель изобретения - повьппение надежности и контролепригодности устройства. На фиг. 1 приведена блок-схема .многокаскадного резервированного ус ройства; на фиг. 2 - схема блока управления настройкой. Многокаскадное резервированное устройство содерясит каскады 1-3, первые резервируемые блоки 4.1 - 4. соответственно каскадов 1-3, контрольки блок 5.1 каскада 1, вторые резервируемые блоки 5.2 и 5.3 соответственно каскадов 2 и 3, конт рольные блоки 6.1 и 6.2 каскадов 1 и 2, третий резервируемый блок 6.3 каскада 3, контрольные блоки 7,1 7,3 каскадов 1 - 3, блоки 8.1 - 8.3 сравнения, первый 9 и второй 10 элементы И первой группы каскада 1, первый 11 и второй 12 элементы И пё вой группы каскада 2, первый 13 и второй 14 элементы И второй группы каскада 2, первый 15 и второй 16 элементы К первой группы каскада 3, первый 17 и второй 18 элементы И второй группы каскада 3, пер-г вый 19 и второй 20 элементы И треть ей группы каскада 3, первые элементы ИЛИ 21 и 22 первых групп соответ ственно каскадов 1 и 2 первьй элемент ИЛИ 23 второй группы каскада 2 первые элементы КПК 24 - 26 первой, второй и третьей групп соответствен но, каскада 3, блЬки 27 - 29 деления третьи э.дементы И 30 - 32, второй элемент ИЛИ 33, блок 34 регистров, селектор 35 минимального кода. блок 36 управления настройкой, третий элемент ИЛИ 37 и шины контрольной информации 38, входных данных 39 и выходной информации 40. Блок 36 управления настройкой (фиг. 2) содерчит буферный регистр 41, четвертый элемент ИЛИ 42, преобразователь 43 параллельного кода в последов Отельный, регистр 44 сдвига, кольцевой регистр 45 сдвига. Устройство работает следующим образом. . Перед началом работы с выходов блока 36 на вторые входа блоков 4.1- 4.3 подаются настроечные коды, соответствующие настройке этих блоков на выполнение функции g(x+h,x,х ), на входы блоков 5.2 и 5.3 - коды, соответствующие настройке этих блоков на выполнение функции g(x, +h, х), на вход блока 6.3- код, соответствующий настройке этого бло ка на выполнение функции g(x , х, ), где h - некоторый заранее заданный шаг поиска, g - функция, (х, х ) - ее аргумент. После этого на шину 39 поступает начальное значение аргумента (х, х, , х), которое через элемент ИЛИ 37 записывается в блоки 4.1, 5.2 и 6.3. Результаты вычислений gCxi -3h, х S X „М , g(x;, X I , 2h, Х), gCXg , X/, ХдЗ +) с выхода : последнего каскада поступают . .в блок 34, а затем - в селектор 35. В последнем происходит сравнение полученных значений функции между собой и выделение минимального значения функции g.. В результате сравнения с выхода, соответствующего минимальному значению g, селектора 35 выдается 1, ас остальных выходов - О. Например, если выполняются условия . g(, х , x3)crg(x, x2+2h,xM и g(x+3h, х2 , x KgCx, x2,x3+h), то с первого выхода блока 35 выдается 1, а с остальных - О, если выполняются условия g(x , +2h, x3)g(x+3h, xS х ) и g(x, х +2h, .х ) g(x, х , ), то с второго выхода селектора 35 выдается 1, а с первого и третьего выходов - О. Аналогично селектор 35 работает в случае, если два значения g из трех равны между собой. Блок управления настройкой работает следующие образом. В исходном состоянии в регистре записаны коды настроек резервируемых блоков на выполнение функций g(x+h, x х), g(x x2+h,x), g(x, х, ). Каждый код настрой ки размещается в п разрядах регистра 45. Если на первый, второй и тре тий входы блока 36 поступает соответственно 1, О, О, то в регистр 4 параллельным кодом также записывается 1,0,0, при этом с первого и второго/выходов регистра 41 выдается соответственно 0,0, на первый и второй входы преобразователя 43 подается, соответственно, 0,0. В результате этого в регистр 44 последовательным кодом запишется (0), после сдвига содержимого регистра 4 вправо, на вход регистра 45 импульсов сдвига не поступает, поэтому с выходов регистра 45 на первые, вт рые и третьи выходы блока 36 поступ ют коды настройки, соответствующие выполнению функций g(x+h, х, х), g(x, , хз), g(x, xS ) соответственно. В этом случае шаг поиска минимума функции g по х равен 3, шаг по х равен 2, а шаг по X - 1. Если на первый, второй, третий входы блока 36 поступает соответственно О, 1, О, то в регистр 41 параллельным кодом записывается О, 1, О, при этом с выходов регистра 4 выдается соответственно О, 1, на пе вый, второй входы преобразователя 4 подается соответственно О, 1. В результате этого в регистр 44 последовательным кодом запишется О, 1. После сдвига содержимого регистра 44 вправо, на вход регистра 45 поступает один импульс сдвига, кото рый соответствует сдвигу содержимо54го регистра влево на п разрядов. В результате этого с выходов регистра 45 на первые, вторые и третьи выхода блока 36 поступают коды настройки, соответствующие выполнению функций g(x , , х) , g(x х , ), g(x+h, xS хО. После сдвига содержимого регистра 44 вправо, на вход регистра 45 поступают два импульса сдвига, которые соответствуют сдвигу .содержимого регистра 45 влево на 2празрядов. В результате этого с выходов ре гистра 45 на первые, BTOfftie и третьи выходы блока 36 поступают коды настройки, соответствующие выпол- -2 , нению функций g(x , х g(xV+h, х2,хЗ), g(x, x2+h, хО. В этом случае шаг поиска функции по х равен 3, шаг по х равен 2, а шаг по х - 1. Таким образом, после сравнения. в блоке 35 значений фзшкций g и выделения единицы с j-ro выхода блока 35, соответствующего наиболее успешному продвижению к минимуму, происходит настройка блоков 4.1,- 4.3 на выполнение функции g(). Тем самым реализуется максимальный шаг к мини-v муму g в наиболее выгодном направлении. . Полученные значения функции поступают на вход блоков 27 - 29, выполняющих g-1. Для реализации очередного шага поиска, минимальное значение аргумента через элементы И 3032 и1 ИЛИ 33 и 37 поступает на обрагботку в устройство и цикл определения очередного значения аргумента повторяется. Останов процесса происходит в том случае, если для текущего значения аргумента значения функции g на очередном шаге больше либо равны значениям функции g на предыдущем шаге. В этом случае значение g выдается на шину 40. Блоки 5.1 - 7.1, 6.2 - 7.2 и 7.3 используются для косвенного контроля каскадов 1 - 3. Наличие корреляционных связей между отказами различных блоков каскадов в интегральном исполнении позволяет применить косвенный контроль, КОТО1И.1Й не пересекается со штатным функционированием устройста. С целью проведения косвенного контроля на входы блоков 5.1 - 7.1, 6.2 - 7.2 и 7.3, настроенных на выпол5неняе тождественного преобразования .и на первые входы блоков 8.1 - 8.3 с шины 38 подается некоторая тестовая последовательность. При совладении информации, поступающей на входь блока 8.1 (,2,3), i-й каскад расценивается как исправный. В этом случае с прямого выхода блока 8.1 выдается потенциал, разрешаю щий прохождение информации с 1-го на следующий (1+1)-й каскад, а с ин версного выхода - запрещающий потен циал, который блокирует путь обхода данного i-ro-каскада. При несовпадении информации, поступающей на вх ды блока 8.1, 1-й каскад расценивается как неисправный. .В этон случае с прямого выхода блока 8.1 выдается запрещающий потенциал, ко5 :6 торый блокирует поступление информации на следующий (1+1)-й каскад, а с инверсного выхода - разрешающий потенциал, с помощью которого реализуется путь обхода отказавшего каскада. Таким образом, при отказе одного или нескольких каскадов выполняется обход отказавших каскадов. . . При последовательных отказах каскадов устройство не перестает работать, а лишь уменьшается длина шагов при поиске. Например, в случае, когда отказал один каскад, максимальная длина шага поиска уменьшается на единицу, а в случае, когда будет функционировать лишь один каскад, шаги поиска по всем направлениям станут одинаковыми и равными единице.

«/

2

«4

ffS

Фаг г

| Авторское свидете,льство СССР : 543941, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Однородная вычислительная среда | 1978 |

|

SU815725A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-07—Публикация

1980-10-27—Подача