схемы сравнения фаз сигналов группы ( ( 1...П-1), где 1 - число разрядов преобразуемого кода, соединен с четвертыми входами j-х (ijn) элементов И третьей группы и с (1+2)-ми входами 1 -X элементов И четвертой группы, выходы которых соединены с первыми входами соответствующих элементов И пятой группы, вторые входы которых соединены с единичными выходами соответствующих триггеров группы, нулевые выходы которых соединены с первыми входа ми соответствующих элементов И шестой группы, вторые входы которых соединены с выходами соответствующих элементов ИЛИ первой группы, первый и второй входы которы соединены соответственно с первым прямым и вторым прямым выходами h-и схемы сравнения фаз сигналов группы прямой выход i -и схемы сравнения фаз сигналов группы соединен с (1+2)-ми входами j -X элементов ИЛИ первор группы, выходы элементов И пятой и шестой групп соединены с первыми и вторыми входами соответствующих элементов ИЛИ второй группы, выходы которых являются выходами преобразователя, первый инверсный выход (-Й схемы сравнения фаз сигналов группы соединен с (i+1)-M входом П-го элемента И третьей группы и с (i+1)-M входом элемента И, причем в каждой из схем сравнения фаз сигна лов группы информационньй вход соединен с первыми входами первого и второго элементов И, выходы которых соединены соответственно с первым и вторым входами первого элемента ИЛИ, а через первый элемент НЕ информационный вход схемы сравнения фаз сиг налов соединен с первым входом первого элемента И группы, тактовый вход соединен с вторыми входами пер8вого и второго элементов И, первым входом третьего элемента И, первым входом второго элемента И группы, а через второй элемент НЕ - с.первым входом третьего элемента И группы и первыми входами четвертого и пятого элементов И, вторые входы которых соединены с информационными задержанными входом схем сравнения фаз сигналов и вторым входом второго элемента И группы и через третий элемент НЕ - с вторыми входами второго и третьего элементов И, выходы элементов И группы соединены с первыми входами соответствующих элементов ИЛИ группы, вторые входы которых соединены с входом сброса, а выходы которых соединены с информационными входами соответствующих триггеров, счетный вход первого триггера соединен с выходом пятого элемента И, третий и четвертый входы которого соединены соответственно с инверсными выходами второго и третьего триггеров, счетные входы которых соединены соответственно с выходами первого элемента ИЛИ и третьего элемента И, третий вход которого соединен с инверсным выходом второго триггера, а четвертый вход соединен с выходом первого элемента НЕ и с третьим входом четвертого элемента И, выход которого соединен с третьим входом третьего элемента ИЛИ группы, прямой выход первого триггера соединен с третьим входом первого элемента И, прямой выход второго триггера соединен с вторь1ми входами первого и второго элементов И группы, прямой и инверсный выходы второго и третьего триггеров соответственно являются первыми и вторыми прямыми и инверсньми выходами схемы сравнения фаз сигналов ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ магнитной записи цифровой информации | 1984 |

|

SU1229809A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА ГРЕЯ В ПАРАЛЛЕЛЬНЫЙ ДВОИЧНЫЙ КОД | 2003 |

|

RU2248033C1 |

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1988 |

|

SU1557680A2 |

| Устройство для определения экстремумов | 1986 |

|

SU1386988A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА АНАЛОГОВОЙ ИНФОРМАЦИИ В ЦИФРОВУЮ ВЫЧИСЛИТЕЛЬНУЮ МАШИНУ | 1991 |

|

RU2006926C1 |

| Преобразователь кода Грея в двоичный код | 1982 |

|

SU1087983A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1693724A1 |

| Устройство для формирования кодовых последовательностей | 1988 |

|

SU1554115A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1986 |

|

SU1388997A1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

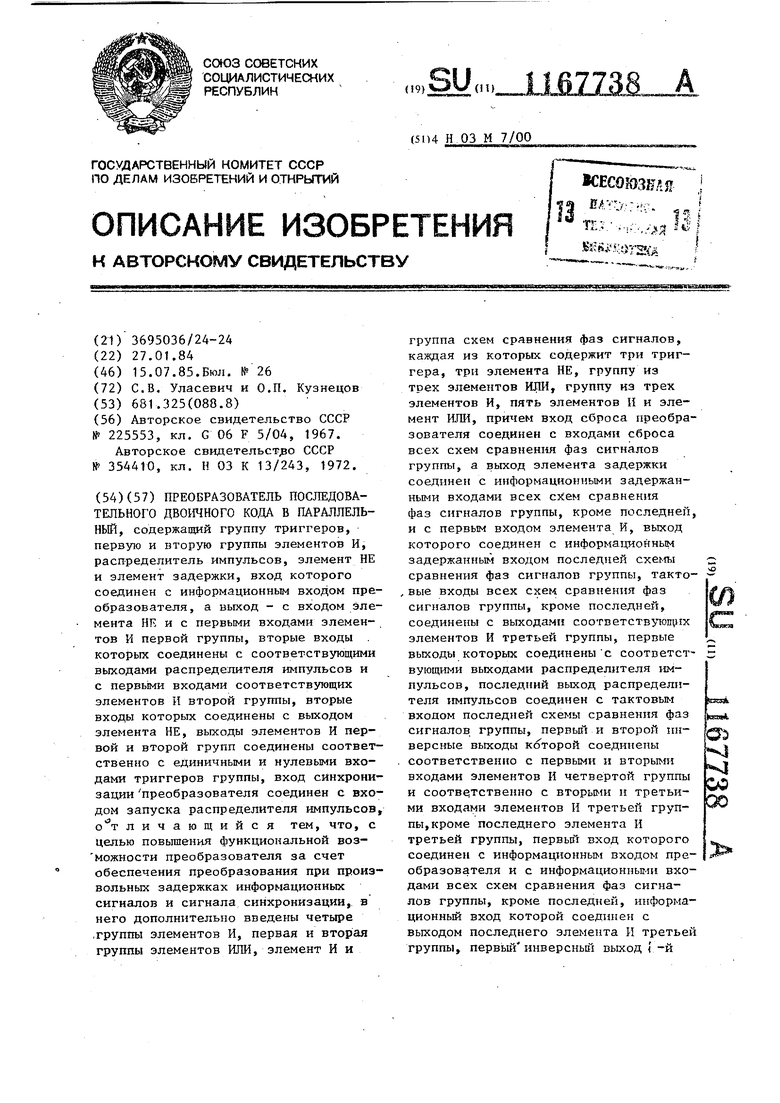

ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ, содержащий группу триггеров, первую и вторую группы элементов И, распределитель импульсов, элемент НЕ и элемент задержки, вход которого соединен с информационным входом преобразователя, а выход - с входом элемента НК и с первыми входами элемен- . тов И первой группы, вторые входы . которых соединены с соответствующими выходами распределителя импульсов и с первьЫи входами соответствующих элементов Н второй группы, вторые входы которых соединены с выходом элемента НЕ, выходы элементов И первой и второй групп соединены соответственно с единичными и нулевыми входами триггеров группы, вход синхронизации преобразователя соединен с входом запуска распределителя импульсов, о тличающийся тем, что, с цепью повышения функциональной возможности преобразователя за счет обеспечения преобразования при произвольных задержках информационных сигналов и сигнала синхронизации, в него дополнительно введены четыре .группы элементов И, первая и вторая группы элементов ИЛИ, элемент И и группа схем сравнения фаз сигналов, каждая из которых содержит три триггера, три элемента НЕ, группу из трех элементов РШИ, группу из трех элементов И, пять элементов И и элемент ИЛИ, причем вход сброса преобразователя соединен с входами сброса всех схем сравнен11я фаз сигналов группы, а выход элемента задержки соединен с информационными задержанными входами всех схем сравнения фаз сигналов группы, кроме последней, и с первым входом элемента И, выход которого соединен с информаи;ионным задержанным входом последней схемы сравнения фаз сигналов группы, такто, вые входы всех схем сравнения фаз сигналов группы, кроме последней, соединены с выходами соответствующих элементов И третьей группы, первые выходы которых соединеныс соответствующими выходами распределителя импульсов, последний выход распределителя импульсов соединен с тактовым входом последней схемы сравнения фаз оя«1 сигналов группы, первьш и второй инаэ версные выходы кб торой соединены -ч соответственгю с первыми и вторыми « входами элементов И четвертой группы 00 и соответственно с вторыми и третьими входами элементов И третьей группы, кроме последнего элемента И третьей группы, первьй вход которого соединен с информационным входом преобразователя и с информационньии входами всех схем сравнения фаз сигналов группы, кроме последней, информационный вход которой соединен с выходом последнего элемента И третьей группы, nepBbuV инверсньй выход Г-и

I

Изобретение относится к вычислительной технике и предназначено для систем передачи данных с временным разделением каналов.

Целью изобретения является повышение функциональной надежности за

счет обеспечения преобразования при произвольных задержках информационных сигналов и сигнала синхронизации,

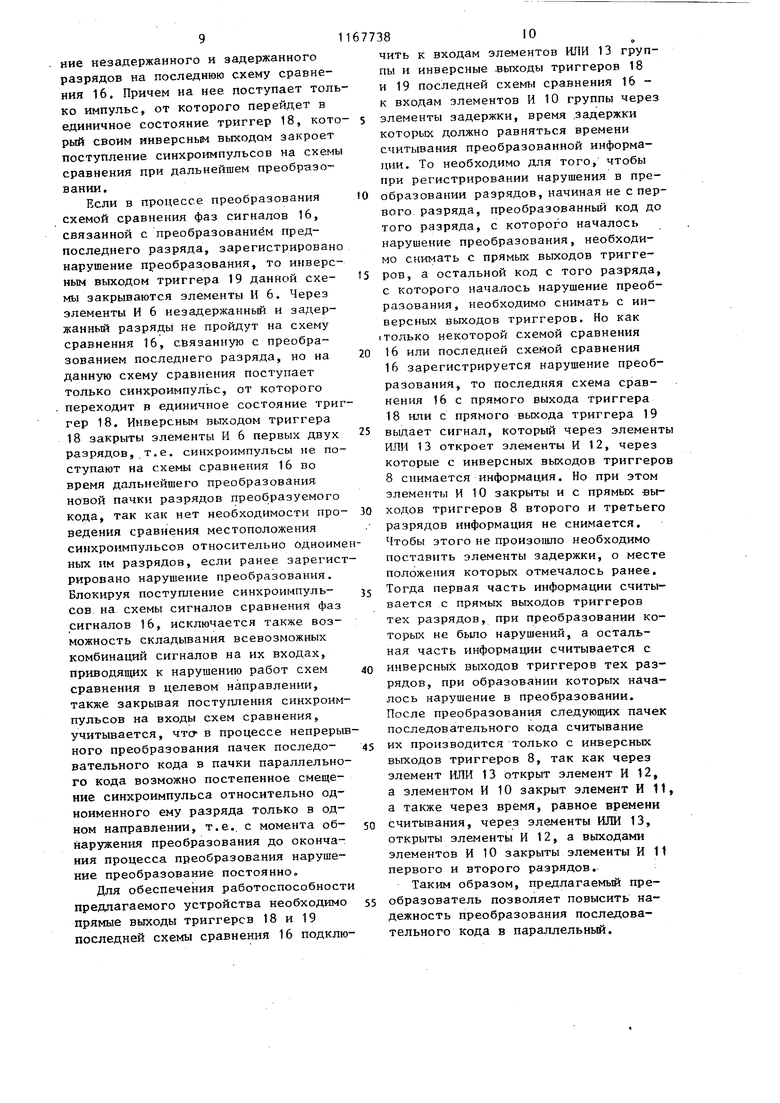

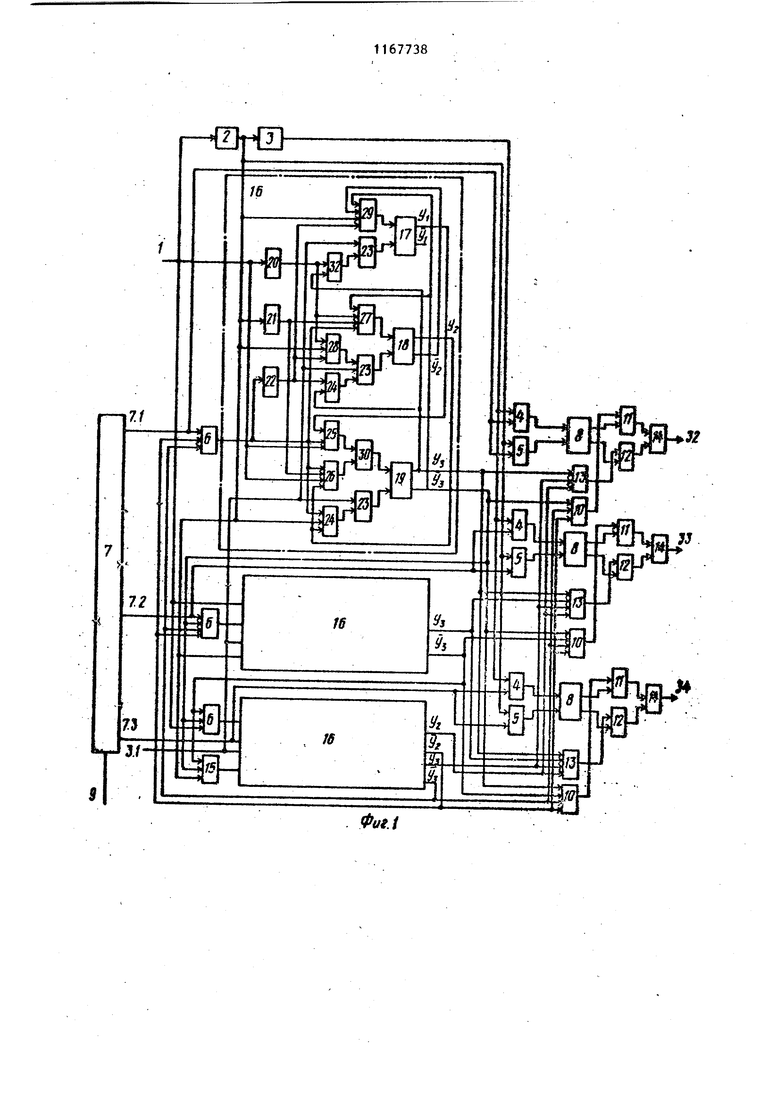

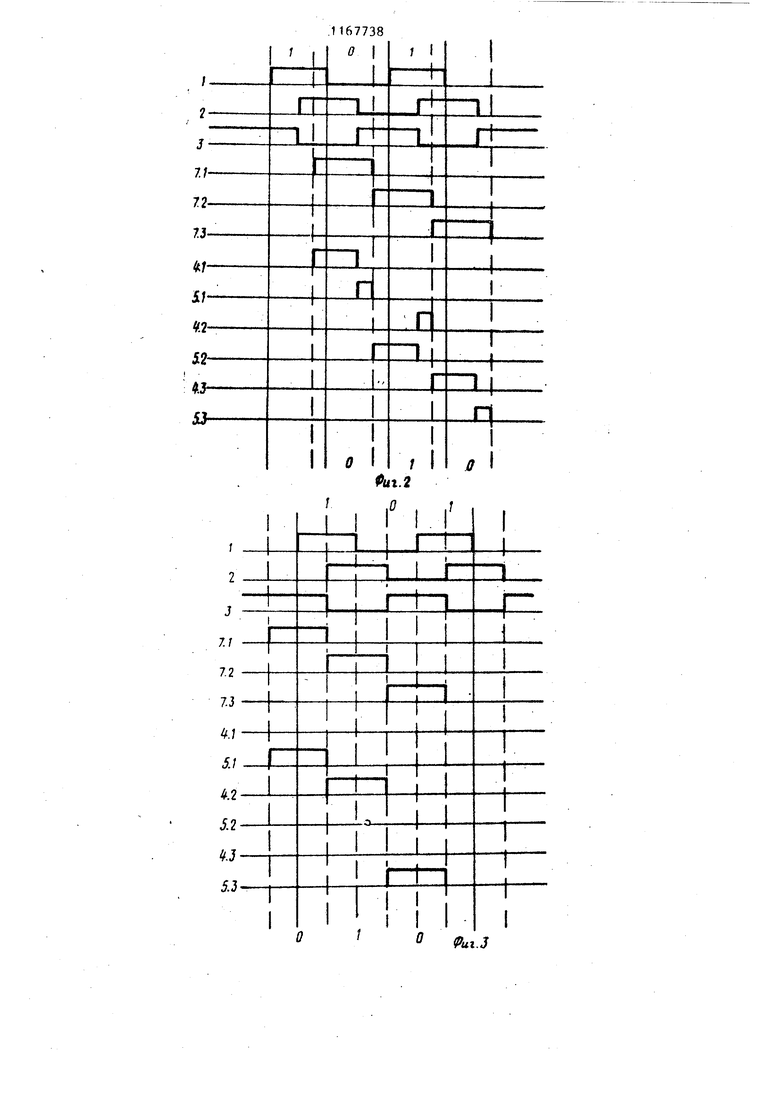

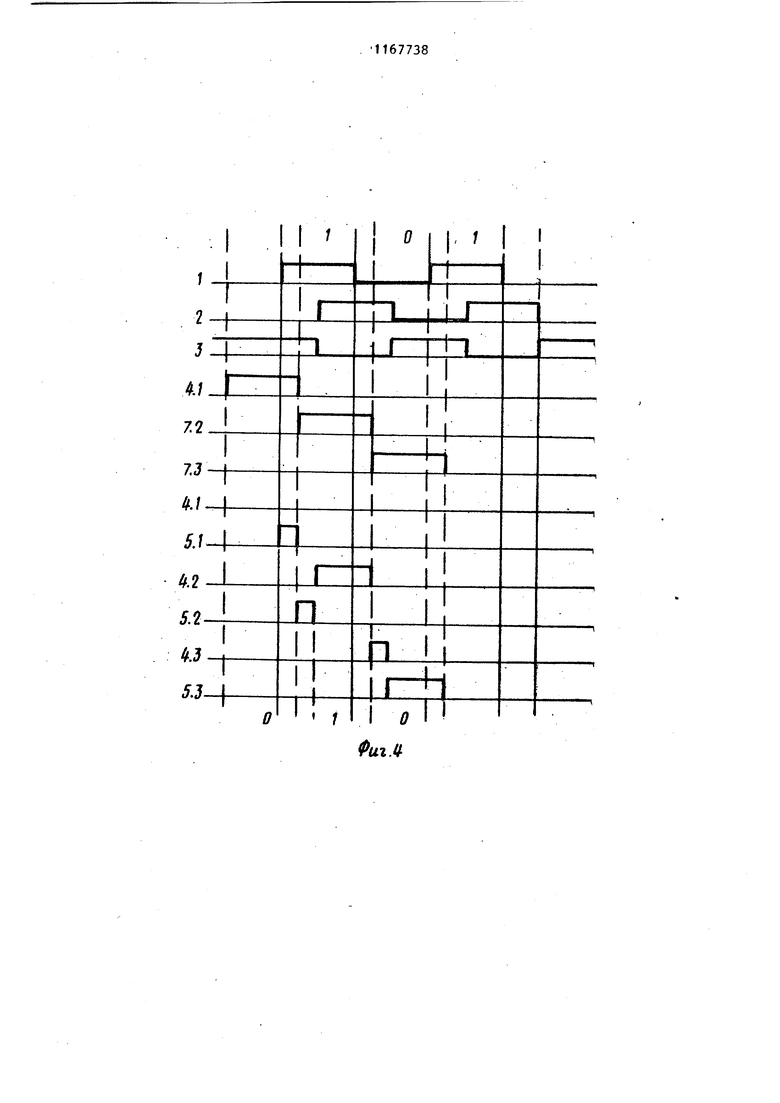

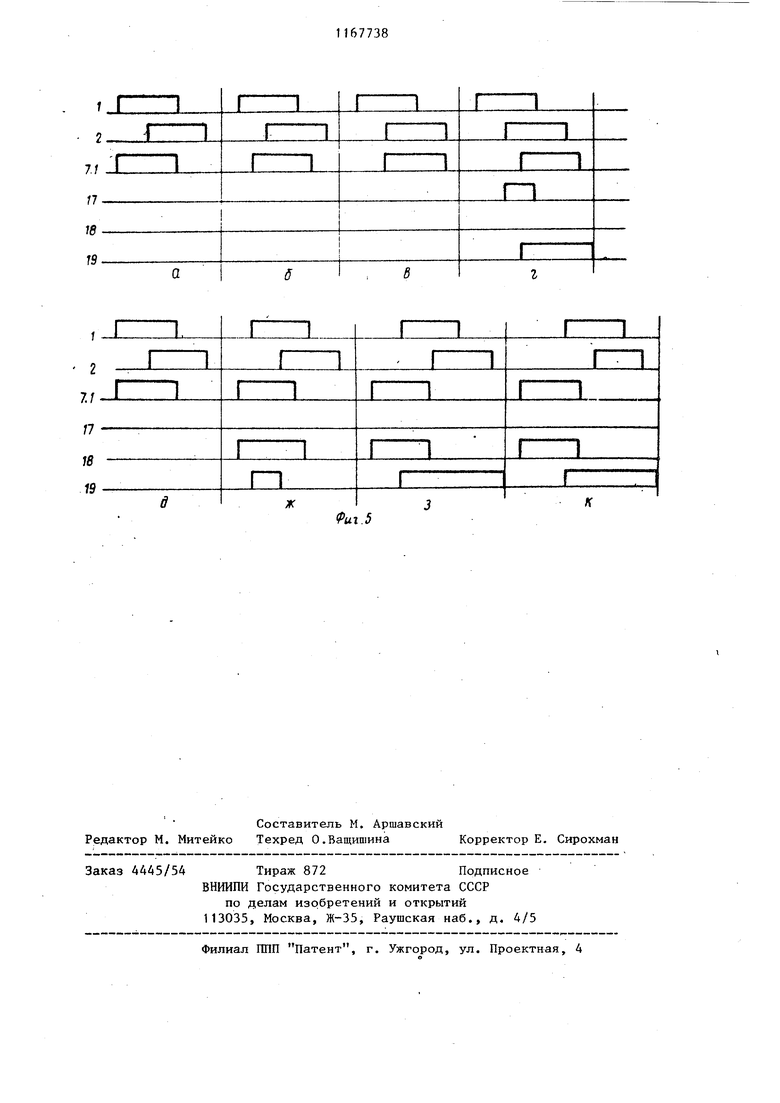

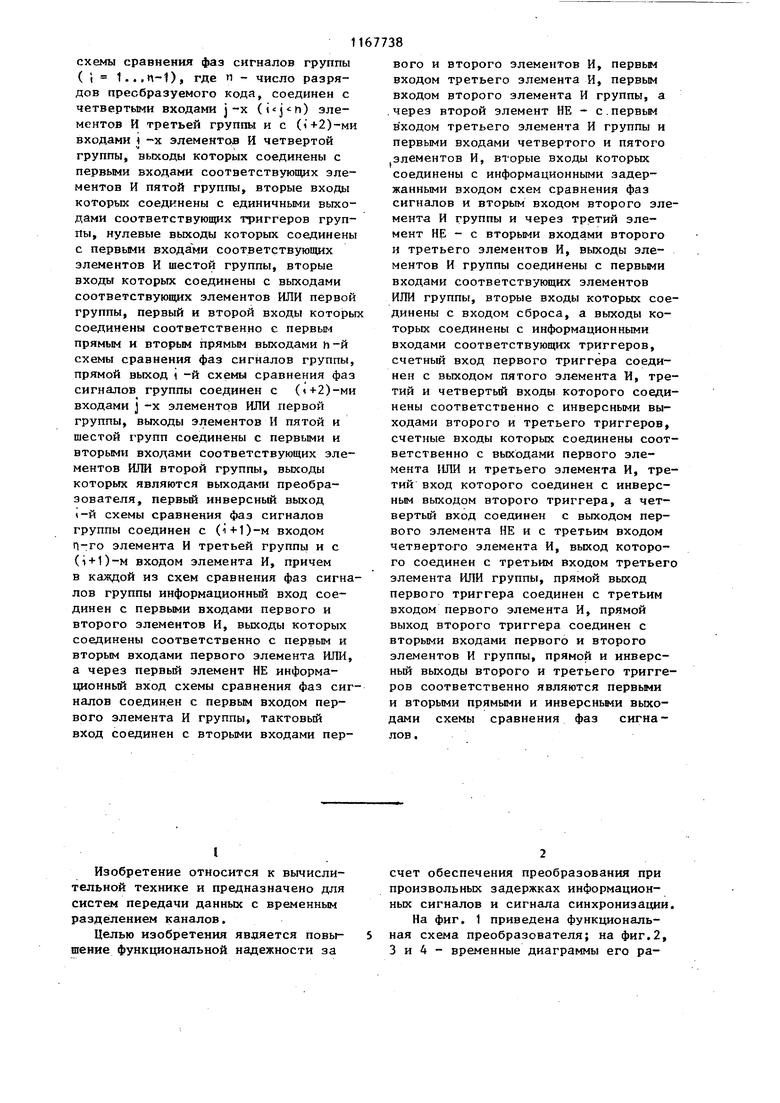

На фиг. 1 приведена функциональная схема преобразователя; на фиг.2, 3 и 4 - временные диаграммы его работы, где цифровые обозначения показывают принадлежность диаграмм v. соответствующему элементу схемы. Преобразователь последовательного кода в параллельный соедржит информа ционный вход 1 преобразователя, элемент задержки 2, элемент НЕ 3, группы элементов И 4, 5 и 6, распределитель импульсов 7, группу триггеров 8 вход 9 синхронизации преобразователя соединен с входом запуска распределителя импульсов, группы элементов И 10 - 12, первую и вторую группы элементов ИЛИ 13 и 14, элемент И 15 и группу схем сравнения фаз сигналов 16, Каждая из схем сравнения фаз сигналов содержит триггеры 17 - 1.9, элементы НЕ 20 - 22, группу элементов ИЛИ 23, группу элементов И 24, элементы И 25 - 29.и элемент ИЛИ ЗО. Входы сброса схем сравнения фаз сигналов 16 соединены с входом сброса преобразователя 31. Выходы элементов ИЛИ 14 соединены с выходами 32 - 34 преобразователя. На временной диаграмме (фиг.5) представлены только первые разряды и их синхроимпульсы, так как этого достаточно для отражения существа работы устройства. Взят крайний случай, т.е. длительность символа равна длительности синхроимпульса. Устройство для преобразования последовательного двоичного кода работает следующим образом. Сигнал информационной последовательности с длительностью импульса, равной длительности символа (телегра ный сигнал), поступает на вход 1 и на элемент задержки 2, С выхода элемента НЕ 3 снимается инверсный сигнал. Когда взаимный сдвиг синхроимпуль сов и информационных сигналов не пре вышает предела задержки, создаваемого элементом задержки 2 (ситуации, обозначенные а, S , i на фиг. 5),. то задержанные прямой и инверсный сигна лы поступают на элементы И 4 и 5, прямой сигнал поступает на элементы И 4 группы, }инверсный - на элементы И 5 группы. На вторые входы данных элементов И поступают синхроимпульсы, поступающие с распределите ля импульсов, а с выходов элементов И 4 и 5 выходные сигналы поступают на входы установки 1 и О триггеров 8 соответственно. В триггер каждого из 1 384 ра рядов в течение первой половины дш тел1 иостн соотиотстмующего синхроимпульса может записываться ложный, т.е. сопгнетствующий соседнему разряду, сигнал, но в течение второй полопины записывается сигнал, соответствующий значению данного. При этом триггеры 18, 19 и 17 . схем сравнения фаз сигналов 16 находятся в нулевом состоянии, хотя и поступают прямые информациоиные разряды на элемент И 26, а синхроимпульсы поступают на .вход элемента И 25, но не проходят через них на счетный вход триггера 19, так как элемент И 26 закрыт прямым выходом триггера 18, а элемент И 25 - прямым выходом триггера 17. До поступления информации на устройство преобразования триггеры 17, 18 и 19 схем сравнения фаз сигналов 16 находятся в нулевом состоянии, а элементы И 29 подготовлены, к открытию инверсными выходами триггеров 18 и 19L и выходом элемента НЕ 22, элементы И 27 подготовлены к . открытию инверсньм выходом триггера 19 и выходами элементов НЕ 20 и 21. Элементы И 25 закрыты прямьми выходами триггеров 17, элементы И 26 подготовлены к открытию выходами элементов НЕ 21, элементы И 24 закрыты прямыми выходами триггеров 19 и 18. При одновременном поступлении информационного разряда и синхроимпульса на преобразователь они поступают на входы элементов И 25, И 26, И 27, И 25, И 26, И 24, но не пройдут через них на счетные входы триг(Геров 18 и 19, так как элемент И 27 закроется выходом элемента НЕ 20, ;на входе которого присутствует информационный сигнал, элементы И 25 и 26 продолжают находиться в закрытом состоянии, так как триггеры 18 и 17 находятся в нулевом состоянии и элемент И 29 закрьшается выходом элемента НЕ 22, на входе которого присутствует синхроимпульс. При появлении информационного разряда сигнал с выхода .элемента задержки 2 на входах И 29 и 24 не пройдет через них, также сигнал с выхода элемента задержки 2 появится на входе элемента НЕ 21,который выходом закроет элементы И 27 и 26. После исчезновения информационного разряда и синхроимпульса продолает присутствовать информационный сигнал с выхода элемента задержки 2, но и он не проходит через элементы И 29 и 24, так как они продолжают находиться закрытыми. Таким образом, для данной ситуации (фиг. 5q) триггеры 18 19 и 17 со схем сравнения 16 находятся в нулевом состоянии. Инверсньм выходом триггера 19 открыт элемент И 10, через который снимается результат преобразования с прямого выхода триггера 8. С выхода элемента И 5 результат далее через элемент И 12 поступает на выход 34 преобразователя. При отставании переднего фронта синхроимпульсов от информационных разрядов в пределах времени задержки (фиг. 58) вначале поступают информационные разряды, которые поступают на входы элементов И 25 и 26, но не проходят через них на счетный вход триггера 19. Затем одновременно с информационным разрядом появляется синхроимпульс, для которого схема сравнения 16 ведет себя аналогично как для ситуации, представленной на фиг. 5а. Далее незадержанный информационный разряд исчезает, но одновременно с задержанным информационны разрядом продолжает присутствовать синхроимпульс. Задержанный разряд не проходит через закрытые элементы И 29 и 24 на счетные выходы триггеров 19 и 17, так как элемент И 29 закрыт выходом элемента НЕ 22, на входе которого присутствует синхроимпульс, а элемент 24 закрыт прямым выхрдом триггера 18, так как на его счетном входе отсутствует сигнал с выхода элемента И 27, закрытого выходом элемента НЕ 21, на входе которого в этот момент присутствует сигнал с выхода элемента задержки 2 Синхроимпульс также не проходит чере элементы И 25 и 26. При наличии толь ко синхроимпульса триггеры 18, 19 и 17 схемы сравнения 16 не сработают аналогично ситуации а , представленной на фиг. 5. Преобразованная информация снимается с прямого выхода триггера 8 через элементы 11, ШШ 14 так как триггер 19 находится в нулевом состоянии. При совпадении синхроимпульса с задержанным информационным разрядом (фиг. 5fc ) триггеры 18, 19 и 17 схемы сравнения 16 не сработают, аналои 8 , представленгично ситуациям а ным на фиг. 5, и преобразованная информация снимается аналогично как в ранее рассмотренных ситуациях. При выходе переднего фронта синхроимпульса из зоны времени задержки (фиг. 5 г) вначале появляется информационный разряд. При этом все триггеры схемы сравнения 16 находятся в нулевом состоянии аналогично ранее рассмотренным ситуациям а , , В фиг. 5. Затем одновременно появляется незадержанный и задержанный информационные разряды. При этом задержанный разряд проходит через элемент И 29, открытый выходом элемента НЕ 22, на счетный вход триггера 17, который переходит в единичное состояние и своим прямым выходом подготавливает к открытию .элемент И 25. Когда одновременно появляются незадержанный разряд и синхроимпульс, то синхроимпульс и незадержанный информационный разряд проходят через элемент И 25, далее через элемент ИЛИ 30 на счетньй вход триггера 19, который переходит в единичное состояние и своим прямым выходом подготавливает к открытию элемент И 24. При этом триггер 17 продолжает находиться в нулевом состоянии, так как элемент И 24 по другому входу закрыт выходом элемента НЕ 20. После исчезновения незадержанного информационного разряда продолжают одновременно присутствовать задержанный информационный разряд и синхроимпульс. В момент исчезновения незадержанного информационного разряда с входа элемента НЕ 20 открьшается элемент И 24, через который с прямого выхода триггера 19 проходит сигнал, далее проходит через элемент ИЛИ 23 на сбросовый вход триггера 17 и переводит его в нулевое состояние. После исчезновения задержанного информационного разряда продолжает присутствовать синхроимпульс, который не проходит через элемент И 27, закрытый инверсным выходом триггера 19, е проходит через элементы И 25, 26 и 24, закрытые прямым выходом риггера 17. Когда отсутствуют сигналы на входах элементов схемы сравения 16, то триггер 19 продолжает аходиться в единичном состоянии, то свидетельствует о том, что зареистрирован выход переднего фронта инхроимпульса из области времени

7

задержки соответствующего ему разряда, что приводит к искажению результата преобразования (фиг.2). Поэтому инверсньм выход триггера 19 через элемент ИЛИ 10 закрывает элемент И 11, а прямой выход триггера 19 через элемент RTO 13 открывает элемент И 12, через который результат преобразования снимается с инверсного выхода триггера 8. Также инверсный выход триггера 19 закрывает элементы И 6 и И 15 для того, чтобы синхроимпульс не поступал через элемент И 6 на схему сравнения 16, относящуюся к второму разряду, а через элемент И 6 - незадержанный разряд, через элемент И 6 - незадержанный разряд, через элемент И 15 - задержанный разряд на схему сравнения 16, относящуюся к третьему разряду, так как на входах схем сравнения 16 могут складываться всевозможные кодовые комбинации, образуемые в результате смещения синхроимпульсов относительно информационных разрядов и нарушающие работу схем сравнения в целевом назначении. Хотя синхроимпульсы не поступают на элементы последующих схем сравнения, но на их входы поступают задержанные и незадержанные информационные разряды,- которые вызывают срабатьгоание триггеров 17, но они не участвуют в коррекции значений преобразуемых разрядов. Хотя задержанные и незадержанные разряды не поступают на элементы схемы сравнения 16, связанной с преобразованием последнего разряда, но на юс входы поступает синхроимпульс .которьй вызьшает срабатывание триггера 18, который не участвует в коррекции.

При поступлении вначале синхроимпульса, а затем совместно с ним информационного разряда (фиг. 5йс) переходит вначале в единичное состояние триггер 18 от синхроимпульса, проходящего на счетньй вход триггера через элемент И 27, подготовленный к открытию. При одновременном поступлении на схему сравнения 16 синхроимпульса и незадержанного информационного разряда переходит в единичное состояние триггер 19 от информационного разряда, проходящего на счетный вход триггера через элемент И 26, подготовленный к открытию, да67738В

лее через элемент ИЛ11 30. При этом григгер 18 продолжает находиться в единичном состоянии. В момент одновременного поступления синхроимпулъ5 са, незадержанного и задержанного информационного разряда триггер 19 возвращается в исходное (нулевое) состояние сигналом с выхода элемента И 24, далее через элемент ИЛИ 23, поto ступающим на его сбросовый вход. Триггер 19 возвращается в исходное состояние, так как для данной ситуации (ситуация Яг) нет необходимости коррекции преобразуемого разряда. 15 Триггер 18 возвращается в нулевое состояние в момент постухшения на схему сравнения 16 только задержанного разряда.

При выходе переднего фронта синхроимпульса из зоны времени задержки и нахождении заднего фронта в зоне времени задержки (фиг.5, к ) вначале переходит в единичное состояние триггер 18., а затем -. в единичное состояние триггер 19, т.е. схема сравнения 16 работает аналогично ситуации :К. В момент поступления на схему сравнения 16 только незадержанного и задержанного разрядов или только незадержанного разряда триггер 18 возвращается в нулевое состояние сигналом с выхода элемента И 24 через элемент ИЛИ 23 группы, поступающим на его сбросовьй вход. Триггер 19 при этом 5 продолжает находиться в единичном состоянии, так как элемент И 24 закрыт. Таким образом триггер 19 з аствует в коррекции преобразуемого разряда в данный момент и всех последую0 Щих разрядов, т.е. корректирует, как и в случае г .

Для приведения триггеров 18, 19 и 17 схем сравнения фаз сигналов 16 в исходное состояние после прекращения процесса преобразования кода, который для Данного устройства может быть непрерывным, необходимо подать сигнал Сброс по входу 31, который через элементы ИЛИ 23 груи-пы поступает на сбросовые входы триггеров 18, 19 и 17 соответственно. Инверсный выход триггера 18 последней схемы сравнения фаз сигналов 16 исполгзуется для того, чтобы при 5 :регистрации предыдущей схемой сравнения 16 в преобразовании инверсный выход триггера 19 предпоследней схемы сравнения 16 блокировал поступление незадержанного и задержанного разрядов на последнюю схему сравнения 16. Причем на нее. поступает тол ко импульс, от которого перейдет в единичное состояние триггер 18, кот рый своим инверсньм выходом закроет поступление синхроимпульсов на схем сравнения при дальнейшем преобразовании. Если в процессе преобразования схемой сравнения фаз сигналов 16, связанной с преобразованием предпоследнего разряда, зарегистрирован нарушение преобразования, то инверс ным выходом триггера 19 данйой схемы закрываются элементы И 6. Через элементы И 6 незадержанный и задержанный разряды не пройдут на схему сравнения 16, связанную с преобразованием последнего разряда, но на данную схему сравнения поступает только синхроимпульс, от которого переходит в единичное состояние три гер 18. Инверсным выходом триггера 18 закрыты элементы И 6 первых двух разрядов,.т.е. синхроимпульсы не по ступают на схемы сравнения 16 во время дальнейшего преобразования новой пачки разрядов преобразуемого кода, так как нет необходимости про ведения сравнения местоположения синхроимпульсов относительно одноим ных им разрядов, если ранее зарегис рировано нарушение преобразования. Блокируя поступление синхроимпульсов на схемы сигналов сравнения фаз сигналов 16, исключается также возможность складывания всевозможных комбинаций сигналов на их входах, приводящих к нарушению работ схем сравнения в целевом направлении, также закрывая поступления синхроим пульсов на входы схем сравнения, учитывается, что- в процессе непреры ного преобразования пачек последовательного кода в пачки параллельно го кода возможно постепенное смещение синхроимпульса относительно одноименного ему разряда только в одном направлении, т.е.. с момента обнаружения преобразования до окончания процесса преобразования нарушение преобразование постоянно. Для обеспечения работоспособност предлагаемого устройства необходимо прямые выходы триггеров 18 и 19 последней схемы сравнения 16 подклю 3810 чить к входам элементов ИЛИ 13 группы и инверсные выходы триггеров 18 и 19 последней схемы сравнения 16 к входам элементов И 10 группы через элементы задержки, время задержки которых должно равняться времени считывания преобразованной информации. То необходимо для того, чтобы при регистрировании нарушения в преобразовании разрядов, начиная не с первого разряда, преобразованный код до того разряда, с которого началось нарушение преобразования, необходимо снимать с прямых выходов триггеров, а остальной код с того разряда, с которого началось нарушение преобразования, необходимо снимать с инверсных выходов триггеров. Но как (ТОЛЬКО некоторой схемой сравнения 16 или последней схемой сравнения 16 зарегистрируется нарушение преобразования, то последняя схема сравнения 16 с прямого выхода триггера 1В или с прямого выхода триггера 19 выдает сигнал, который через элементы ИЛИ 13 откроет элементы И 12, через которые с инверсных выходов триггеров 8 снимается информация. Но при этом элементы И 10 закрыты и с прямых выходов триггеров 8 второго и третьего разрядов информация не снимается. Чтобы этого не произошло необходимо поставить элементы задержки, о месте положения которых отмечалось ранее. Тогда первая часть информации считывается с прямых выходов триггеров тех разрядов, при преобразовании которых не было нарушений, а остальная часть информации считывается с инверсных выходов триггеров тех разрядов, при образовании которых началось нарушение в преобразовании. После преобразования следующих пачек последовательного кода считывание их производится только с инверсных выходов триггеров 8, так как через элемент ИЛИ 13 открыт элемент И 12, а элементом И 10 закрыт элемент И 11, а также через время, равное времени считывания, через элементы ИЛИ 13, открыты элементы И 12, а вьпсодами элементов И 10 закрыты элементы И 11 первого и второго разрядов. Таким образом, предлагаемый преобразователь позволяет повысить надежность преобразования последовательного кода в параллельный.

Фиг Л

18

rs

| Авторское свидетельство СССР № 225553, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ ПОСЛЕДОВАТЕЛБНОГО | 0 |

|

SU354410A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-07-15—Публикация

1984-01-27—Подача