Изобретение относится к вычислительной технике и может быть использовано при проектировании буферных запоминающих устройств систем сбора и обработки информации.

Цель изобретения - расширение функциональных возможностей устройства путем синхронизации моментов подготовки и сбора данных.

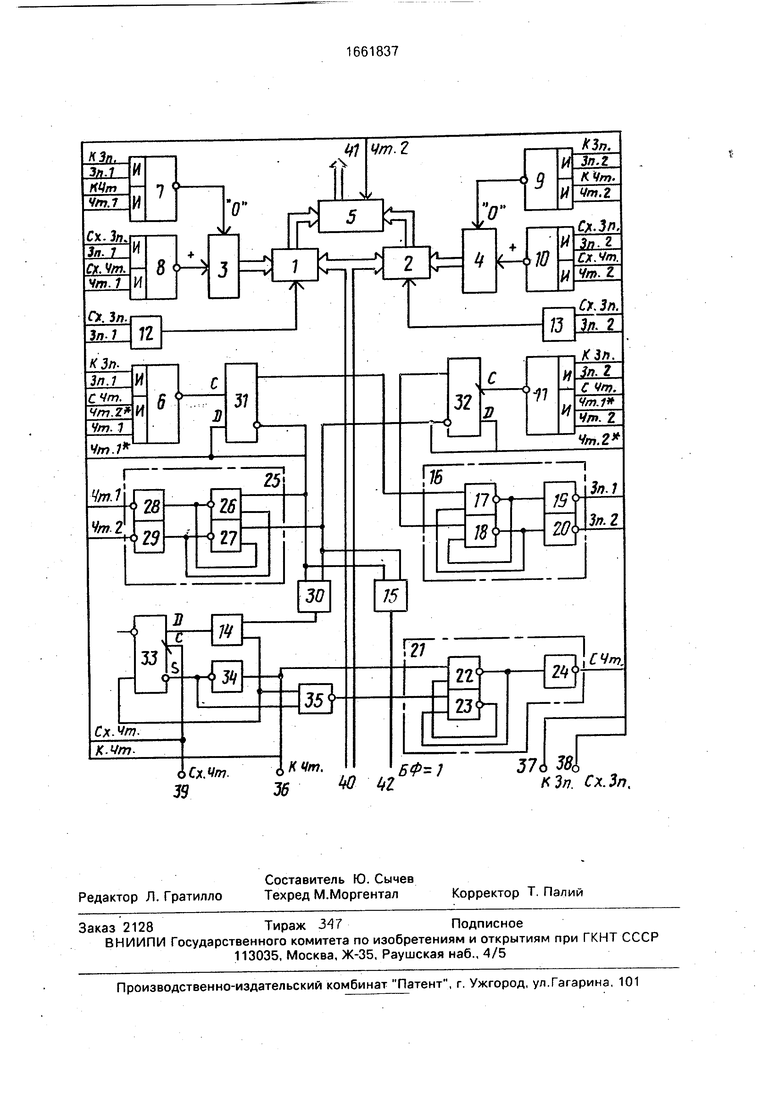

На чертеже приведена структурная схема буферного запоминающего устроцства. На схеме обозначены первый 1 и второй 2 блоки памяти, первый 3 и второй 4 счетчики адреса обращения, мультиплексор 5, первый 6, второй 7, третий 8, четвертый 9, пятый 10, шестой 11 элементы И-ИЛИ-НЕ, первый 12, второй 13, третий 14, четвертый 15 элементы И, схема 16 приоритета заявок записи, реализованная на первом 17 и втором 18 элементах И-НЕ и первом 19 и втором 20 элементах НЕ, схема 21 приоритета

заявок на переключение режимов блоков памяти и блокировки переключения, реализованная на третьем 22 и четвертом 23 элементах И-НЕ и третьем элементе НЕ 24, схема 25 приоритета заявок чтения, реализованная на пятом 26 и шестом 27 элементах И-НЕ и четвертом 28 и пятом 29 элементах НЕ, элемент ИЛИ 30, первый 31 и второй 32 триггеры режимов, третий триггер 33 состояния чтения буфера, шестой элемент НЕ 34, седьмой элемент И-НЕ 35, первый управляющий вход 36 устройства Конец чтения (КЧт.), второй управляющий вход 37 устройства Конец записи (КЗп)/ третий управляющий вход 38 устройства Синхронизация записи (Сх.Зп), четвертый управляющий вход 39 устройства Синхронизация4 чтения (Сх.Чт.), информационные входы 40 устройства, информационные выходы 41 устройства, управляющий выход 42 устройства, Буфер полон (БФ-1).

о а

00 СлЭ

v|

Устройство работает следующим образом.

В исходном состоянии по цепям начальной установки (не показаны) триггеры 31 и 32 устанавливаются в единичное состояние Запись, триггер 33 - в единичное состояние Чтение буфера, счетчики 3 и 4 сбрасываются. Управляющие входы 36 - 39 устройства и управляющий выход 42 имеют низкий уровень, Заявки записи высокого уровня поступают на вход схемы 16 приоритета (Сх.Пр.1), которая представляет собой триггер. При поступлении на его установочные входы потенциалов высокого уровня он установится в нулевое состояние по тому установочному входу, который поступил раньше. Предположим, что низкий уровень установился на выходе 17 (заявка на запись от триггера 31 пришла первой). Через инвертор 19 сигнал высокого уровня, воздействуя на вторые входы элементов 6-8 и 12, подготовит их для формирования соответствующих импульсов в режиме записи.

Низкий уровень с инверсных выходов (нет заявок на чтение) с триггеров 31 и 32 поступает на вход Сх.Пр.З, реализованной аналогично Сх.Пр.1, В связи с отсутствием заявок чтения на выходе инверторов 28 и 29 Сх.Пр.З сформируются сигналы низкого уровня, которые, поступая на входы элементов 6-11, блокируют формирование управляющих сигналов в режиме чтения.

Одновременно потенциалы низкого уровня с инверсных выходов триггеров 31 и 32 поступают на входы элементов И 15, ИЛ И 30, формируя их на выходах соответственно сигналы низкого уровня БФ-1 и Нет информации. Сигнал с выхода элемента ИЛИ 30 и прямого выхода триггера 33 поступает на входы элемента И 14, выход которого подключен к входу D триггера 33. В исходном состоянии на выходе элемента ИЛИ 30 и, следовательно, на входе триггера 33 - низкий уровень. Сигнал высокого уровня с прямого выхода триггера 33 поступает на второй вход элемента И-НЕ 35, на первом входе которого в исходном состоянии - высокий уровень. На выходе элемента И-НЕ 35 сформируется сигнал низкого уровня (нет заявки блокировки переключения режимов), который поступает на второй вход Сх.Пр.21 в качестве заявки блокировки сброса режима чтения блоков памяти. На первый вход Сх.Пр.21 через инвертор 34 поступает заявка на сброс режима чтения (управляющий вход 36 устройства КЧт). В исходном состоянии заявки на сброс режима чтения нет, на первом входе Сх.Пр.21 - низкий уровень. На выходе инвертора 24 Сх.Пр.2 сигнал низкого уровня, который запрещает по третьим входам элементов 6 и 11 формирование сигнала Сброс режима чтения (СЧт.) соответственно блоков 1 или 2 памяти. Работа Сх.Пр.2 аналогична работе

Сх.Пр.1 за исключением того, что в Сх.Пр.2 используется только один выход - СЧт.

При поступлении на вход 40 устройства данных в сопровождении сигнала Сх.Зп. 38 положительной полярности начинается

0. цикл записи в буфер. Сх.Зп. поступает на первые входы элементов 8 и 12, формируя на их выходах соответственно сигналы модификации содержимого счетчика 3 адреса и сигнал режима работы блока 1 памяти

5 Запись. Модификация счетчика 3 осуществляется по заднему фронту сигнала Сх.Зп. По концу записи в блок 1 памяти блока данных заданной длины на вход 37 устройства поступит сигнал КЗп, положительной поляр0 ности. На выходе элемента 6 при совпадении сигналов КЗп, и Зп,1 сформируется сигнал, по заднему фронту которого триггер 31 переключится в состояние Чтение - высокий уровень на инверсном выходе. На

5 входе Сх.Пр.1 исчезнет заявка записи от первого блока памяти и на ее выходе Зп, 2 сформируется сигнал высокого уровня, который поступит на входы элементов 13, 9,10 и 11 для формирования сигналов управле0 ния записью во второй блок 2 памяти. Заявка чтения с инверсного выхода триггера 31 поступает на первый вход Сх.Пр.З и формирует на ее выходе сигнал высокого уровня Чт, 1, который поступает на входы элементов

5 6-8, подготавливая их для формирования сигналов управления в режиме чтения, Запись информации во второй блок памяти происходит аналогично. После переключения триггера режима 32 второго блока памя0 ти в режим чтения на входе Сх.Пр.З присутствуют две заявки чтения. Так как от триггера 31 заявка пришла раньше, то на выходе Сх.Пр.З сформируется высокий потенциал Чт.1.

5 В режиме чтения на вход 39 устройства поступает сигнал Сх.Чт., который представляет собой пачку импульсов положительной полярности определенной длины и занимает определенное место в цикле опроса сис0 темы сбора информации. Сх.Чт. поступает на входы элементов 8 и 10 для формирования сигналов модификации счетчика адреса в режиме чтения блока памяти, заявка которого выбрана на Сх.Пр.З (высокий уровень

5 на одном из выходов Чт.1 или Чт.2). Если к приходу первого импульса пачки Сх.Чт. в буфере нет информации (не записан блок данных ни в один из блоков памяти), то на выходе элементов ИЛИ 30 и И 14 - низкий уровень, который указывает на отсутствие

информации в буфере. По переднему фронту первого импульса Сх.Чт. триггер 33 установится в нулевое состояние (низкий уровень - на выходе И 14 и входе D триггера 33). Низкий уровень с прямого выхода триггера 33 заблокирует прохождение сигнала о наличии информации в буфере с выхода элемента ИЛИ 30 на вход D триггера 33 и сфор- мирует через элемент 35 заявку на блокировку сброса режима чтения. Если во время пачки Сх.Чт. произойдет запись блока данных в один из блоков памяти (на выходе элемента ИЛИ 30 сформируется сигнал высокого уровня - есть информация), то триггер 33 не переключится в состояние Чтение, так как элемент И 14 заблокирован сигналом с прямого выхода триггера 33. В этом случае в систему сбора выдается информация с одного из блоков памяти (режим выборки накопителя блоков памяти установлен постоянно), которая установилась в нем при включении питания. Такой режим работы буфера будет продолжаться до тех пор, пока в буфер не будет загружен хотя бы один блок данных. По концу пачки Сх.Чт. на вход 36 устройства поступает сигнал КЧт., в качестве которого можно использовать любой сигнал синхронизации системы опроса, не попадающий в пачку Сх.Чт. Сигнал КЧт. через инвертор 34 устанавливает триггер 33 в состояние Чтение (высокий уровень на прямом выходе) и на время действия сигнала КЧт. формирует на элементе 35 заявку с триггера 33 на блокировку сброса режима чтения. Таким образом, на входе Сх.Пр.2 присутствуют две заявки: Сброс режима чтения (первый вход элемента 22) и Блокировка сброса режима чтения (первый вход элемента 23). Заявка блокировки сброса опережает заявку на сброс режима (она была, установлена в начале пачки Сх.Чт. при отсутствии информации в буфере) и, следовательно, на выходе Сх.Пр.2 сигнал СЧт. сформирован не будет. Если к приходу первого импульса пачки Сх.Чт. в буфер загружен хотя бы один блок данных, то на выходе элемента 30 сформируется сигнал высокого уровня, который через открытый элемент 14 поступает на вход триггера 33. По переднему фронту первого импульса Сх.Чт. триггер подтвердит свое состояние (останется в единичном состоянии). С приходом сигнала КЧт. положительной полярности на входах Сх.Пр.2 - опять две заявки на Сброс режима чтения и Блокировка сброса режима чтения. Заявка сброса режима чтения будет сформирована на время действия сигнала КЧт. и задержана по отношению к заявке сброса режима на время задержки элементов 34 и 35. Следовательно, заявка КЧт. будет записана в Сх.Пр. 2 и на выходе элемента 24 сформируется сигнал высокого уровня СЧт. который поступит на третьи входы элементов 6 и 11 для формирования сигналов 5 сброса режима чтения соответственно бло- ков 1 или 2 памяти. На пятые входы элементов 6 и 11 поступают разрешающие потенциалы заявок чтения Чт.1 или Чт. 2 с Сх.Пр.З. На четвертые входы элементов 6 и 10 11 с триггера 31 или 32 поступают заявки чтения соответственно первого блока памяти Чт.1 или второго Чт.2. Сигнал сброса режима чтения на выхде элементов 6 и 11 будет сформирован по сигналу СЧт. в слу- 15 чае, если на выходе элемента 6 будет установлен режим чтения первого элока памяти, а во втором блоке памяти будет подготовлен следующий блок данных если на выходе элемента 11 будет установлен режим чтения

0 второго блока памяти, а в первом блоке памяти будет подготовлен следующий блок данных. По сигналу с выходов элементов 6 или 11 соответственно триггер 31 или 32 переключается в режим записи очередного

5 блока данных. Если к приходу сигнала КЧт. в момент формирования сигнала СЧт. в нечитаемом блоке памяти не подготовлен оче- редной блок данных, то сигнал переключения режима чтения на выходах

0 элементов 6 или 11 сформирован не будет. С приходом очередной пачки Сх.Чт, будет . повторен цикл выдачи предыдущего блока данных, Счетчики адреса обращения в режиме чтения модифицируются по заднему

5 фронту сигналов, которые формируются из сигнала Сх.Чт. на элементах 8 или 11 в зависимости от выбранной заявки Чт.1 или Чт.2, В зависимости от заявки Чт,2, управляющей выбором входа мультиплексора 5, на выход

0 устройства поступают данные с блока 1 памяти (Чт,2 - низкий уровень) или с блока 2 памяти (Чт.2 - высокий уровень).

Если в буфере заняты под блоки данных оба блока памяти, то высокие уровни с ин5 версных выходов триггеров 31 и 32 поступят на входы элемента И 15 и сформируют на его выходе сигнал высокого уровня приостановки формирования новых блоков данных до момента освобождения буфера.

0Формула изобретения

Буферное запоминающее устройство, содержащее первый и второй блоки памяти, информационные входы которых объединены и являются информационными входами

5 устройства, первый и второй счетчики, выходы которых соединены соответственно с адресными входами первого и второго блоков памяти, первый, второй, третий и четвертый элементы И, элемент ИЛИ, первый и второй триггеры,- отличающееся тем, что, с

целью расширения функциональных возможностей устройства путем синхронизации моментов подготовки и сброса данных, в него введены мультиплексор, первый и вторые информационные входы которого соединены соответственно с выходами первого и второго блоков памяти, выходы мультиплексора являются информационными выходами устройства, первый, второй, третий, четвертый, пятый и шестой элементы И-ИЛИ-НЕ, первый, второй, третий, четвертый, пятый, шестой и седьмой элементы И-НЕ, первый, второй, третий, четвертый, пятый и шестой элементы НЕ, третий триггер, выходы первого и шестого элементов И-ИЛИ-НЕ соединены с входами синхронизации соответственно первого и второго триггеров, прямые выходы первого и второго триггеров соединены соответственно с первыми входами первого и второго элементов И-НЕ, выходы которых соединены с вторыми входами соответственно второго и первого элементов И-НЕ и с входами соответственно первого и второго элементов НЕ, первый вход третьего элемента И-НЕ соединен с третьим входом второго и четвертого элементов И-ИЛИ-НЕ с входом шестого элемента НЕ и является входом Конец чтения устройства, выход шестого элемента НЕ соединен с первым входом седьмого элемента И-НЕ и с входом установки в 1 третьего триггера, прямой выход которого соединен с первым входом третьего элемента И и вторым входом седьмого элемента И-НЕ, выход седьмого элемента И-НЕ соединен с первым входом четвертого элемента И-НЕ, выход третьего элемента И-НЕ соединен с вторым входом четвертого элемента И-НЕ и с входом третьего элемента НЕ, выход четвертого элемента И-НЕ соединен с вторым входом третьего элемента И-НЕ, первый вход первого элемента И- ИЛИ-НЕ соединен с первыми входами второго, четвертого и шестого элементов И-ИЛИ-НЕ и является входом Конец записи устройства, первый вход первого элемента И соединен с первыми входами второго элемента И, третьего и пятого элементов И-ИЛИ-НЕ и является входом синхронизации записи устройства, выход первого элемента НЕ соединен с вторыми

входами первого, второго, третьего элементов И-ИЛИ-НЕ и первого элемента И, выход второго элемента НЕ соединен с вторыми входами четвертого, пятого, шестого элементов И-ИЛИ-НЕ и второго элемента И, выход третьего элемента НЕ соединен с третьими входами первого и шестого элементов И-ИЛИ-НЕ, инверсный выход первого триггера соединен со своим

информационным входом и с первыми входами элемента ИЛИ, четвертого элемента И, пятого элемента И-НЕ и с четвертым входом шестого элемента И-ИЛИ-НЕ, инверсный выход второго триггера соединен со

своим информационным входом и с вторыми входами элемента ИЛИ, четвертого элемента И, первым входом шестого элемента И-НЕ и четвертым входом первого элемента И-ИЛИ-НЕ, вход синхронизации третьего триггера соединен с третьими входами третьего и пятого элементов И-ИЛИ-НЕ и является входом синхронизации чтения устройства, выходы пятого и шестого элементов И-НЕ соединены соответственно с

вторыми входами шестого и пятого элементов И-НЕ и с входами четвертого и пятого элементов НЕ, выход четвертого элемента НЕ соединен с четвертыми входами второго, третьего элементов И-ИЛИ-НЕ и с пятым входом первого элемента И-ИЛИ-НЕ, выход пятого элемента НЕ соединен с четвертыми входами четвертого, пятого элементов И-ИЛИ-НЕ, управляющим входом мультиплексора и с пятым входом шестого

элемента И-ИЛИ-НЕ, выходы первого и второго элементов И соединены с управляющими входами соответственно первого и второго блоков памяти, выходы второго и третьего элементов И-ИЛИ-НЕ соединены

соответственно с входом начальной установки и синхронизации первого счетчика, выходы четвертого и пятого элементов И- ИЛИ-НЕ соединены соответственно к входу начальной установки и синхронизации второго счетчика, выход элемента ИЛИ соединен с вторым входом третьего элемента И, выход которого соединен с информационным входом третьего триггера, выход четвертого элемента И является выходом

0 буферного устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство для блоков отображения информации | 1986 |

|

SU1411830A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1278980A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1280457A1 |

| Устройство для контроля блоков буферной памяти | 1987 |

|

SU1501175A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1444893A1 |

| Устройство для сопряжения процессоров | 1990 |

|

SU1807495A1 |

| Устройство для контроля программно-аппаратных средств эвм | 1987 |

|

SU1513454A1 |

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1376091A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287237A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании буферных запоминающих устройств систем сбора и обработки информации. Цель изобретения - расширение функциональных возможностей устройства. Устройство содержит блоки памяти, счетчики адреса обращения, мультиплексор, элементы И - ИЛИ - НЕ, схему приоритета заявок записи, реализованную на элементах И - НЕ и элементах НЕ, схему приоритета заявок на переключение режимов блоков памяти и блокировки переключения, реализованную на элементах И - НЕ и элементе НЕ, элемент ИЛИ, триггеры режимов, триггер состояния чтения буфера. Устройство позволяет организовать обмен данными между источником и приемником через систему сбора информации, работающую асинхронно с источником. 1 ил.

| Устройство для цифровой магнитной записи | 1985 |

|

SU1256087A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1278980A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-07-07—Публикация

1989-06-05—Подача