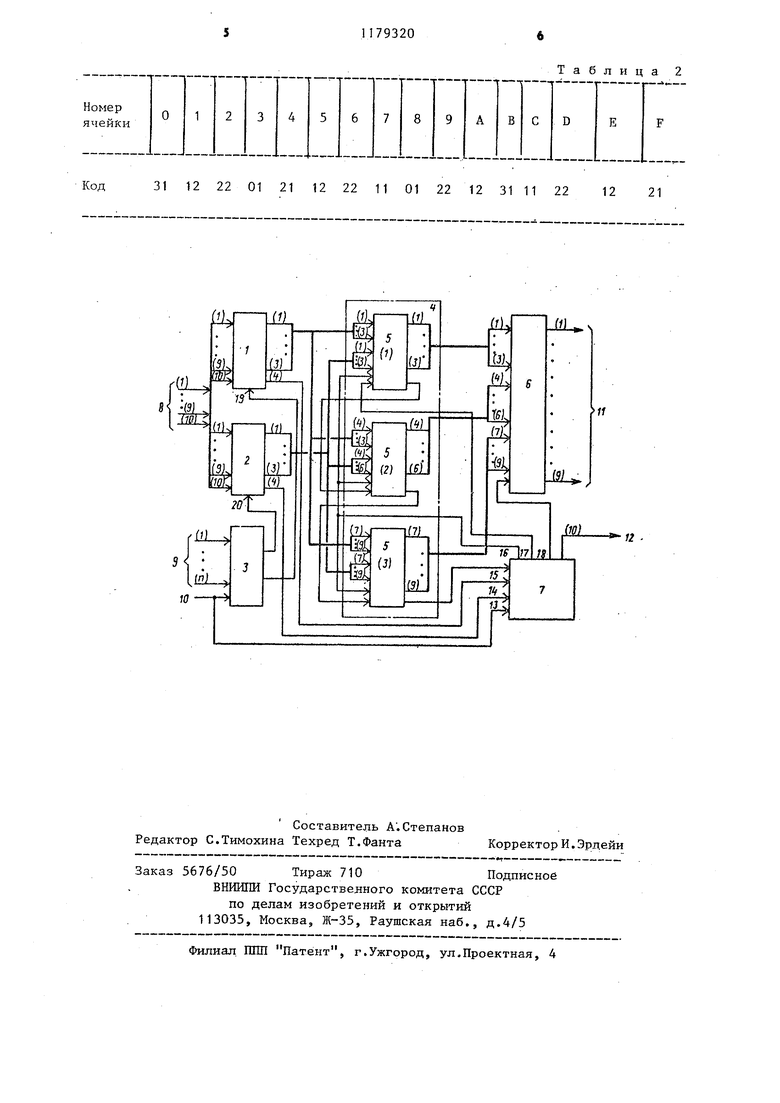

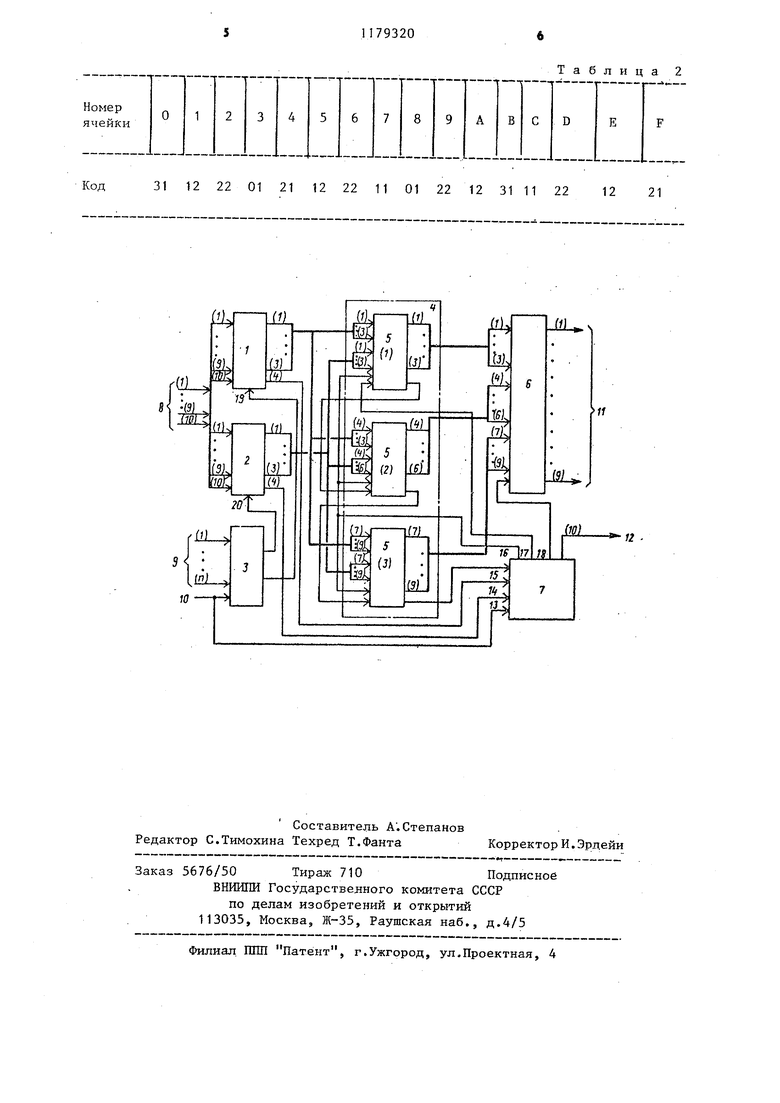

Изобретение относится к вычислительной технике и может быть использовано при обработке потока чисел, например, в интерполяторах и устройствах вычисления координат. Целью изобретения является повышение быстродействия устройства при обработке потока -чисел. На чертеже представлена структурная схема устройства для вычисления разности двух чисел для случая вычисления разности десятиразрядных чи сел, при-чем десятьш разряд- является знаковым. Устройство содержит регистры 1 и 2, дешифратор 3, сумматор 4, состоящий из трех одинаковых трехразрядных суммирующих блоков 5, преобразовател 6 прямого кода в дополнительный и блок 7 анализа знаков.. Устройство 1шеет входную шину 8, шину 9 номера Разряды адреса 8р - 7р Подаваемая веПеренос Код опер личина

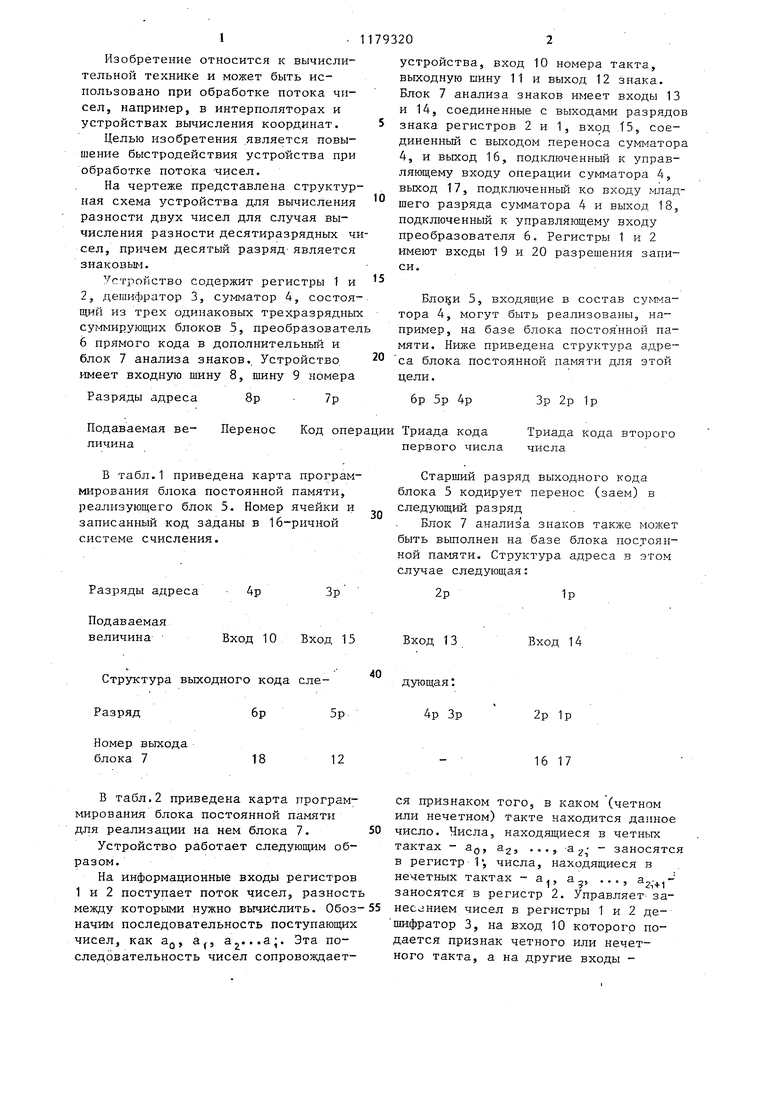

В табл.1 приведена карта программирования блока постоянной памяти, peaJшзyющeгo блок 5. Номер ячейки и записанный код заданы в 16-ричной системе счисления.

Зр

4р

Вход 10 Вход 15

Структура выходного кода слеРазряд6р 5р

Номер вьпсода

18

12 блока 7

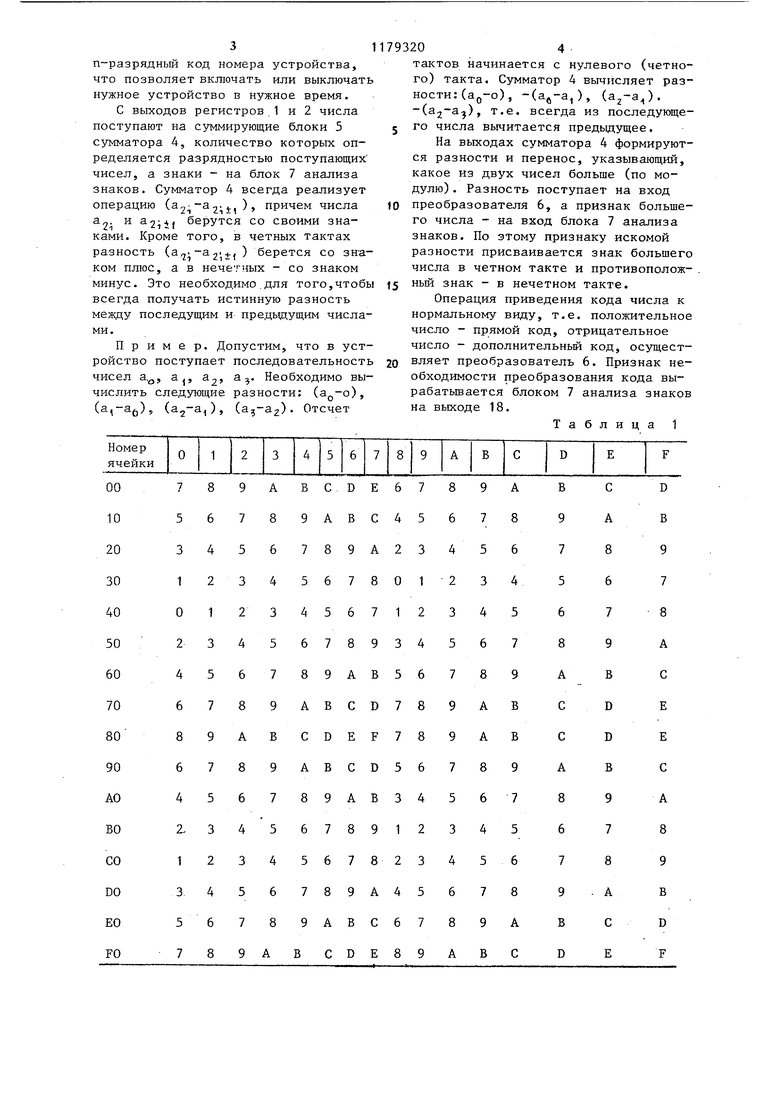

В табл.2 приведена карта программирования блока постоянной памяти для реализации на нем блока 7. 50

Устройство работает следующим образом.

На информационные входы регистров 1 и 2 поступает поток чисел, разность между которыми нужно вычислить. Обоз-55 начим последовательность поступающих

1...а;. Эта почисел, как а

f

о

следовательность чисел сопровождаетСтарший разряд выходного кода блока 5 кодирует перенос (заем) в следующий разряд

Блок 7 анализа знаков также может быть выполне на базе блока постоянной памяти. Структура адреса з этом случае следующая:

2р

1р

Вход 13

Вход 14

дующая: 4р Зр

2р 1р

16 17

ся признаком того, в каком (четном или нечетном) такте находится данное число. Числа, находящиеся в четных

тактах - а

о 2:

-а 2 заносятся

в регистр 1, числа, находящиеся в

нечетных тактах - а., а,,

а

-2-,1

заносятся в регистр 2. Управляет занесением чисел в регистры 1 и 2 дешифратор 3, на вход 10 которого подается признак четного или нечетного такта, а на другие входы устройства, вход 10 номера такта, выходную шину 11 и выход 12 знака. Блок 7 анализа знаков имеет входы 13 и 14, соединенные с выходами разрядов знака регистров 2 и 1, вход Т5, соединенньш с выходом переноса сумт 1атора 4, и выход 16, подключенный к управляющему входу операции сумматора 4, выход 17, подключенный ко входу младшего разряда сумматора 4 и выход 18, подключенный к управляющем входу преобразователя 6. Регистры 1 и 2 имеют входы 19 и 20 разрешения записи, Бло15И 5, входящие в состав сумматора 4, могут быть реализованы, например, на базе блока постоянной памяти. Ниже приведена структура адреса блока постоянной памяти для этой цели. 6р 5р 4р Зр 2р 1р Триада кода Триада кода второго первого числа числа

31

n-разрядный код номера устройства, что позволяет включать или выключать нужное устройство в нужное время.

С выходов регистров.1 и 2 числа поступают на суммирующие блоки 5 сумматора 4, количество которых определяется разрядностью поступающих чисел, а знаки - на блок 7 анализа знаков. Сумматор 4 всегда реализует операцию (21 причем числа а. и а2И1 берутся со своими знаками. Кроме того, в четных тактах разность (а,2-а2;+{ ) берется со знаком плюс, а в нечетных - со знаком минус. Это необходимо.для того,чтобы всегда получать истинную разность между последущим и предыдущим числами.

П р и м е р. Допустим, что в устройство поступает последовательность чисел а,д, а,, а2, а,. Необходимо вычислить следующие разности: (), (), (,), (). Отсчет

793204

тактов начинается с нулевого (четного) такта. Сумматор 4 вычисляет разности: (ад-о) , -(, ), (). -(), т.е. всегда из последующего числа вычитается предыдущее.

На выходах сумматора 4 формируются разности и перенос, указывающий, какое из двух чисел больше (по модулю) . Разность поступает на вход

to преобразователя 6, а признак большего числа - на вход блока 7 анализа знаков. По этому признаку искомой разности присваивается знак большего числа в четном такте и противоположный знак - в нечетном такте.

Операция приведения кода числа к нормальному виду, т.е. положительное число - прямой код, отрицательное число - дополнительньй код, осуществляет преобразователь 6. Признак необходимости преобразования кода вырабатьшается блоком 7 анализа знаков на выходе 18.

Таблица 1

Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО СИНТЕЗА, ПЕРЕДАЧИ, ПРИЕМА, АНАЛИЗА И ОЦЕНКИ МНОГОВАРИАНТНЫХ ПО ФОРМЕ, МНОГОПОЗИЦИОННЫХ И ЛОКАЛЬНЫХ ПО СПЕКТРУ СИГНАЛОВ | 2000 |

|

RU2160509C1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Арифметико-логическое устройство двухадресной ЦВМ | 1980 |

|

SU890390A1 |

| Устройство для поиска чисел в заданном диапазоне | 1981 |

|

SU993250A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Экстраполятор видеосигнала изображения | 1989 |

|

SU1718246A1 |

| Устройство для умножения чисел в непозиционной системе счисления | 1981 |

|

SU1015382A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| Устройство для поиска чисел в заданномдиАпАзОНЕ | 1979 |

|

SU822179A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ РАЗНОСТИ ДВУХ ЧИСЕЛ, содержащее первый и второй регистры, сумматор и блок анализа знаков, причем выходы разрядов регистров соединены с соответствующими разрядами соответственно первого и второго входов сумматора, вькоды разрядов знака первого и второго регистров соединены соответственно с первым и вторым входами блока анализа .знаков, выход переноса сумматора соединен с третьим входом блока анализа знаков, первый выход которого подключен к управляющему входу операции сумматора, а второй - к входу переноса младшего разряда сумматора, третий выход блока анализа знаков соединен с выходом знака устройства, отлич ающее С я тем, что, с целью повышения быстродействия при обработке потока чисел, устройство содержит дешифратор и преобразователь прямого кода в дополнительный, причем входы разрядов первого и второго регистров соединены с соответствукнцими разрядами входной шины устройства, входы разрешения записи первого и второго регистров соединены с соответствующими выходами дешифратора, первый I вход которого соединен с входом номера такта устройства, а остальные (Л входы соединены с шиной номера устройства, выходы разрядов сумматора соединены с входами разрядов преобразователя прямого кода в дополнительный, управляющий вход которого соединен с четвертым выходом блока анализа знаков, четвертый вход коточ рого соединен с входом номера такта устройства, выходы разрядов преобсо О9 разователя прямого кода в дополнительный соединены с соответствующиt d ми разрядами выходной шины устройства.

| Патент США № 3424898, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление к индикатору для определения момента вспышки в двигателях | 1925 |

|

SU1969A1 |

| Карцев М.А | |||

| Арифметика цифровых машин | |||

| М.: Наука, 1969, с | |||

| ДИФФЕРЕНЦИАЛЬНАЯ ТЕРМИОННАЯ ЛАМПА | 1920 |

|

SU294A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-09-15—Публикация

1984-01-19—Подача