равления содержит усилитель, элемент И, коммутатор и последовательно соединенные тумблерный регистр, дешифратор, второй вход которого соединен с первым выходом коммутатора, и элемент ИЛИ, второй вход которого соединен с вторым выходом коммутатора, первый вход которого соединен с вторым выходом тумблерного регистра, третий выход которого подключен к первому входу элемента И, выход которого подключен к второму входу коммутатора, третий вход которого объединен с входом усилителя и является первым входом блока управления, вторым входом, а также первым, вторым и третьим выходами которого являются соответственно второй вход элемента И, третий выход коммутатора, выход элемента ИЛИ и выход усилителя.

3. Устройство по п. 1, отличающееся тем, что блок сравнения содерлсит первый элемент ИЛИ,

последовательно соединенные первый инвертор, первый сумматор по модулю два, первый элемент И и второй элемент ИЛИ, последовательно соединенные второй инвертор, второй сумматор по модулю два и второй элемент И, второй вход и выход которого соединены соответственно с выходом первого элемента ИЛИ и вторым входом второго элемента ИЛИ, выходы первого и второго элементов И и выход второго элемента ИЛИ являются соответственно первым, вторым и третьим выходами блока сравнения, первым, вторым, третьим, четвертым, пятым и шестым входами которого являются соответственно вход первого инвертора, объединенные вторые входы первог и второго сумматоров по модулю два, первый и второй входы первого элемента ИЛИ, второй вход первого элемента И и вход второго инвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи и анализа циклограмм дискретных блоков | 1985 |

|

SU1313221A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Программируемое устройство для контроля цифровых систем | 1986 |

|

SU1439588A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для контроля логических блоков | 1983 |

|

SU1101825A1 |

| Устройство для контроля качества ферромагнитных изделий | 1987 |

|

SU1499212A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для сбора данных о загрузке узлов электронной вычислительной машины | 1975 |

|

SU532102A1 |

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| Устройство для отладки и контроля программ | 1988 |

|

SU1509907A1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ, содержащее блок управления, последовательно соединенные блок сравнения и первый блок индикации, второй вход которого соединен с вторым выходом блока сравнения, блок памяти, управляю1щй вход и первый выход которого соединены соответственно с первым выходом блока управления и первым входом блока сравнения, второй блок индикации, коммутатор, выход которого является информационным входом контролируемого логического блока, информационным выходом которого является второй вход блока сравнения, отличающееся тем, что, с целью сокращения времени контроля, в него введены генератор тактовых импульсов, третий и четвертый блоки индикации, формирователь кодов операций, формирователь сигналов переключений, а блок памяти вьтолнен в виде регистра адреса, регистра кода состояния, регистра информации и регистра управления, выход генератора тактовых импульсов подключен к первому входу блока управления, второй вход и второй выход которого соединены соответственно с третьим выходом блока сравнения и входом формирователя кодов операций, первый выход которого подключен к входу второго блока индикации, второй выход соединен с входом формирователя сигналов переключений и управляющим входом контролируемого логического блока, первый выход формирователя сигналов переключений соединен с третьим входом блока сравнения и первым входом коммутатора, второй выход соединён с четвертым входом блока сравнения и вторым входом коммутатора, третий выход формирователя сигналов переклю(Л чений соединен с пятым входом блока сравнений, шестой вход которого соединен с выходом коммутатора, третий выход блока управления подключен к входу синхронизации контролируемого логического блока, информационый выход которого подключен к входу 00 четвертого блока индикации, выход о регистра кода состояния является перСХ) вым выходом блока памяти и соединен ;о с первым входом третьего блока индика00 ции, второй вход которого соединен с адресным входом контролируемого логического блока и вторым выходом блока памяти, которым является выход регистра адреса, выходы регистра информации и регистра управления являются соответственно третьим и четвертым выходами блока памяти и соединены соответственно с третьими и четвертыми входами третьего блока индикации и коммутатора . 2. Устройство по п. 1, отличающееся тем, что блок уп

1

Изобретение относится к радиотехнике и может использоваться при проектировании и отработке макетных и опытных образцов логических блоков.

Цель изобретения - сокращение времени контроля.

На фиг. 1 представлена структурная электрическая схема предложенного устройства; на фиг. 2 - блок управления; на фиг. 3 - блок сравнения на фиг.4 - формирователь сигналов переключений; на фиг. 5 - коммутатор

Устройство для контроля логически блоков содержит формирователь 1 сигналов переключений, блок 2 управления, блок 3 сравнения, первый 4, второй 5, третий 6 и четвертый 7 блоки индикации, коммутатор 8, генератор 9 тактовых импульсов, формирователь 10 кодов операций, блок 11 памяти, состоящийиз регистра 12 .адреса, регистра 13 кода состояния, регистра 14 информации, регистра Т5 управления и логический блок 16.

Блок управления 2 содержит усилиталь 17, элемент И 18,, коммутатор

19, элемент ИЛИ 20, дешифратор 21 и тумблерный регистр 22.

Блок 3 сравнения соде ржит первый 23 и второй 24 элементы ИЛИ, первый 25 и второй 26 элементы И, первый 27 и второй 28 сумматоры по модулю два, первый 29 и второй 30 инверторы.

Формирователь 1 сигналов переключений содержит первый 31, второй 32 и третий 33 дешифраторы.

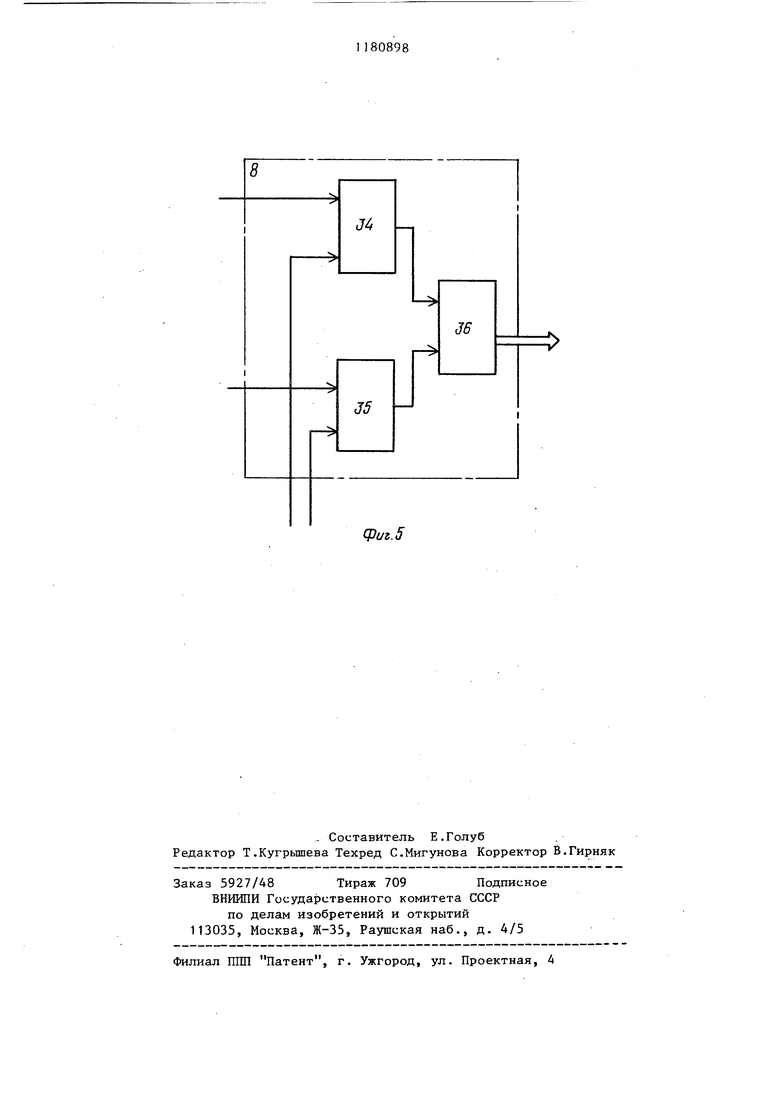

Коммутатор 8 содержит первый 34 и второй 35 элементы И и элемент ИЛИ 36.

Предложенное устройство для контрля логических блоков имеет три режима работы: автоматический, пошаговый и режим принудительной установки кодов операций.

В автоматическом режиме устройств работает следующим образом.

Формирователь 10 кодов операций под воздействием тактовых импульсов поступающих на его вход от генератор 9 тактовых импульсов через коммутатор 19 и элемент ШШ 20 блока 2

3

управления, формирует циклическую последовательность кодов операций к торые поступают в Отрабатываемый образец контролируемого логического блока 16 и на входы дешифраторов 31 - 33 формирователя 1 сигналов переключений.

В зависимости от вида кода операции происходит его распознавание одним из дешифраторов 31, 32 или 33 формирователя 1 сигналов переключения, с выхода которого сигнал переключения поступает либо на вторые входы первого элемента ИЛИ 23 блока 3 сравнения и элемента И 34 коммутатора 8, либо на первый вход первого элемента ИЛИ 23 и на второй вход элемента И 35, либо на второй вход первого элемента И 25.

По сигналу переключения происходит подключение выхода регистра 14 информации или регистра 15 управления блока 11 памяти через первый и второй элементы И 34 или 35 коммутатора 8 к входу контролируемого логического блока 16 и по его выходу к входу второго инвертора 30 блока 3 сравнения. Одновременно с этим происходит подключение выхода одного из сумматоров по модулю два 27 или 28 к входу второго элемента ИЛИ 24 и первому блоку 4 индикации. Код реакции контролируемого логического блока 16 на выданное воздействие поступает на четвертый блок 7 индикации и на вторые входыпервогои второго сумматоров по модулю два 27 и 28 блока 3 сравнения на первые входы которых через пер- вый и второй инверторы 29 и 30 поступают коды эталонов (информационные части тестовых воздействий) с выходов регистра 13 кода состояния, регистра 14 информации и регис ра 15 управления блока 11 памяти. Результаты суммирования кодов эталонов с кодами реакции с выходов первого и второго сумматоров по модулю два 27 и 28 поступают на первые входы первого и второго элементов И 25 и 26. С выхода того же элемента И, на первый вход которого в данный момент поступает сигнал переключения с одного из дешифраторов 31 - 33, результат сравнения поступает на вход второго элемента НИИ 24 и на вход первого блока 4 индикации.

808984

Учитывая то, что выдача информационной части воздействия на контролируемый логический блок 16 и подключение выхода первого или второго 5 сумматора по модулю два 27 и 28

к входу второго элемента ИЛИ 24 происходит под воздействием одного и того же сигнала переключения, а реакция контролируемого логическо0 го блока 16 не имеет запаздывания по времени относительно момента выдачи воздействия, с выхода второго элемента ИЛИ 24 на вход элемента И 18 блока 2 управления поступает 5 сигнал результата сравнения кода реакции контролируемого логического блока 16 с кодом эталона того сигнала, который был выдан в качестве информационной части воздействия, 20. или с эталоном кода состояния, хранящимся в регистре 13 кода состояния блока 11 памяти

Если на тумблерном регистре 22 блока 2 управления не установлен признак блокировки результата сравнения кода реакции с эталоном, то сигнал результата сравнения с вькода элемента И 18 поступает на коммутатор 19. При положительном результате

30 сравнения коммутатор 19 пропускает очередной тактовый импульс от генератора 9 через элемент ИЛИ 20 на вход формирователя 10 кодов операций, который формирует очередной код опера5 ции в циклической последовательности кодов.

При отрицательном результате сравнения сигнал с выхода второго элемента ИЛИ 24 блокирует прохождение

0 тактовых импульсов через коммутатор 19 на вход формирователя 10 кодов операций. При этом на соответствующем входе контролируемого логического блока 16 формируется тот код

5 операции, при котором произошло не- сравнение реакции с эталоном. Первый блок 4 индикации указывает местонахождение эталона, с которым произошло несравнение кода реакции, второй,

0 третий и четвертый блоки 5 - 7 индикации отображают соответственно состояния кода операции, регистра 12 адреса, регистра 13 кода состояния, регистра 14 информации, регистра 15

5 управления и кода реакции.в момент несравнения. Это позволяет разработчику достоверно и быстро определить ситуацию, при которой произошло нарушение алгоритма обмена информацией между предложенным устройством и контролируемым логическим блоком 16.

Повторный запуск устройства производится сигналом с второго выхода тумблерного регистра 22 при нажатии на нем соответствующей кнопки.

Пошаговый режим работы отличается от автоматического тем, что тактовые импульсы, поступающие с третьего выхода блока 2 управления на формирователь 10 кодов операций, выдаются не генератором 9 тактовых импульсов а оператором вручную путем нажатия К110ПКЛ на тумблерном регистре 22 блока 2 управления. Для этого на тумблерном регистре 22 устанавливается признак пошагового режима, при

котором коммутатор 19 запрещает про

хождение тактовых импульсов от генератора 9 тактовых импульсов и разрешает прохождение единичных тактовых импульсов с тумблерного регистра 22 на вход элемента ИЛИ 20 и далее на вход формирователя 10 кодов операций.

Режим принудительной установки кодов операций характеризуется тем, что формирователь 10 кодов операций производит периодическую с частотой следования тактовых импульсов выдачу одного и того же выбранного оператором кода операции.

В этом режиме оператор устанавливает на тумблерном регистре 22 признак пошагового режима и признак кода, который должен быть сформирован . Коммутатор 19 запрещает прохождение тактовых импульсов от генератора 9 на вход элемента ИЛИ 20 и ра.зрешает их поступление на второй вход дешифратора 21, на первый вход которого подается признак кода с выхода тумблерного регистра 22.

С выхода дешифратора 21 признак кода и тактовые импульсы поступают на первый вход элемента ИЛИ 20, с выхода которого они подаются на

вход формирователя 10 кодов операций, формирующего заданный код с частотой тактовых импульсов.

Режим принудительной установки кодов операций необходим в случае локализации неисправности путем ис;ледования трактов прохождения управляющей части воздействия с помощью, например, осциллографа.

0 Кроме того, в этом режиме возможно исследование реакции контролируемого логического блока 16 на каждое изменение информационной части воздействия, которое задается разра5ботчиком путем внесения различных кодовых комбинаций в соответствующий регистр блока 11 памяти.

Во всех указанных режимах работы разработчик имеет возможность

0 запретить выдачу сигнала несравнения с выхода второго элемента ИЛИ 24 блока 3 сравнения на вход коммутатора 19 путем выдачи сигнала запрета на первый вход элемента И 18.

5

Выдача сигнала запрета достигается установкой на тумблерном регистре 22 признака блокировки результата сравнения реакции контролируемого логического блока 16 с этало0ном, хранящимся в регистрах блока 11 памяти. .

Во всех режимах работы предложенного устройства, тактовые импульсы с выхода генератора 9 тактовых им5пульсов через усилитель 17 блока 2 управления поступают на вход синхронизации контролируемого логического блока 16 для синхронизации работы его узлов.

0

Кроме того, во всех режимах работы предложенного устройства разработчик имеет возможность с тумблерного регистра 22 и коммутатора 19 задать отрабатываемому образцу контролируемого логического блока 16 режим ввода или вывода информации, необходимый для диагностики его вводно-выводных трактов.

и

О

12

U

/J

/4

W

/J

-N V

31

зг

JJ

Фиг.

J6

cpuz.5

| Устройство для контроля оконечных блоков системы передачи данных | 1978 |

|

SU750748A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для контроля логических блоков | 1978 |

|

SU734694A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-23—Публикация

1984-04-21—Подача