Изойретение относится к цифровой вычислительной технике и может быть использовано в микропроцессорных системах управления и обработки данных..5

Цель изобретения - увеличение пропускной способности устройства,

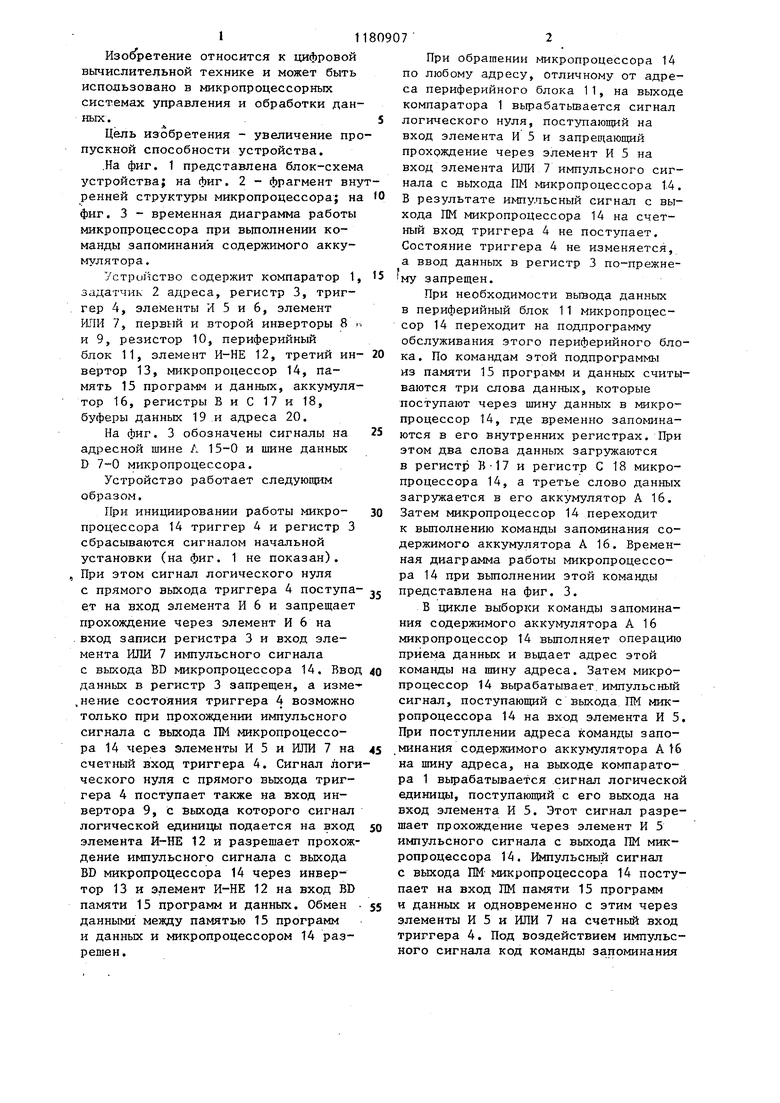

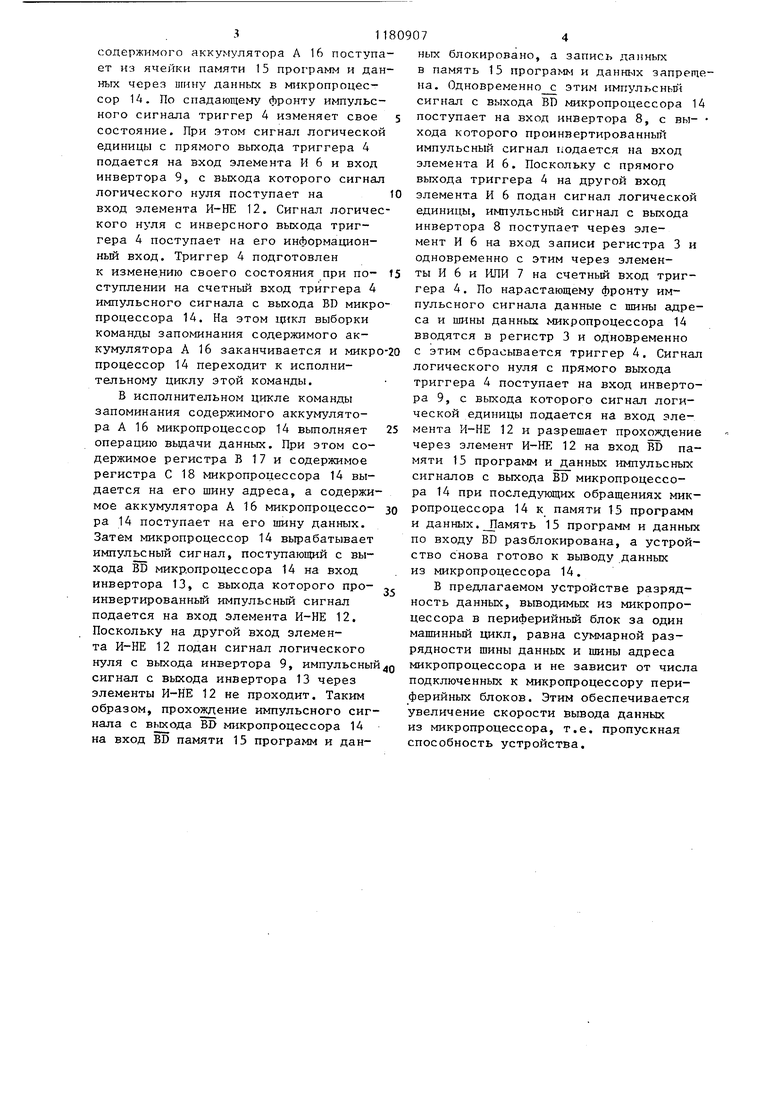

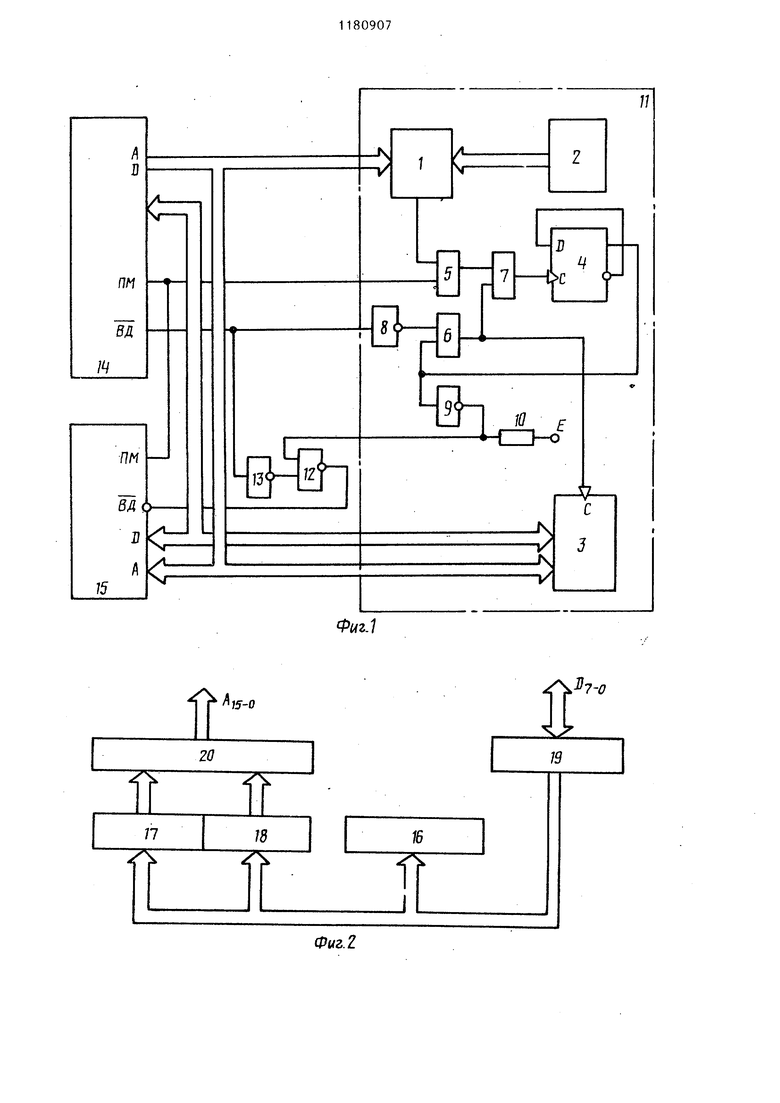

.На фиг. 1 представлена блок-схема устройства; на фиг. 2 - фрагмент внутренней структуры микропроцессора; на О фиг. 3 - временная диаграмма работы микропроцессора при вьтолнении команды запоминания содержимого аккумулятора .

Устрийство содержит компаратор 1, 5 задатчик 2 адреса, регистр 3, триггер 4, элементы И 5 и 6, элемент ИЛИ 7, nepBtm и второй инверторы 8 j, и 9, резистор 10, периферийный блок 11, элемент Pi-HE 12, третий ин- 20 вертор 13, микропроцессор 14, память 15 программ и данных, аккумулятор 16, регистры В и С 17 и 18, буферы данных 19 и адреса 20.

На фиг. 3 обозначены сигналы на 25 адресной шине А 15-0 и шине данных D 7-0 микропроцессора.

Устройство работает следующим образом.

При инициировании работы микро- ЗО процессора 14 триггер 4 и регистр 3 сбрасываются сигналом начальной установки (на фиг. 1 не показан). При этом сигнал логического нуля с прямого выхода триггера 4 поступает на вход элемента И 6 и запрещает прохождение через элемент И 6 на вход записи регистра 3 и вход элемента ИЛИ 7 иьтульсного сигнала с выхода BD микропроцессора 14. Ввод 40 данных в регистр 3 запрещен, а изме.нение состояния триггера 4 возможно только при прохождении импульсного сигнала с выхода ПМ микропроцессора 14 через элементы И 5 и ИЛИ 7 на 45 счетный вход триггера 4. Сигнал логического нуля с прямого выхода триггера 4 поступает также на вход инвертора 9, с выхода которого сигнал логической единицы подается на вход 50 элемента И-НЕ 12 и разрешает прохождение импульсного сигнала с выхода BD микропроцессора 14 через инвертор 13 и элемент И-НЕ 12 на вход BD памяти 15 программ и данных. Обмен 55 данньши между памятью 15 программ и данных и микропроцессором 14 разрешен.

При обращении микропроцессора 14 по любому адресу, отличному от адреса периферийного блока 11, на выходе компаратора 1 вьфабатьшается сигнал логического нуля, поступающий на вход элемента И 5 и запрещающий прохождение через элемент И 5 на вход элемента ИЛИ 7 импульсного сигнала с выхода ПМ микропроцессора 14. В результате импульсный сигнал с выхода ПМ микропроцессора 14 на счетный вход триггера 4 не поступает. Состояние триггера 4 не изменяется, а ввод данных в регистр 3 по-прежнему запрещен.

При необходимости вывода данных в периферийный блок 11 микропроцессор 14 переходит на подпрограмму обслуживания этого периферийного блока. По командам этой подпрограммы из памяти 15 программ и данных считываются три слова данных, которые поступают через шину данных в микропроцессор 14, где временно запоминаются в его внутренних регистрах. При этом два слова данных загружаются в регистр В-17 и регистр С 18 микропроцессора 14, а третье слово данных загружается в его аккумулятор А 16. Затем микропроцессор 14 переходит к выполнению команды запоминания содержимого аккумулятора А 16. Временная диаграмма работы микропроцессора 14 при выполнении этой команды представлена на фиг. 3.

В цикле выборки команды запоминания содержимого аккумулятора А 16 микропроцессор 14 выполняет операцию приема данных и выдает адрес этой команды на шину адреса. Затем микропроцессор 14 вырабатывает, импульсный сигнал, поступающий с выхода ПМ микропроцессора 14 на вход элемента И 5 При поступлении адреса команды запоминания содержимого аккумулятора А 16 на шину адреса, на выходе компаратора 1 вырабатывается сигнал логической единицы, поступающий с его выхода на вход элемента И 5. Этот сигнал разрешает прохождение через элемент И 5 импульсного сигнала с выхода ПМ микропроцессора 14. Импульсный сигнал с выхода ИМ микропроцессора 14 поступает на вход ИМ памяти 15 программ и данных и одновременно с этим через элементы И 5 и ИЛИ 7 на счетный вход триггера 4. Под воздействием импульсного сигнала код команды запоминания содержимого акку 1улятора А 16 поступ ет нз ячейки памяти 15 программ и да ных через игину данных в микропроцессор 14. По спадающему фронту импульс ного сигнала триггер 4 изменяет свое состояние. При этом сигнал логическо единицы с прямого выхода триггера 4 подается на вход элемента И 6 и вход инвертора 9, с выхода которого сигна логического нуля поступает на вход элемента И-НЕ 12. Сигнал логиче кого нуля с инверсного выхода триггера 4 поступает на его информационный вход. Триггер 4 подготовлен к изменению своего состояния при поступлении на счетный вход триггера 4 импульсного сигнала с выхода BD микр процессора 14. На этом цикл выборки команды запоминания содержимого аккумулятора А 16 заканчивается и микр процессор 14 переходит к исполнительному циклу этой команды. В исполнительном цикле команды запоминания содержимого аккумулятора А 16 микропроцессор 14 вьтолняет операцию вьщачи данных. При этом содержимое регистра В 17 и содержимое регистра С 18 микропроцессора 14 выдается на его шину адреса, а содержи мое аккумулятора А 16 микропроцессора 14 поступает на его шину данных. Затем микропроцессор 14 вырабатывает импульсный сигнал, поступающий с выхода BD микр.опроцессора 14 на вход инвертора 13, с выхода которого проинвертированный импульсный сигнал подается на вход элемента И-НЕ 12. Поскольку на другой вход элемента И-НЕ 12 подан сигнал логического нуля с выхода инвертора 9, импульсны сигнал с выхода инвертора 13 через элементы И-НЕ 12 не проходит. Таким образом, прохождение импульсного сиг нала с выхода В1 микропроцессора 14 на вход BD памяти 15 программ и данных блокировано, а запись данных в память 15 программ и данных запрещена. Одновременно с этим импульсньй сигнал с выхода BD микропроцессора 14 поступает на вход инвертора 8, с вы- хода которого проннвертированный импульсный сигнал подается на вход элемента И 6. Поскольку с прямого выхода триггера 4 на другой вход элемента И 6 подан сигнал логической единицы, импульсный сигнал с выхода инвертора 8 поступает через элемент И б на вход записи регистра 3 и одновременно с этим через элементы И 6 и ИЛИ 7 на счетный вход триггера 4. По нарастающему фронту импульсного сигнала данные с шины адреса и шины данных микропроцессора 14 вводятся в регистр 3 и одновременно с этим сбрасывается триггер 4. Сигнал логического нуля с прямого выхода триггера 4 поступает на вход инвертора 9, с выхода которого сигнал логической единицы подается на вход элемента И-НЕ 12 и разрешает прохождение через элемент И-НЕ 12 на вход BD памяти 15 программ и д анных импульсных сигналов с выхода BD микропроцессора 14 при последующих обращениях микропроцессора 14 к памяти 15 программ и данных.Память 15 программ и данных по входу BD разблокирована, а устройство снова готово к выводу данных из микропроцессора 14. В предлагаемом устройстве разрядность данных, выводимых из микропроцессора в периферийный блок за один машинный цикл, равна суммарной разрядности шины данных и шины адреса микропроцессора и не зависит от числа подключенных к микропроцессору периферийных блоков. Этим обеспечивается увеличение скорости вывода данных из микропроцессора, т.е. пропускная способность устройства.

fj

V

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Устройство для ввода информации | 1991 |

|

SU1800452A1 |

| Устройство для отладки и контроля хода программ | 1989 |

|

SU1691843A2 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Устройство для адресации памяти | 1987 |

|

SU1442990A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

УСТРОЙСТВО ДЛЯ ВЫВОДА ИНФОРМАЦИИ, содержащее компаратор, задатчик адреса, первый элемент И, первый инвертор и регистр, входы первой группы которого являются информационными входами первой группы устройства, вход первого инвертора является первым управляющим входом устройства, выход подключен к первому входу первого элемента И, выход которого соединен со стробирующим входом регистра, выход задатчика адреса соединен с первым входом компаратора, о т л ичающееся тем, что, с целью повьшения пропускной способности устройства, в него введены второй и третий инверторы, элемент ИЛИ, второй элемент И, элемент И-НЕ и триггер, первый вход BTopoio элемента И является вторым управляющим входом устройства, второй вход второго эле мента И соединен с выходом компаратора, второй вход которого является адресным входом устройства, входы второй группы регистра являются информационными входами второй группы устройства, выходы первого и второго элементов И соединены с соответствующими входами элемента ИЛИ, выход которого подключен к синхровходу триггера, вход данных которого соединен с его инвертирующим выходом, неинвертирующий выход триггера подключен к второму входу первого элемента И и через второй инвертор - к первому входу элемента И-НЕ, второй вход которого соединен с выходом третьего инвертора, а выход является выходом 00 устройства, вход третьего инвертора О является первым управляющим входом со устройства.

/Ч,5-о 20

тт

ю

л

18 TV

Т

Фиг. г

16

U,uKf вы5арки команды

Исполните/ ьныи цикл

| СОЕДИНЕНИЕ ПЕРЕХОДНОГО МЕТАЛЛА ДЛЯ КАТАЛИЗАТОРА ПОЛИМЕРИЗАЦИИ ОЛЕФИНОВ И КАТАЛИЗАТОР ПОЛИМЕРИЗАЦИИ ОЛЕФИНОВ, СОДЕРЖАЩИЙ СОЕДИНЕНИЕ ПЕРЕХОДНОГО МЕТАЛЛА | 2019 |

|

RU2756890C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Патент CiilA № 4144562, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

Авторы

Даты

1985-09-23—Публикация

1984-04-13—Подача